AN-835:高速A/D コンバータ(ADC)のテストと評価について

範囲

本書では、高速ADC を評価するためにアナログ・デバイセズの高速コンバータ・グループで使用する特性評価と製品テストの方法について説明します。このアプリケーション・ノートは参考資料として利用できますが、製品データシートに代わるものではありません。

動的テストのハードウェア・セットアップ

S/N 比、SINAD、最大スプリアス、IMD は、図1 に示すようなハードウェア・セットアップを使用してテストされます。製品テストではテスト・ハードウェアは高集積化されていますが、ハードウェアの原理は同じです。動的テスト用の基本セットアップには、信号発生器、バンドパス・フィルタ、テスト用治具、低ノイズ電源、エンコード・ソース(通常は評価用ボード上に集積されています)、データ・アクイジション・モジュール、データ解析ソフトウェアが含まれます。アナログ・デバイセズではベンチ評価を支援するために、アプリケーション・ハードウェアとソフトウェアを提供しています。

図1. 代表的な特性テストのセットアップ

HSC-ADC-EVALC 評価用プラットフォーム

高速ADC FIFO 評価用キット(HSC_ADC_EVALC)は、アナログ・デバイセズの高速ADC 評価用ボード、VisualAnalog®、およびSPIController ソフトウェアからデジタル・データをブロックでキャプチャするためのFPGA ベースのバッファ・メモリ・ボードを搭載しています。HSC-ADC-EVALC 評価用プラットフォームの詳細については、www.analog.com/FIFO を参照してください。

図2. 代表的なHSC-ADC-EVALC 評価用プラットフォーム

FPGA ベースのバッファ・メモリ・ボードは、標準的なUSB ケーブルでパソコンに接続でき、VisualAnalog およびSPIController ソフトウェアと併用すると、高速ADC の性能評価を迅速に実行できます。ユーザは、個々のADC製品に固有のSPI レジスタの設定値の変更、特定のアナログ入力とサンプル・レートのFFT の表示、SNR、SINAD、SFDR、高調波情報、更にゲインやオフセットなどの時間領域情報の分析ができます。HSC-ADC-EVALCは、CMOS、LVDS、およびCML 出力をサポートしています。ボードによっては、インターポーザまたはわずかに異なるFIFOの代替手段が必要になる場合があります。追加または別のハードウェアが必要な場合は、製品データシートに記載いたします。HSC-ADC-EVALC、SPIController、およびVisualAnalog ソフトウェアの動作の詳細については、www.analog.com/FIFO を参照してください。

背景

図3. HSC-ADC-EVALC:FPGA ベースのデータ・キャプチャ・ボード

図4. VisualAnalog:FFT と時間領域の性能プロットを表示する代表的な画面

アナログ信号源

通常、動的試験では、Rohde & Schwarz SMA/SMHU/SMG/SMGU、Agilent 8644 信号発生器、Wenzel 水晶発振器またはValpey Fisher水晶発振器を使用します。これらの信号源は、数kHz~数GHzの周波数に対して優れた性能(低位相ノイズ、平坦な周波数応答、妥当な高調波性能)を提供することが実証されています。これらの信号発生器の高調波性能は一般にADC の固有直線性ほどには優れていないため、ADC へのアナログ入力と信号発生器との間にフィルタ処理を追加する必要があります。

アナログ信号フィルタ

デバイス・テストには、固定周波数と可変周波数の2 つのバンドパス・フィルタを使用します。一般に固定周波数フィルタは可変フィルタよりも小型であり、性能は若干優れています。可変フィルタは、1 つのフィルタを使用して広範囲の周波数でテストできます。K&L Microwave、TTE、Allen Avionics など、数社のフィルタ・メーカーがADC テスト向けに優れたフィルタを提供しています。

ADC テストには、一般にローパス・フィルタとバンドパス・フィルタという2 種類のフィルタが使用されます。これらは個々に使用したり、アプリケーションに必要な性能レベルを得るために組み合わせて使用したりできます。

ADC に広範囲のアナログ周波数を印加する必要がある場合は、ローパス・フィルタを推奨します。しかし、ローパス・フィルタでは信号発生器からADC にノイズが入ってしまいます。このノイズにより、測定されるADC の性能レベルが低下することもあります。代表的なローパス・フィルタはTTE のJ97 です。通常、ローパス・フィルタにはパス・バンドの終了とストップ・バンドの開始を定義する遷移帯域があります。この仕様と共に、サポートされるストップ・バンド減衰量が仕様規定されます。J97 の場合、遷移帯域は3dB 周波数の1.0~1.2 倍と定義され、サポートされるストップ・バンド減衰量は80dB です。3dB 周波数の1.2 倍を超えるエネルギーは、少なくとも80dB 減衰します。

アナログ周波数が固定されて変更されない場合は、バンドパス・フィルタが使用されます。バンドパス・フィルタでは、信号源によって生成されたワイドバンド・ノイズの多くが除去されるので、一般にはADC テスト用に最高の性能が提供されます。TTE のQ70T シリーズなどのフィルタには、中心周波数のパーセンテージで定義される帯域幅があります。この帯域幅が狭いほど、フィルタを通過するノイズが減少します。しかし、アナログ周波数は更に制限され、大きな挿入損失があります。中心周波数を選択すると、帯域幅を決定できます。理想的には5~6%の帯域幅を選択してください。ただし、優れたノイズ性能はアナログ周波数の柔軟性とトレードオフの関係にあることを念頭に置いてください。ローパス・フィルタの場合と同様、バンドパス・フィルタには3dB 周波数(中心周波数の上下)とサポートされるストップ・バンド性能の周波数との間の形状を定義する遷移帯域があります。TTE のQ70T では、ストップ・バンド減衰量は60dB です。

図5.TTE J97 の代表的な性能

図6.TTE Q70T の代表的なバンドパス性能

前述のように、バンドパス・フィルタのストップ・バンド減衰量が60dB しかない場合があります。この場合、ストップ・バンドの領域に入る信号は60dB 除去されます。例えば、基本波よりも25dB 下の高調波を持つ信号源の場合、高調波の実効的なレベルはQ70T フィルタの後では−85dBc となります。多くの高性能ADC では、これでは不十分です。−100dBc 以上の性能が必要な場合は、バンドパス・フィルタとローパス・フィルタをカスケード接続するのが一般的です。バンドパス・フィルタの後に接続するローパス・フィルタを選択する際は、バンドパス・フィルタを通過する高調波がローパス・フィルタのストップ・バンド性能によって最も適切にフィルタリングされるようにローパス周波数を選択します。J97 ローパス・フィルタでは、ストップ・バンド減衰量には3dB 周波数の1.2 倍で到達します。バンドパス・フィルタの2 次高調波がローパス3dB 周波数の1.4倍に設定されている場合、バンドパス・フィルタを通過するすべての高調波がフィルタリングされ、ローパス・フィルタの追加の挿入損失は必要なパス・バンドのレベルを大幅に減らさないことが確実に実現されます。この場合、ローパス周波数はバンドパス周波数の1.4倍となり、カスケード接続された減衰量は理論上約140dB となります。実際はカップリング効果や放射効果があるためこの値を実現することは困難ですが、これは有用な技術であり、−100dBc をはるかに超える高調波減衰量を達成できます。

0.5dB~3dB の減衰器は、直列のバンドパスとローパスの間に配置できることにも注目してください。これにより、公称50Ω に仕様規定されている2 つのフィルタ間の整合性の向上にも役立ちます。

フィルタを指定する際は、飽和を防止するために大きなコアを使用したフィルタを推奨します。一般にフィルタは約+15dBmの入力パワーに対して設計されます。しかし多くの場合、ADCの駆動条件はこの値をはるかに上回るため、コアの飽和と歪みを引き起こします。大きなコアを指定すると、コア飽和によるスプリアス歪みが減少します。最後に、フィルタ・コネクタも指定できます。アダプタを使用すればコネクタ・タイプ間の変換は可能ですが、それに伴うミスマッチがコンバータ性能に微妙な影響を与えることがあります。これは8 ビットや10 ビットのコンバータでは問題になりませんが、12、14、16 ビットのコンバータでは非常に目立ちます。

信号のエンコード・ソース

高性能のコンバータを実現するには、一般にストック信号発生器ではエンコード・ソースとして不十分です。なぜなら、近接位相ノイズとワイドバンド位相ノイズがあるためです。エンコード・ソースには、一般に固定周波数発振器が使用されます。Wenzel およびTechtrol Cyclonetics(TCI)製の高性能水晶発振器を使用できます。WenzelのSprinterおよびUltra Low Noiseシリーズは、最適な位相ノイズ性能を実現できます。高品質エンコード・ソースのもう1 つの供給元はValpey Fisher で、差動PECLやVCXO など、いくつかのオプションを提供します。要求がそれほど厳しくないアプリケーションでは、さまざまなメーカーから提供される標準的なCMOS クロック・モジュールを使用できます。クロックを外部リファレンスと同期させる必要があるエンド・アプリケーションでは、AD9516-0 のような製品にある、PLL ループのVCXO を使用できます。

図7. 代表的な低価格CMOS クロック発振器

ADCの設計ごとに、適切なクロック発振器を使用することが非常に重要です。適切なクロックの選択方法は、アナログ・デバイセズのアプリケーション・ノートAN-501とAN-756、およびアナログ・ダイアログ:A/Dコンバータのクロックの最適化 試験工学的な観点に記載しており、www.analog.comで参照できます。これらのアプリケーション・ノートでは、アパーチャ・ジッタの測定方法、および必要な位相ノイズ/ジッタ仕様を満たすクロックの指定方法について説明しています。クロック源の指定が適切でないと、図8と図9に示すようにS/N比性能が低下します。参考として、代表的なWenzelクロック発振器のアパーチャ・ジッタは約0.07psであるのに対して、CMOSクロック発振器のアパーチャ・ジッタは約0.3ps以上です。

図8. −1.0dBFS で130MHz のアナログIF を持つAD9445(Wenzel クロックを使用、S/N 比 = 75.2dBFS)

図9. −1.0dBFS で130MHz のアナログIF を持つAD9445(CMOS クロックを使用、S/N 比 = 71.2dBFS)

必要なジッタ性能を持つクロック源を使用できない場合は、高周波クロックを低いレートに分割することができます。こうすると、10 log(x)のレートでジッタを減らす効果があります。ここで、x は分周比です。しかしこの方法では、ゲート自身のジッタによる制限があります。アプリケーション・ノートAN-501 には、さまざまなロジック・ファミリーに対応するクロック・ジッタの目安が掲載されています(www.analog.com 参照)。

カスタム・クロッキングが要求される場合、一般にPLL が必要となります。PLL では、VCO またはVCXO を使用してADC と外部クロック・リファレンスの同期をとることができます。しかし、簡単なPLL を使用して複数のデバイスをクロッキングすることは困難です。このようなクロッキングを可能にするには、デバイス間に遅延を追加する必要があります。図10 に示すようにクロックのクリーンアップと分配には、AD9516-0 などのデバイスが最適です。AD9516-0 の相加性ジッタは約0.22ps であり、このデバイスはADC、DAC、およびさまざまなロジック・デバイスの駆動用に最適化されています。

図10. AD9516-0 低ジッタ・クロック源

電源

ADC の電源は非常に重要です。従って、クリーンで静かな電源供給をすることが重要です。大半のADC はこれらの入力バイアス・ピン上の過剰なノイズを変調する可能性があるためです。これらのピン上のある量のノイズに対してADC がどのように動作するかを完全に理解するには、すべての電源の電源電圧変動除去比を、対象となる周波数帯域にわたって測定し、理解する必要があります。スイッチング・レギュレータは多くのアプリケーションに適しており、その例として、ADP5020、ADP2108、ADP2114 などが挙げられます。しかし、リニア・レギュレータの方が、多くの場合より静かで、より高性能なソリューションになります。ADP3338/ADP3339(図11 参照)やADP1706/ADP1707/ADP1708(図12 参照)シリーズなどのデバイスは、非常に低いノイズと安定したソースを可能にし、ほとんどのADC アプリケーションに適しています。更に、それらは様々な電圧で利用可能で、最大1A を供給できます。

図11. ADP3338/ADP3339 の代表的なアプリケーション

図12. ADP1706/ADP1707/ADP1708 の代表的なアプリケーション

高速ADC 用電源の設計の詳細については、www.analog.com の回路ノートCN0135 とCN0137 を参照してください。

データ・アクイジション

データのアクイジションと処理は、高速キャッシュ・メモリによって行われます。データは、使用するテスト方法に応じて、ADC のフルスピードで収集したり、デシメーションしたりできます。ベンチ・テストでは、HSC-ADC-EVALC 評価用プラットフォーム(デシメーションは不要)をVisualAnalog ソフトウェアと併用します(詳細については、HSC-ADC-EVALC 評価用プラットフォームのセクションを参照)。一般には16k、32k、64k のFFT が実行されますが、ベンチFFT は4M までのサンプルが可能となっています。アナログ入力ソースがクロックと同期していない(ノンコヒーレント・サンプリング)場合、一般にハニングまたはブラックマン・ハリス窓関数が使用されます。詳細については、「On the Use of Windows for Harmonic Analysis with the Discrete Fourier Transform」(Fredric J. Harris, Proceedings on the IEEE. Vol. 66, No. 1, January 1978)を参照してください。

AC テストの定義

一般に、AC または動的テストは、フルスケール(dBFS)より0.1dB、0.5dB、1dB 下の信号パワーを持つ定格周波数でのアナログ信号によって行われます。異なる振幅が使用される場合は、データシートのテスト条件で定義されます。これらのテストでは、一般にエンコード・レートは最大定格値またはその近くに設定されます。電源条件や温度条件などの他のテスト条件については、データシートを参照してください。

FFT テスト

実際のテスト条件に応じて、コヒーレントとノンコヒーレントの両方のFFT テストを用いることができます。コヒーレント・テストを行う場合は、キャプチャされたデータ・サンプルがレコード長に含まれるコンバータ・コードをできるだけ多く使用するようなアナログ周波数が選択されます。そのためには、アナログ周波数とエンコード・レートの間の最も重要な関係を使用します。

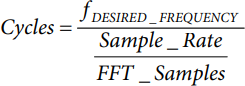

例えば、コヒーレント・サンプリングを使用し、65MSPS の仕様規定されたサンプル・レートで10MHz のアナログ入力が必要とされる場合、算出されるコヒーレント・アナログ入力周波数は10.0015258789063MHz、つまりちょうど2521 サイクルになります。これは次の式で計算できます。

サイクル数は最も近い整数に丸めます。可能ならば最も近い素数を選択して、コンバータの最大の量子化レベル数を使用できるようにします。サイクル数が選択されると、目的のアナログ入力周波数を使用して前の式を解くことができます。

一般にFFT テストの結果はデシベルで表します。単位はdBc(キャリアを基準として目的の信号を表す場合)またはdBFS(コンバータのフルスケールを基準として目的の信号を表す場合)で、いずれもフルスケールに対するキャリアのレベルを加算/減算することによってもう一方の単位に変換できます。FFT テストの詳細については、「The FFT: Fundamentals and Concepts」(Tektronix, Inc., 070-1754-00, Production Group 45, first printing December 1975)を参照してください。

シングルトーンFFT

S/N 比(SNR、dB)

S/N 比(SNR)は、信号振幅の実効値と全スペクトル成分(6 次までの高調波とDC を除く)の実効値総和との比です。入力レベルが減少するにつれて、一般にS/N 比もデシベル単位で直線的に減少します。

フルスケールを基準にしたS/N 比(SNRFS、dBFS)

フルスケールを基準にしたS/N 比(SNRFS)は、実効値フルスケールと全スペクトル成分(6 次までの高調波とDC を除く)の実効値総和との比です。SNRFS はフルスケールを基準にしたデシベルで表します(dBFS)。S/N 比とSNRFS の差異は、基本波の振幅とフルスケールの差異です。

信号/ノイズ + 歪み(SINAD、dB)

信号/ノイズ + 歪み(SINAD)は、信号振幅の実効値と全スペクトル成分(DC を除く高調波)の実効値総和との比です。S/N比とSINAD の差異は、6 次までの高調波に含まれるエネルギーです。

ユーザ定義のS/N 比(UDSNR、dB)

UDSNRは、ユーザが定義可能な周波数範囲にわたってノイズの積分限界を設定する能力を指す用語です。FFT 解析の詳細については、www.analog.com にあるアプリケーション・ノートAN-905:VisualAnalog™ コンバータ評価用ツールVer 1.0 ユーザ・マニュアルを参照してください。信号振幅の実効値とユーザが設定した指定帯域内の全スペクトル成分(6 次までの高調波とDCを除く)の実効値総和との比です。UDSNRはデシベルで表します。

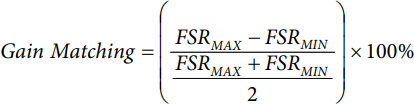

ノイズ指数(NF、dB)

ノイズ指数(NF)は、デバイスの出力におけるノイズ・パワーとデバイスの入力におけるノイズ・パワーとの比です。ここで、入力ノイズ温度はリファレンス温度(298K)と同じです。ノイズ指数はデシベルで表します。

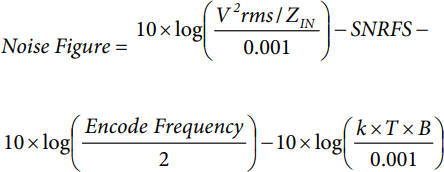

ADC のノイズ指数は、1 つの構成に対して計算できます。入力範囲、終端、サンプル・レートが固定であると想定すると、ADC のNF は次式で計算できます。

ここで、

Vrms = 実効値フルスケール入力電圧

ZIN = ADC の入力インピーダンスまたは入力ネットワークおよびADC の入力インピーダンス

SNRFS = フルスケールADC のS/N 比

Encode Frequency = ADC のクロック・レート

k = ボルツマン定数 = 1.38 × 10−23

T = ケルビン温度 = 298 K.

B = 対象の帯域幅 (Hz)

ノイズ・フロア(dBFS)

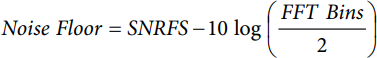

ノイズ・フロアは、VisualAnalog ソフトウェアで使用する用語です(www.analog.com にあるアプリケーション・ノートAN-905:VisualAnalog™ コンバータ評価用ツールVer 1.0 ユーザ・マニュアルを参照)。ノイズ・フロアは、次式で計算できます。

これは各FFT ビンにおける平均ノイズを示します。FFT のサイズが2 倍になった場合、この数値は3dB 減少します。ノイズ・フロアでは絶対的な計測値を得ることはできず、特定のセットアップに対するノイズの位置を相対的に示します。

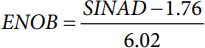

有効ビット数(ENOB、ビット)

有効ビット数(ENOB)は、ビットで表すADC の測定性能です。有効ビット数を最も正確に測定するには、サイン波の曲線近似法を使用します。ENOB を計算する最も一般的な方法では、コンバータのフルスケールでのSINAD に基づいて、次式を使用します。

スプリアスフリー・ダイナミック・レンジ(SFDR、dBc)

スプリアスフリー・ダイナミック・レンジ(SFDR)は、信号の実効値と最も厳しい結果をもたらすアナログ入力ピーク・スプリアス・スペクトル成分の実効値との比です。ほとんどの場合、SFDR はADC に印加される入力信号の高調波です。

高調波歪み(dBc またはdBFS)

高調波は、駆動されるアナログ入力周波数の整数倍のスペクトル成分です。例えば、2 次高調波の周波数はアナログ入力周波数の2 倍です。大部分のADC には、1 つまたは複数の高調波に対する仕様があります。一般に2 次と3 次の高調波が選ばれる理由は、すべての高調波のうち最も悪影響を与える性能を持つためです。

高調波歪みは、順序を問わず、信号振幅の実効値と指定された高調波成分の実効値との比であり、dBc またはdBFS で表します。

ADC は非直線性デバイスであるため、出力にはスペクトル成分が豊富に含まれています。最大のスプリアス・エネルギーは、最初の2 つの高調波(2HD と3HD)とは直接関係していない場合があり、他の最大スプリアス(WoSpur)によって測定されます。WoSpur は、信号振幅の実効値と最大スプリアス成分(最初の6 つの関連する高調波成分を除く)の実効値との比であり、dBc で表します。

全高調波歪み(THD、dBc)

全高調波歪み(THD)は、信号エネルギーの実効値と6 次までの高調波の実効値総和との比です。

高調波イメージ(dBc)

高調波イメージの測定結果は、インターリーブされたADC を解析する場合のみ有効です。この仕様は大部分のADC には適用されません。高調波イメージは、信号振幅の実効値と2 つのADCのクロッキング位相差から生じる非高調波成分の実効値との比であり、dBc で表します。

図13. シングルトーン・テストのセットアップ

ツートーンFFT

複数のトーンが非直線性を持つコンバータを通過すると、相互変調歪み積(IMD)が生じます。ADC でのツートーン・テストは、このような非直線性を特定する手段です。アナログ・スペクトルにおいては歪み積の多くが比較的高いため、周波数のエイリアスが生じる場合があります。歪み成分の識別に際しては、このことを忘れないでください。

F1 + F2(dBc)

これは周波数に現れる2 次歪み成分を表し、2 つの入力周波数を合計したものです。この値は、その実効値と2 つの入力トーンの一方の実効値との比であり、dBc で表します。

F2 − F1(dBc)

これは周波数に現れる2 次歪み成分を表し、2 つの入力周波数の差をとったものです。この値は、その実効値と2 つの入力トーンの一方の実効値との比であり、dBc で表します。

2 次入力インターセプト・ポイント(IIP2、dBm)

2 次入力インターセプト・ポイント(IIP2)は、コンバータのフルスケール入力信号パワーからIMD の2 次成分を引いた値であり、dBm で表します。

2F1 ± F2 および2F2 ± F1(dBc)

これらはコンバータの3 次歪み成分を表します。それぞれの値は、その実効値と2 つの入力トーンの一方の実効値との比であり、dBc で表します。ピーク・スプリアス成分は、IMD 成分とみなされます。

3 次入力インターセプト・ポイント(IIP3、dBm)

3 次入力インターセプト・ポイント(IIP3)は、コンバータのフルスケール入力信号パワーから3 次IMD 成分の1/2 を引いた値であり、dBm で表します。

その他の最大スプリアス(WoSpur、dBc)

その他の最大スプリアス(WoSpur)は、2 次または3 次の歪み成分には関係なく、2 つのアナログ入力信号の混合によって生じる最悪のスプリアスです。この値は、その実効値と2 つの入力トーンの一方の実効値との比であり、dBc で表します。

ツートーンSFDR(dBc)

スプリアスフリー・ダイナミック・レンジ(SFDR)は、信号の実効値と最も厳しい結果をもたらすアナログ入力ピーク・スプリアス・スペクトル成分の実効値との比です。ほとんどの場合、SFDR はADC に印加される入力信号の高調波です。

図14. ツートーン・テストのセットアップ

ノイズ・パワー比(NPR、dB)

ノイズ・パワー比(NPR)は、フル負荷のガウス・ノイズ源によるコンバータ性能の評価に使用される動的テストです。ノイズ・レベルの調整は、ナイキスト限定されたノイズ源によりクリッピング点のすぐ下の負荷がコンバータに加えられるように行われます。次に、ディープ・ノッチ・フィルタでナロー・バンドのノイズを除去します。ノッチ内のノイズ密度とノッチなしでのノイズ密度との比率を調べるため、FFT 技術を使用してノッチ内のノイズが測定されます。結果はデシベルで表します。図15 に示すように、NPR はクリッピングの直前に最適化されます。クリッピングが開始されると、NPR は入力信号の増大につれて急速に減少します。入力信号が減少した場合、ノイズ・パワーが1 デシベル減少するたびにNPR は約1dB 減少します。

図15. 代表的なNPR 曲線

図16. 12 ビット・コンバータに対する代表的なNPR 応答

図17. NPR テストのセットアップ

フルパワー帯域幅(MHz)

アナログ入力帯域幅は、FFT 解析によって決定される基本周波数のスペクトル・パワーが3dB 減少するアナログ入力周波数です。このテストではSFDR またはS/N 比性能の特定の値は得られません。

図18. 代表的なフルパワー帯域幅応答

図19. フルパワー帯域幅テストのセットアップ

ディザ・テスト

ADC のアナログ入力に意図的なノイズを印加すると、伝達関数のディザリングが発生して、静的な非直線性によるスプリアスが減ります。ディザはスルーレート制限による歪みの低減にはほとんど貢献しませんが、ADC 性能を妨げる局所誤差を減らすためには非常に効果的です。

ディザには帯域外とワイドバンドの2 種類があります。図20 のセットアップに示すように、帯域外ディザは帯域外に置かれた帯域制限ノイズであり、コンバータ性能をスペクトル的に混乱させることはありません。この技術は通信システムでよく使用されます。通信システムでは、目的の信号を選択して他の信号をすべてカットするためにデジタル・フィルタを使用します。ワイドバンド・ディザは、通常は高性能テスト機器で使用されます。この構成では、入力にワイドバンド・アナログ・ノイズが加算され、それに対応するデジタル値が出力から減算されます。これらの技術によって、コンバータのスプリアス性能が大幅に向上するという効果が得られます。詳細については、当社のWeb サイト(www.analog.com)にてアプリケーション・ノートAN-410を参照してください。

図20. ディザ・テストのセットアップ

ディザを使用すると、アプリケーションにもよりますが、一般にスプリアス性能は15dB 以上改善します。多くのデータシートには、比較のためにディザ性能のグラフが含まれています。

アナログ入力

アナログ入力インピーダンス

アナログ入力インピーダンスは、複素入力電圧をアナログ入力用の複素入力電流で割った比率です。一般にアナログ入力インピーダンスはネットワーク・アナライザにより測定され、スミス・チャートに表示されます。

場合によっては、複素入力は、抵抗、容量、誘導の各項に分解して表すこともできます。

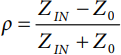

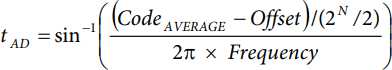

電圧定在波比(VSWR)

VSWR は、ADC の入力から反射により戻されるパワー量の値です。これはADC の入力ポートへのエネルギー転送の効率を示します。

デバイスからの反射により戻されるパワー量は、次式に基づいて入力インピーダンスから計算できます。

ここで、

ρ はデバイスからの反射により戻されるパワー量。

ZINは、ADC の複素入力インピーダンス。

Z0 は、ネットワークで必要とされるインピーダンス。

反射係数から、次の式を使用してVSWR を計算できます。

図21. アナログ入力インピーダンスとVSWR テストのセットアップ

アナログ入力フルスケール・レンジ(Vp-p)

アナログ入力フルスケール・レンジは、有効なフルスケール応答を生成するためにコンバータのアナログ入力に印加できるピークto ピーク電圧(シングルエンドまたは差動)の範囲です。

図22. アナログ入力フルスケール・レンジ・テストのセットアップ

コモンモード入力範囲(V)

コモンモード入力範囲は、コンバータが通常の信号範囲内で動作するADC の両方のアナログ入力ピンに印加または供給される直流オフセット範囲です。通常、バッファなしのコンバータを適切に動作させるには、直流コモンモード・バイアスを供給する必要があります。このバイアスは通常、AVDD/2 であり、外部分圧器、または上記コンバータが提供するVCM/CML ピンで設定できます。バッファありのコンバータには内部バッファがあり、通常、このバイアスの提供に必要な他のハードウェアを用いずに、アナログ入力ピンに直接、コモンモード(AVDD/2 +0.7V)を提供します。

どのコンバータにも、動作して優れた性能を発揮できる最適な範囲があります。この範囲は限定的な場合と広い場合があるため、念のためコンバータのデータシートを参照してください。

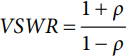

同相モード除去比(CMRR、dB)

同相モード除去比(CMRR)は、共通の信号が印加されたときの差動アナログ入力での除去量として定義されます。一般にCMRR はデシベルで表され、次式に示すように計算できます。

2 つのアナログ入力を結合し、必要に応じてアナログ入力にコモンモード・バイアスをかけ、コンバータのフルスケール付近に入力信号を注入します。CMRR を計算するには、FFT ディスプレイに基本スパー・レベル(dB)を記録してACOMMON MODE 数を収集します。ADIFFERENTIAL 数を収集するには、コンバータの入力に印加されたアナログ入力レベルをdB で記録します。次に、この測定を、いくつかの周波数または対象の帯域にわたって繰り返します。

図23. CMRR テストのセットアップ

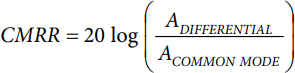

アパーチャ遅延(AD、ps)

アパーチャ遅延(AD)は、アナログ・パスとエンコード・パスとの間の遅延の差を表します。これを測定するには、サンプル・クロックの立上がりエッジの50%ポイントから、入力信号が実際にサンプリングされるまでの時間を観測します。

AD を測定するには、次のテスト構成を使用します。

- アナログ入力をフィルタ済みアナログ信号源に接続します。

- VisualAnalog ADC Analyzer などのソフトウェアを使用して、シングルトーンFFT がフルスケール信号(0dBFS)になるまで入力を調整します。

- アナログ入力を切断し、ショート・バーを使用してアナログ入力をグラウンドに短絡します。

- 連続平均時間領域プロットを使用して、デバイスのオフセットを測定します。

- アナログ入力からショート・バーを取りはずし、図24 に示すようにアナログ入力を再接続します。

- 新しいオフセット値を記録し、それを用いて次の式を解きます。

ここで、

CodeAVERAGEは、アナログ入力からショート・バーを取りはずしてアナログ入力を再接続した後で得られる新しいオフセット値(ステップ5 を参照)。

Offset は、連続平均時間領域プロットを使用して測定されたデバイスのオフセット(ステップ4 を参照)。

2N/2 は、ADC のミッドスケール。

図24.アパーチャ遅延テストのセットアップ

アパーチャ・ジッタまたはアパーチャ不確定性(ps RMS)

アパーチャ・ジッタは、アパーチャ遅延におけるサンプル間変動であり、ADC 入力での周波数依存ノイズとして現れることがあります。アパーチャ・ジッタの測定の詳細についてはアプリケーション・ノートAN-501 を、アパーチャ・ジッタを位相ノイズに変換する方法の詳細については当社のWeb サイト(www.analog.com)にてアプリケーション・ノートAN-756を参照してください。

図25. アパーチャ不確実性

クロストーク(dB)

クロストークは、マルチチャンネルADCのクワイエット・チャンネルに混入するフィードスルーの値と定義されます。クロストークは2 つの条件下で3 つの方法により測定されます。

条件1

信号がフルスケール近くに駆動された場合、クロストークは次のいずれかの方法により測定されます。

- −0.5dBFS で互いに2MHz 以上離れた異なるミッドベースバンド周波数を使用して、2 つのチャンネルを駆動します。オープン・チャンネル(非駆動)上の同じ基本周波数を記録します。これをすべてのチャンネルの組合わせについて繰り返します。

- −0.5dBFS で1 つのミッドベースバンド周波数を使用して、任意のN − 1 チャンネルを駆動します。オープン・チャンネル(非駆動)上の同じ基本周波数を記録します。これをすべてのチャンネルについて組合わせで繰り返します。

条件2

信号がフルスケールを3dB 超えて駆動された場合(オーバードライブ条件)、クロストークは次のように測定できます。

- 条件1 で説明したいずれかの方法を使用しますが、ミッドベースバンド周波数の振幅は、フルスケールより3dB上に設定します。

すべての結果は、クワイエット・チャンネル上の不要信号のエネルギーと駆動チャンネル上のエネルギーとの比として、デシベルで表します。

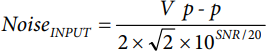

入力換算ノイズ(LSB RMS)

これは、図26 に示すように、ADCによって生じる広帯域ノイズの尺度です。入力が接地されている間に、出力コードのヒストグラムが作成されます。入力換算ノイズはヒストグラムの標準偏差を使用して計算され、LSB rms で表します。

図26. 入力換算ノイズのヒストグラム

この測定を互いに関係付けるには、SNRFS 測定を使用し、次式によりデシベルをボルトに変換します。

ここで、

Vp-p はADC のフルスケール入力範囲、

SNR は小さな入力信号によって駆動された場合のフルスケールのS/N 比性能です。

アウトオブレンジ回復時間(CLK サイクル)

アウトオブレンジ回復時間とは、過渡入力が正側フルスケールの10%上から負側フルスケールの10%上まで変化した後、または負側フルスケールの10%下から正側フルスケールの10%下まで変化した後で、ADC が定格精度まで回復するために必要な時間です。

デジタル時間領域

最小変換レート(MSPS)

最小変換レートは、仕様規定された最低のアナログ信号周波数のS/N 比が、サポートされる限界から3dB を超えない範囲で低下するときのクロック・レートです。

最大変換レート(MSPS)

最大変換レートは、パラメータ・テストが実行されるクロック・レートです。これより高い動作レートも可能ですが、保証はされていません。

パイプライン遅延(CLK サイクル)

パイプライン遅延は、コンバータを通じての遅延であり、エンコード・サイクルの関数となります。スループットを最大にするため、多くの高速コンバータではパイプライン処理を活用します。その結果、対応するデータは、信号がサンプリングされてから数クロック・サイクル経過しないと出力されません。この遅延がパイプライン遅延であり、データ・コンバータに応じてクロック・サイクルの全体または一部として表わすことができます。

一般的な評価用ボードのセットアップについては、図27 を参照してください。オシロスコープの1 つのチャンネルを用いて、アナログ入力をキャプチャします。もう1 つのチャンネルを用いて、MSB データ・ビットをキャプチャします。このチャンネルにトリガを設定して、立上がりエッジでキャプチャします。遅延量を測定するには垂直カーソルを用います。パイプライン遅延は、アナログ入力の立上がりエッジのゼロ交差と50%のMSB データ・ビットの立上がりエッジとの間の時間差として定義されます。求めた時間差を1/サンプル周波数で割って、パイプライン遅延を求めます。

図27. パイプライン遅延テストのセットアップ

伝搬遅延(ns)

伝搬遅延は、クロック・ロジックのスレッショルド(または差動クロック入力の50%ポイント)から全ビットが有効ロジック・レベルになるまでの遅延です。

エンコード・パルス幅またはエンコード・デューティサイクル

エンコード・パルス幅ハイは、エンコード信号がロジック・ハイ状態になり、仕様性能を達成できるようになるための最小時間です。エンコード・パルス幅ローは、エンコード信号がロジック・ロー状態になり、仕様性能を達成できるようになるための最小時間です。従来のADC では、エンコード信号がロジック・ハイ状態にあると、回路はサンプル・モードにあります。ハイ状態の保持時間が短すぎると、サンプル・プロセスは正しく完了できません。また、ロー状態の保持時間が短すぎても、回路はサンプリングされる信号を正しく取得できません。取得時間とサンプル時間のバランスがうまく取れると、最適な動作が達成されます。

多くのコンバータでは、パルス幅の測定の代わりにエンコード・デューティサイクルが提供されます。通常これは最大定格エンコードと呼ばれ、エンコード・ラインをハイ状態にできる時間のパーセンテージ範囲として表します。

このテストでは、定格性能は、SNRFS 性能が公称性能の−3dB以内である範囲と定義されます。

図28. 伝搬遅延テストのセットアップ

変換誤差レート(CER)

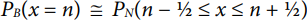

変換誤差レート(CER)は、ADC によって生じる誤差の頻度を表します。誤差は、正規分布ノイズによって許容される限度を超えてコンバータ・ノイズの上下限を外れる出力コードと定義されます。コンバータ・ノイズは、一般に量子化、熱効果、およびクロック・ジッタによって生じるノイズと定義され、一般にはガウス分布とみなされます。ただし、コンバータのノイズおよび誤差は、実際には二項分布であり、連続式の半整数補正を用いて正規分布から推定できます。

サンプルがエラーとみなされるのは、発生頻度が正規分布による予測値を超える場合です。

図29. 二項分布(サンプル数:100 万)

ノイズの大きさはシグマ(σ)に正規化され、フルスケールのS/N 比を測定し、その値を用いて次式を解くことによって決定できます。

想定されるS/N 比(またはデータシート)に基づいてシグマが決定されると、想定されるADC コードが実際のコードから減算されて分布のヒストグラムが得られるようにデータをキャプチャできます。統計学的に大きなデータ・セットでは、通常のADCノイズに対して、図29 に示すような分布が得られると想定できます。大きな分布では、表1 に示すように、これらの範囲を超えるサンプルはビット誤差を示します。

| σ | Normal Probability of Occurrence | Natural Occurrences Outside in 1 Million Samples |

| 3.58 | 2 × 10−3 | 2000 |

| 4.22 | 2 × 10−4 | 200 |

| 4.76 | 2 × 10−5 | 20 |

| 5.25 | 2 × 10−6 | 2 |

| 5.70 | 2 × 10−7 | 0.2 |

| 6.11 | 2 × 10−8 | 0.02 |

| 6.50 | 2 × 10−9 | 0.002 |

| 6.85 | 2 × 10−10 | 0.0002 |

なお、100MSPS のサンプル・レートでは、6.85 シグマを外れる1 つの誤差は50 秒窓では正常であり、変換誤差とはなりません。そのレートが2 × 10−10 を超えた場合にのみ、変換誤差となります。実際はラッチ処理やメモリ素子を含む外部デバイスにより、およそ2 × 10−6 または2 × 10−7を超える測定は困難となります。

DC テストの定義

ゲイン誤差(%FS)

ゲイン誤差は、測定したフルスケールと理想的なフルスケールとの差異です。一般にフルスケールのパーセンテージで表します。

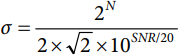

ゲイン・マッチング(%FS)

ゲイン・マッチングは、マルチチャンネルADCの最大のフルスケールと最小のフルスケールの比であり、次の式を使用してフルスケールのパーセンテージで表します。

ここで、

FSRMAX は最も大きな正側のゲイン誤差(単位:V)。

FSRMIN は最も小さな負側のゲイン誤差(単位:V)。

オフセット誤差(%FS)

オフセット誤差は、出力側でミッドスケール・コードを発生させるアナログ入力での測定した電圧と理想的な電圧との差異です。一般にフルスケールのパーセンテージで表します。

オフセット・マッチング(mV)

オフセット・マッチングはマルチチャンネル・コンバータのチャンネル間のオフセットの差異であり、ミリボルトで表します。次の式で計算できます。

ここで、

VOFFSETMAX は最も大きな正側のオフセット誤差。

VOFFSETMIN は最も小さな負側のオフセット誤差。

一般にオフセット・マッチングはミリボルトで表され、フルスケール入力範囲は製品のデータシートに記載されています。

温度ドリフト(ppm)

オフセット誤差とゲイン誤差の温度ドリフトは、初期(25ºC)値からTMIN またはTMAX での値までの最大変化を示すものです。一般にppm で表します。

電圧出力ハイ/電圧出力ロー(VOH/VOL、V)

電圧出力ハイ(VOH)は、ハイのロジック・レベルを表す電圧です。電圧出力ロー(VOL)は、ローのロジック・レベルを表す電圧です。

DC テストや静的テストは、一般にDC またはきわめて低周波のテスト信号で行われます。これらのテストの目的は、多くのコア・コンバータ仕様の基準値を決定することです。テスト条件は製品によって異なるため、実際のテスト条件を決定するには製品のデータシートを参照してください。

直線性

コンバータの直線性には、微分非直線性(DNL)と積分非直線性(INL)の2 種類があります。ADC の基本的な指標は、各コードがアクティブである電圧の範囲です。コンバータの全体的な伝達関数は、これらの電圧の積分によって決まります。ADC の静的な特性性能は、この2 つの基本的な計測値によって決まります。

これらのテストは、多くの場合ヒストグラム技術を用いて実行されます。ヒストグラムを収集するには、既知の統計的品質を持つ信号でADC のアナログ入力を駆動します。例えば、DC ランプは一様な確率密度関数の品質を備えています。つまり、ADC 入力を駆動する際、各ADC コードは大きな観測窓の全域で同じ発生確率を持つことになります。サイン波など他の波形にも、既知の関数があります。このような波形は一様ではありませんが、数学的には正確に記述できます(The Data Conversion Handbook(Walt Kester, Newness, 2005, Page 315)を参照してください。)。

代表的なヒストグラム・テストは、妥当な限り多数のサンプルを使って実行されます。高分解能のコンバータでは400 万個以上のサンプルになることもあります。

微分非直線性誤差(DNL、LSB)

微分非直線性(DNL)は、理想的な1LSB ステップからのコードの変動です。これを測定するには、各ヒストグラム・ビンを検査して、実際の発生確率と理想的な確率を比較します。これによりコードごとにDNLの直接的な指標が得られます。

図30. 代表的な10 ビットDNL

ミッシング・コード

コードがミッシングといわれるのは、そのコードのDNLが−1LSB である場合です。ミッシング・コードは、ミッシング量子化レベルと定義され、さまざまな原因によって生じます。大部分の製品は、ノー・ミッシング・コードを実現するように設計または選別されています。

積分非直線性誤差(INL、LSB)

積分非直線性(INL)は、最小2 乗法によって決定されるベスト・ストレート・ライン近似を用いたリファレンス直線からの伝達関数の偏差であり、1LSB 単位で測定されます。測定では、ヒストグラムを積分して伝達関数を形成してから、この関数に対して直線回帰を実行します。INL は、実際の伝達関数とこのベスト・ストレート・ライン近似との差異です。

図31. 代表的な10 ビットINL

図32. DNL およびINL テストのセットアップ

電源電圧変動除去比(PSRR、dB)

電源電圧変動除去比(PSRR)は、ADC のデジタル出力にカップリングされる電源上の信号量を表します。PSRR を測定するには、電源を変え、コンバータのオフセットの変化を測定し、フルスケールのパーセンテージで表します。より一般的には、PSRR の測定は、既知の振幅の交流信号を電源ピンに注入し、FFT のスペクトル観測値を測定して行います。PSRR は、ADC によって測定されたボルト値とオシロスコープによって測定された入力値との差異であり、デシベルで表します。

図33. PSRR テストのセットアップ

参考資料

データ・コンバータ特性の詳細については、The Data Conversion Handbook(Walt Kester, Newness, ISBN 0-7506-7841-0)を参照してください。www.analog.com には、High Speed Design Techniques 、Practical Analog Design Techniques 、Linear Design Seminar、System Applications Guide など、その他の参考文献も掲載しています。アナログ・デバイセズの販売代理店では、多くの参考文献のほか、さまざまなアプリケーション・ノート、記事、転載情報を提供しています。詳細については、当社のWebサイト(www.analog.com)を参照してください。

その他の参考資料

Brannon, Brad 1995 年。アプリケーション・ノートAN-410「ディザ使用によるコンバータ非直線性の改善」アナログ・デバイセズ(12 月)

Brannon, Brad 2004 年。アプリケーション・ノートAN-756「サンプル化システムに及ぼすクロック位相ノイズとジッタの影響」アナログ・デバイセズ(12 月)

Brannon, Brad and Allen Barlow 2006 年。アプリケーション・ノートAN-501「アパーチャ不確定性とADC システム性能」アナログ・デバイセズ(3 月)

Brannon, Brad and Tom MacLeod 2009 年。アプリケーション・ノートAN-737「ADIsimADC によるADC モデリングの方法」アナログ・デバイセズ(4 月)

Caserta, Jim and Rob Reeder「アプリケーション・エンジニアに尋ねる— 36 広帯域A/D コンバータ・フロントエンド設計についてII:ADC にはアンプ駆動かトランス駆動か?」アナログ・ダイアログ、第41 巻、2 月(2007 年)

Cobb, Michael and Rob Reeder(2009 年6 月)「Webcast:Designing with Switching Regulators in High-Speed A/D Converter Applications」アナログ・デバイセズおよびAvnet Electronics Marketing

Downing, Salina and Rob Reeder(2006 年4 月)「Webcast:Designing Transformer Coupled Front-Ends for High Performance A/D Converters」

Green, Wayne, Rob Reeder, and Robert Shillito「A/D コンバータのクロックの最適化 試験工学的な観点」アナログ・ダイアログ、第42 巻2 号、2 月(2008 年)

Hand, Jim, Mark Looney, and Rob Reeder「Pushing the State of the Art with Multichannel A/D Converters」アナログ・ダイアログ、第39 巻5 号、5 月(2005 年)

Kessler, Walt and Rob Reeder「NPR Specification Aids Wireless System Analysis」Microwaves & RF、12 月(2005 年)

Newman, Eric and Rob Reeder「A Resonant Approach to Interfacing Amplifiers to Switched-Capacitor ADCs」Microwave ProductDigest、9 月(2005 年)

Newman, Eric and Rob Reeder 2006 年。アプリケーション・ノートAN-827「共振方式によるアンプとスイッチド・キャパシタADC のインターフェース」アナログ・デバイセズ(1月)

Reeder, Rob「Testing an A/Ds power supply rejection ratio」EE Times、2003 年7 月1 日

Reeder, Rob 2005 年~2009 年。アプリケーション・ノートAN-742「スイッチド・キャパシタADC の周波数領域応答」アナログ・デバイセズ(9 月)

Reeder, Rob「Transformer-Coupled Front-End for Wideband A/D Converters」アナログ・ダイアログ、第39 巻(2009 年4 月)

Reeder, Rob「Compare aperture delay between ADCs」Test & Measurement World、2002 年5 月1 日

Rob Reeder「Wideband A/D Converter Front-End Design Considerations」アナログ・ダイアログ、第40 巻7 号、7 月(2006 年)

Reeder, Rob 2007 年。アプリケーション・ノートAN-935「ADC トランス結合フロントエンドの設計」アナログ・デバイセズ(9 月)

Reeder, Rob 2009 年。回路ノートCN-0135「Powering the AD9272 Octal Ultrasound ADC/LNA/VGA/AAF with the ADP5020 Switching Regulator PMU for Increased Efficiency」アナログ・デバイセズ(10 月)

Reeder, Rob「Considering the ADC input-interface」EE Times Europe、2009 年12 月1 日

Reeder, Rob「Improve the Design of Your Passive Wideband ADC Front-End Network」Electronic Design、2010 年3 月26 日

Rob Reeder「RAQ:そのフィルタ、ちゃんとフィルタリングしてますか?」EDN, Design News、2009 年2 月1 日

Rob Reeder「RAQ:コモンモードを共通にしておく」EDN,Design News、2009 年4 月1 日

Rob Reeder「RAQ:ケネス、(コンバータの)周波数は何だ?」Design News、2009 年7 月17 日

Rob Reeder「RAQ:今回はコンバータ・ノイズについて-第1部」Design News、2009 年10 月1 日

Rob Reeder「RAQ:今回はコンバータ・ノイズについて-第2部」Design News、2009 年11 月23 日

Rob Reeder「RAQ:A/D コンバータの電源をおとなしくさせるには」Design News、2010 年3 月1 日