資料ライブラリ

AN-935:ADC トランス結合フロントエンドの設計

はじめに

本書では、高い中間周波数(IF)での狭帯域アプリケーションに最適なA/D コンバータ(ADC)のフロントエンドを設計するための、5 つのステップからなる方法を示します。

現代の通信システムや試験装置では、多くの場合、デジタル信号として信号処理を行うためにアナログの信号をできるだけ早い段階でデジタル化します。しかし、高い中間周波数(IF)を扱うシステムの場合では特に、ADC のトランス式フロントエンド回路の設計は容易ではありません。幸い、ここに示す5 ステップの効率的な方法が、ADC の最適なフロントエンドの開発に役立ちます。この方法はほぼすべてのアプリケーションに簡単に適用でき、必要な性能を実現することができます。

5 ステップからなるこの方法は、次の簡潔で論理的な手順から構成されます。

- システム/設計条件を知る。

- ADC の入力インピーダンスを求める。

- ADC の基本性能を求める

- 負荷にマッチングするトランスと受動素子を選択する。

- 設計をベンチ・テストする

ステップ1:システム/設計条件を知る

最初のステップは、言うまでもなく、特定アプリケーションの条件を知ることです。条件がわかれば、最初から適正な部品を選択して、目標性能を速やかに達成できるため、試行錯誤の回数を容易に減らすことができます。各設計条件のリストを作成し、その条件から逸脱しないように必要な性能限界を設定します。これによってADC とトランスの選択を速やかに実行できます。

たとえば、110 MHz を中心とした20 MHz 帯域幅(100~120 MHz)で入力信号を取り込むために61.44 MSPS のサンプリング・レートを必要とするアプリケーションについて考えてみます。所望のS/N 比(SNR)が72 dB より高い場合は、14 ビットのADC を使って必要なSNR 性能を実現します。消費電力は1 チャンネル当たり500 mW 未満とします。システム・レベルのこのような性能条件を満たすADC としては、アナログ・デバイセズの14 ビット、80 MSPS の製品AD9246 があります。このデバイスは1.8~3.3Vの電源電圧で動作します。AD9246 を選択した理由は、広帯域と低消費電力という特性にあります(表1 を参照)。

| Boundaries | Input Impedance (Ω) | VSWR | Pass-Band Flatness (dB) | IF –3 dB BW (MHz) | SNR(dBc) | SFDR(dBc) | Input Drive Level (dBm) |

| Ideal Value | 50 | 1 | <0.5 | 150 | 72 | 85 | 4 |

| Design Limit | 30 | 1.5 | <1 | 300 | 69 | 80 | 7 |

この設計例では、サンプリング・レートが61.44 MSPS、帯域幅が20 MHz で、110 MHz IF をADC に入力します。帯域幅は狭いため(1 ナイキスト帯域)、共振マッチング方法を使います。このタイプのマッチングは狭い帯域幅にのみ適用可能ですが、特定の周波数範囲では優れたマッチングが可能となります。一般にこの方法では、ADC 入力段の寄生容量を共振除去するために、アナログ入力に直結する、インダクタまたはフェライト・ビーズを追加する必要があります。もし目的とするIF がベースバンド帯域内(最初のナイキスト帯域)にあれば、単純なRC 回路のローパス・フィルタが利用できます。

ステップ2:ADC の入力インピーダンスを求める

2 番目のステップでは、ADC の入力インピーダンスを求めます(図1 を参照)。当該デバイスAD9246 は、アンバッファ/スイッチド・キャパシタADC です。したがって、入力インピーダンスは時変であり、またアナログ入力周波数に応じて変化します。このデバイスの入力インピーダンスを求めるときは、AD9246 の製品ページにあるスプレッドシートを使用できます。このスプレッドシートから、トラック・モードのところの110 MHz でのインピーダンスを求めてください。この例では、ADC の入力内部負荷は4 pF コンデンサに並列接続された6.9 kΩ の差動抵抗に相当します。これらの数値はこのADC が実際にサンプリング状態のときのものであるため、このADC トラック・モードにマッチングさせることを推奨します。表2 に、AD9246 の製品ページにあるスプレッドシートの一部を示します。

図1. ADC の入力内部インピーダンス(抵抗とコンデンサの並列接続構成)

| Frequency (MHz) | Track Mode | Hold Mode | ||||

| R (kΩ) | C (pF) | R (kΩ) | C (pF) | |||

| 109.02 | 7.012504 | −4.023861 | 23.621962 | −2.219631 | ||

| 109.64 | 7.001112 | −4.020610 | 23.501558 | −2.219192 | ||

| 110.27 | 6.909521 | −4.017265 | 23.226639 | −2.218956 | ||

| 110.89 | 6.806530 | −4.013601 | 23.724023 | −2.218073 | ||

| 111.52 | 6.750957 | −4.012279 | 23.477964 | −2.216845 | ||

| 112.14 | 6.695931 | −4.010091 | 23.463246 | −2.216127 | ||

| 1太字の数値はこの設計例に使用されている値です。 | ||||||

ステップ3:ADC の基本性能を求める

3 番目のステップでは、すべての設計パラメータを最適化する前にADC の基本性能を明確にし、ADC の動作状況を把握します。この基準を確定するために、デフォルト状態に設定されている評価用ボードを使用します。製品のデータシートの仕様については、ほぼこのような方法でADC の特性評価が行われています。

次に、性能仕様を収集します。フルスケール−1 dB(dBFS)、周波数110 MHz の入力信号を高速フーリエ変換(FFT)した結果を収集すれば、データシートの仕様に近い72 dB のSNR と82.7 dBc のスプリアスフリー・ダイナミック・レンジ(SFDR)が得られます。この特性評価は、高性能の信号発生器とフィルタを使って行います。フィルタは、テストの実行時に信号発生器の高調波とスプリアス成分を除去します。

この後、フィルタを除去して、ADC の評価用ボードをテスト信号発生器に再接続します。この発生器の出力レベルを再調整し、ADCの入力レベルとして記録しておきます(この場合は14 dBm)。パスバンド平坦性の変化の状況と–3 dB ポイントを確認するために、入力周波数は十分な帯域幅で掃引を行う必要があります1。この場合、デフォルトのフロントエンド回路の構成は単純なRCフィルタであり、1.2 dB のパスバンド平坦性と約100 MHz の帯域幅を持っています。

このデータを収集した時点で、いくつかの決定を行います。72 dBSNR と83 dBc SFDR の条件下では、アンチエイリアス・フィルタ(AAF)を使ってスプリアス性能を改善し、信号の高調波を低く抑えることがきわめて重要です。しかし、これは入力の駆動やパスバンド平坦性の問題の解決にはなりません。評価用ボード上のデフォルトのAAF は、目的のパスバンドを急激に減衰させてしまいます。単純なシャント・インダクタを使うことで、その周波数での減衰を抑えて、帯域外で適正なロールオフ(減衰)を実現できます。入力駆動については、インピーダンス比1:4 のトランスを使うことでADC のフルスケール動作が実現できます。これによって信号が+6 dB 増幅され、入力駆動要件を余裕を持って上回ることができます。最後にベクトル・ネットワーク・アナライザ(VNA)を使って入力インピーダンスとVSWR を測定します。当該周波数を選択して、入力がどれだけマッチングしているか確認します。この場合、110 MHz での実測値は35 Ω であり、VSWR は1.44:1 でした。

1 ADC のテストについては、AN-835 を参照してください。

ステップ4:負荷にマッチングするトランスと受動素子を選択する

4 番目のステップでは、負荷のインピーダンスにマッチングするトランスと受動素子を選択します。前のステップでは、基本性能を設定することで一定の動作基準を設けることができました。次に、トランス、およびR とL 両方のコンポーネントの値を負荷とうまくマッチするよう選択し、トランスの2 次側とADC 間の目標性能を達成できるAAF を構成します(図2)。

図2. フロントエンドの回路図(負荷にマッチングする抵抗とインダクタの値を選択します)

このような場面では、過去の経験や実験結果がものを言います。トランスの性能はそれぞれ大きく異なるため、その選択は容易ではありません。本書の場合は、測定済みで既知の性能のトランスを選択しました。一般には、優れた位相不均衡特性を持つトランスを選択することが重要です。このアプリケーション例の場合、帯域幅は狭く、低入力駆動を必要とします。したがって、インピーダンス比が1:4 の既知のトランスを使用しています。

ADC 用のトランスを選択する際の単純な指針としては、仕様をよく精査することが挙げられます。たとえば、リターンロス、挿入損失、位相/振幅不均衡などの仕様はじっくりと比較する必要があります。データシートにこれらのパラメータの仕様が記載されていない場合は、メーカーに問い合わせるか、ベクトル・ネットワーク・アナライザを使ってこれらを測定してください。標準的な磁束結合トランスとバラン型のいずれを選択するかは、帯域幅条件を満たす上で重要な意味を持ちます。標準型トランスの場合は周波数範囲が1 GHz 以下となる傾向にありますが、バラン型はそれよりもかなり高い帯域を実現できます。

終端は1 次側と2 次側の間で分割できますが、この例では、必要部品数を最小限に抑えるために2 次側だけが終端されています。アプリケーションによっては、終端を分割したほうがより適している場合があります。

アナログ入力には、小さな直列抵抗(15~50 Ω の任意の値)を使用します。この例では、2 個の33 Ω 抵抗を使用しています。これは、バッファなしADC からアナログ入力に向けて流れる電荷量を制限するためです。また、これは前段の信号源抵抗値を決定するのにも役立ちます。9 割の確率で33 Ω が使用できますが、抵抗値を変えると性能がわずかながら向上する場合もあります。

次に、トランスの2 次側の差動終端値を求めます。計算式からわかるように、2 次側差動終端の適正な設計開始値は251 Ω 未満となります。インピーダンスが1:4 という理論値通りのトランスであれば、200 Ω を使用します。まず、指定の中央周波数のリターンロス値を使って実際の特性インピーダンス(Z0)を計算します。

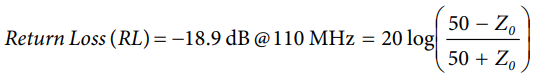

ここで、トランスの2 次側終端に関する計算式の例を示します。リターンロスは次式で求められます。

このリターンロス値を使って、トランスの2 次側の特性インピーダンスを求めることができます。

ここで、Z0 = 39.8 Ω です。

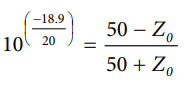

理論上の1:4 インピーダンス・トランスでは、2 次側が200 Ω の場合、1 次側は50 Ω にとなります。しかし、実際のシステムではそうはなりません。1 次側から見える実際のインピーダンスは、前のステップで求めたZ0 の値を使って、次の単純な計算式から求めます。

ここからX を求めると、X = 251 Ω となります。

実際のトランスでは何らかの損失が発生するため、2 次側終端を251 Ω とすることでその損失を補います。あらかじめトランスの2 次側終端値をより適切な値に設定することで、1 次側から見た適正なインピーダンスを得ることができます。この場合は、設計条件通り50 Ω とします。

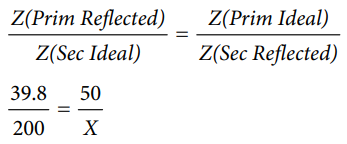

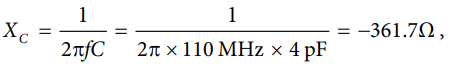

次に、内部のADC 寄生容量を共振除去するために、インダクタンスの値(L)を求める必要があります。容量(C)の値(4 pF)を代入することでL の値を簡単に求めることができます。

以下に、インダクタL の計算例を示します。

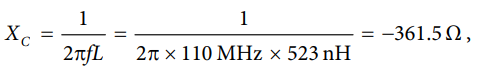

これらの値を使って、L の値を求めることができます。

L のリアクタンスはC と等しくなるように設定します。この場合は容量が4 pF で、インダクタンスが523 nH(110 MHz)になります。これで、L 値の設計開始値が設定されます。

ステップ5:設計をベンチ・テストする

最適なADC トランス・マッチングを実現するための最終ステップでは、これまでのステップで求めた抵抗とインダクタンスの値を使って設計をベンチ・テストします。先にADC 基本性能の設定をデフォルト状態で行ったのと同じように、SNR、SFDR、入力駆動レベル、パスバンド平坦性、入力インピーダンスなどの各性能を測定することが重要です。

最適な性能を得るには、R とL の値が両方とも計算した値とは異なっている場合があることに注意してください。これらのコンポーネントの値は、ベンダーごとの傾向や提供されているコンポーネントのサイズにより、最初に計算された値とは異なる場合があります。試行錯誤を繰り返す場合には、スプレッドシートを作成し、その都度性能の変化のようすを記録しておくと良いでしょう。

以下の、コンバータがほぼフルスケール状態の例では、SNR とSFDR 性能レベルが規定目標内で達成されています(図3 を参照)。110 MHz で、SNR はほぼ72 dB、SFDR は80 dBc です。図4 に、入力駆動レベル3.1 dBm で測定された最終的な性能結果を示します。このグラフでは、50 MHz 以上の帯域にわたって0.5 dB 未満のパスバンド平坦性も示されています。–3 dB 帯域幅はこの事例の要件には十分な150MHz あり、この設計に対して十分なスプリアス除去性能も実現しています。

図3. ADC におけるSNR およびSFDR の最終測定結果(本文でのトランスを使用)

図4. ADC における入力駆動およびパスバンド平坦性の最終測定結果(本文でのトランスを使用)

図5 は、入力回路設計をベクトル・ネットワーク・アナライザで測定した、スミス・チャートとVSWR プロットを示しています。入力インピーダンスは110 MHz で約41 Ω です。VSWR は1.2:1に近い値を保っており、フィルタの特性に適切に準じています。

図5. ADC 入力インピーダンスとVSWR に関する性能測定(本文でのトランスを使用)

この例は、入力回路またはADC アナログ・フロントエンドのマッチングをとることによって入力駆動、パスバンド平坦性(IF パスバンド)、負荷に供給される電力量(VSWR)が改善されることを示しています。この場合でも、ADC のデータシートに規定されている通りのSNR とSFDR 性能を達成しています。

オプション:ステップ6

6 番目のステップ(オプション)では、算出した性能と実際の測定結果とを比較します。インピーダンスについては、算出した値と測定値とを比較し、確認することができます。以下に、すべての入力をマッチングした場合の計算例を示します。

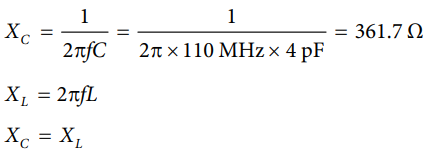

ADC 虚数インピーダンス

6.9 kΩ||4 pF または(6.9 kΩ + j0)||(0 − j361.7) = (18.9 − j361)、ADC インピーダンス

L 虚数インピーダンス

(18.9 − j361)||(0 + j361.5) = (6.93 kΩ + j72.8)

(6.93 kΩ + j72.8) + (66 + j0) = (6.97 kΩ + j72.8)、2 個の33 Ω 抵抗を加えます。

トランス2 次側の終端は

(6.93 kΩ + j72.8)||(242 + j0) = (234 + j82.1m)

絶対値は次式で得られます。

(Re2 + jX2)1/2 = 234 Ω

ステップ4 と同様にして、もう一度比をとります。

X を求めると、X = 42.7 Ω となります。この事例の場合、インピーダンスの測定値と計算値はかなり近い値となりました。

結論

新しい設計に取り組む際に大切なのは、設計の重要なパラメータに優先順位をつけた上で、時間をかけて適正なシステム/設計条件を確定するということです。

トランスを選択するときは、トランスによって違いがあることをまず認識し、異なるトランスを比較するために、トランスの仕様を完全に把握してください。仕様が手に入らないときには、メーカーに問い合わせて必要なパラメータ情報を入手してください。高い周波数のIF 設計はトランスの位相不平衡の影響を受ける場合があります。また、超高周波数IF 設計の場合は、偶数次歪みを抑制するために2 つのトランスまたはバランを必要とする場合があります。

ADC を選択するときは、バッファ付き、バッファなしのいずれのADC を使用するかを決める必要があります。バッファなしADC(スイッチド・キャパシタ型ADC など)は、入力インピーダンスが時変であるため、高周波数IF での設計は難しくなります。バッファなしADC を使用する場合は、常にトラック・モードの大きさに対して入力マッチングを行い、メーカーのウェブサイトにある入力インピーダンス・スプレッドシートを参照してください。一般に、バッファ付きADC のほうが高周波数IF の場合でも設計が簡単です。ただし、バッファなしADC よりも消費電力は増大します。こうした検証を最初に行うことが、R とL の値を計算する上での重要なポイントとなります。各アプリケーションですべてのレイアウトや寄生要素が同じになるとは限らないため、アプリケーションで必要な性能を最終的に得るためには、試行錯誤を繰り返すことが必要になる場合もあります。

参考資料

AN-742『スイッチド・キャパシタ ADC の周波数領域応答』

AN-827『A Resonant Approach to Interfacing Amplifiers to Switched-Capacitor ADCs』

AD9215、AD9226、AD9235、AD9236、AD9237、AD9244、AD9245のADC スイッチド・キャパシタ入力インピーダンス(S パラメータ)データ。製品ページで「評価用ボード」をクリックし、Microsoft Excel スプレッドシートをアップロードしてください。

Rob Reeder, “広帯域対応のA/Dコンバータに適したトランス・ベースのフロント・エンド回路” Analog Dialogue 39-2, 2005, pp. 3-6.

Rob Reeder, Mark Looney, and Jim Hand, “Pushing the State of the Art with Multichannel A/D Converters,” Analog Dialogue 39-2, 2005, pp.7-10.

Walt Kester, “Which ADC Architecture is Right for Your Application?” Analog Dialogue 39-2, 2005, pp. 11-18.

Rob Reeder and Ramya Ramachandran, “Wideband A/D Converter Front-End Design Considerations—When to Use a Double Transformer Configuration,” Analog Dialogue 40-3, 2006, pp. 19-22.

Rob Reeder and Jim Caserta, “Wideband A/D Converter Front-End Design Considerations: Amplifier- or Transformer Drive for the ADC,” Analog Dialogue 41-1, 2007, pp. 6-12.

Analog Devices (www.analog.com) 、AD9246 、80 MSPS/105 MSPS/125 MSPS、14 ビット、1.8 V、スイッチド・キャパシタ型ADC のデータシート

Mini-Circuits、モデルADT1-1WT のデータシート

M/A-COM、モデルETC4-1T-7、ETC1-1-13 のデータシート