Overview

Features and Benefits

- 64kB FIFO Depth

- Works with single and multi-channel ADCs

- Use with VisualAnalog® software

- Based on Virtex-4 FPGA

- May require adaptor to interface with some ADC eval boards

- Allows programming of SPI control Up to 644 MSPS SDR / 800MSPS DDR Encode Rates on each channel

- DDR Encode Rates on each channel

Product Details

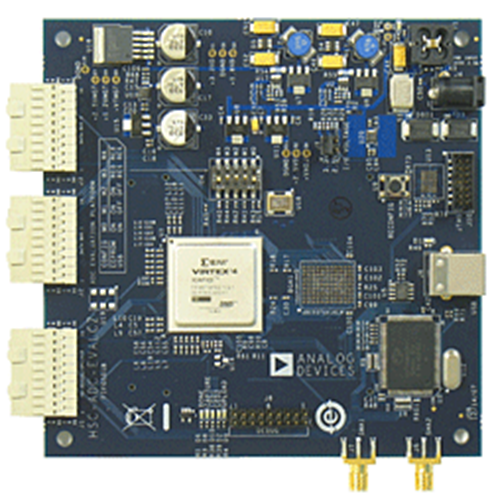

The HSC-ADC-EVALCZ high speed converter evaluation platform uses an FPGA based buffer memory board to capture blocks of digital data from the Analog Devices high speed analog-to-digital converter (ADC) evaluation boards. The board is connected to the PC through a USB port and is used with VisualAnalog® to quickly evaluate the performance of high speed ADCs. The evaluation kit is easy to set up. Additional equipment needed includes an Analog Devices high speed ADC evaluation board, a signal source, and a clock source. Once the kit is connected and powered, the evaluation is enabled instantly on the PC.Markets and Technologies

Applicable Parts

- AD9652

- AD6649

- AD9613

- AD6643

- AD6642

- AD6641

- AD9653

- AD9650

- AD9648

- AD9643

- AD9642

- AD9639

- AD9637

- AD9634

- AD9276

- AD9273

- AD9272

- AD9269

- AD9266

- AD9259

- AD9258

- AD9257

- AD9255

- AD9253

- AD9252

- AD9251

- AD9246S

- AD9231

- AD9230

- AD9228

- AD9222

- AD9219

- AD9212

- AD9211

- AD9204

- AD9277

- AD9278

- AD9279

- AD9284

- AD9268

- AD9484

- AD9600

- AD9608

- AD9609

- AD9628

- AD9629

- AD9633

- AD6672

- AD9649

- AD6657

Documentation & Resources

-

Visual Analog5/12/2015

-

High Speed ADC USB FPGA Evaluation Kit, EVALC10/29/2014PDF2M

-

AN-878: High Speed ADC SPI Control Software (Rev. A)3/20/2018PDF585 kB