JESD204シリアル・インターフェース

JESD204シリアル・インターフェースとJEDEC規格データ・コンバータ

JESD204およびJESD204B改正データ・コンバータ・シリアル・インターフェース規格は、高速データ・コンバータとFPGA(フィールド・プログラマブル・ゲート・アレイ)などの他のデバイス間のデータ入出力を規格化し、その数を減らすためにJEDEC委員会によって作成されました。相互接続の数が少ないため、レイアウトが簡素化され、システム全体の性能に影響を与えることなく、より小型の形状を実現できます。これらの特性は、無線インフラ(GSM、EDGE、W-CDMA、LTE、CDMA2000、WiMAX、TD-SCDMA)トランシーバ・アーキテクチャ、ソフトウェア無線、携帯型計測器、医療用超音波機器、レーダーやセキュア通信などの軍事/航空アプリケーションなど、さまざまな高速ADCアプリケーションのシステム・サイズとコストの制約に対処するために重要となります。アナログ・デバイセズは、JEDEC JESD204規格委員会のオリジナル参加メンバーであり、当社のお客様がこの重要なインターフェースのブレークスルーを十分に活用できるよう、規格に準拠したデータ・コンバータ技術とツール、および包括的な製品ロードマップを同時に開発してきました。

JESD204インターフェース・フレームワーク

アナログ・デバイセズのJESD204インターフェース・フレームワークは、性能最適化IPフレームワークを提供することで、システム開発を簡素化することを目的としたシステム・レベルのソフトウェアとHDLのパッケージです。IPフレームワークは、高速コンバータ、トランシーバ、クロックなどの複雑なハードウェアをさまざまなFPGAプラットフォームに統合できます。

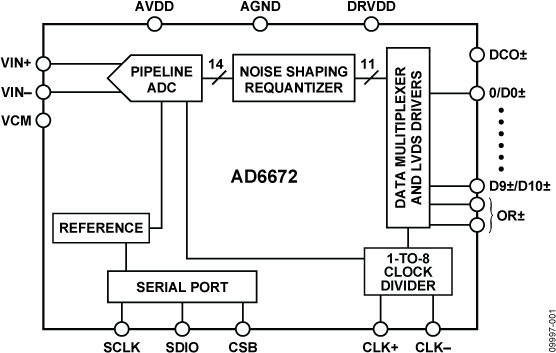

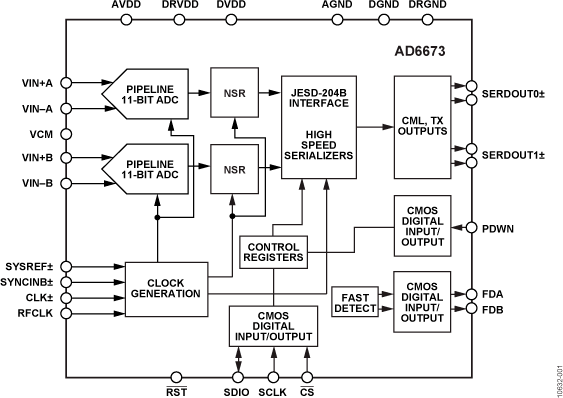

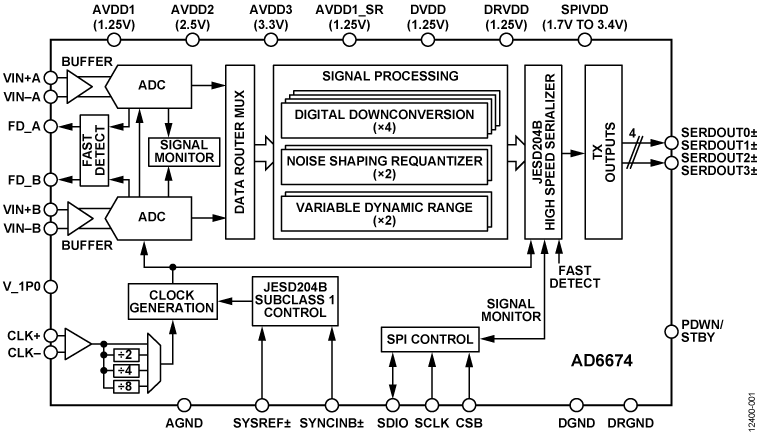

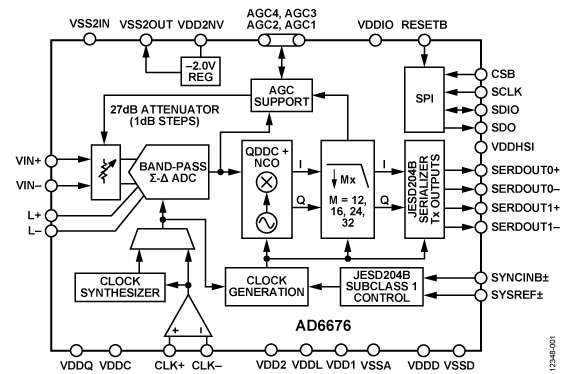

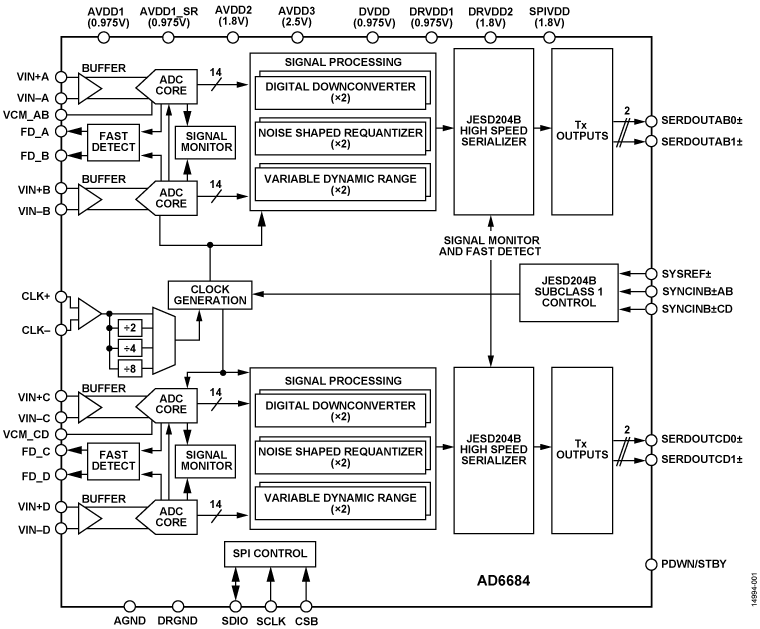

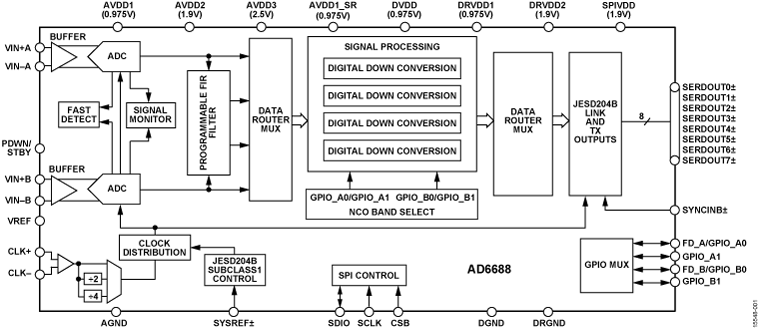

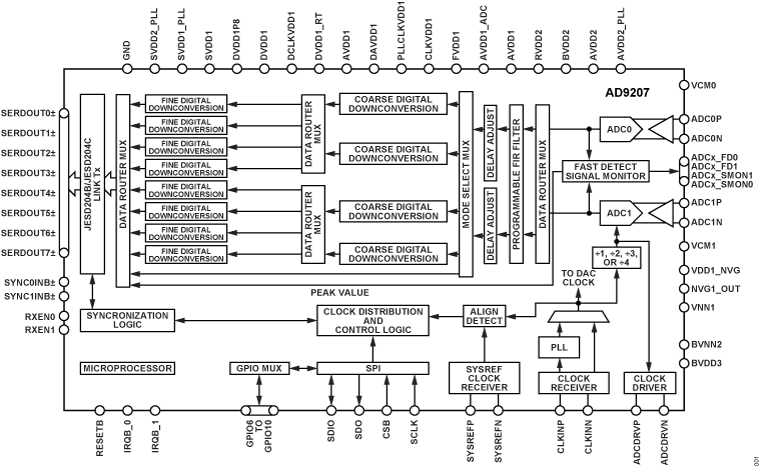

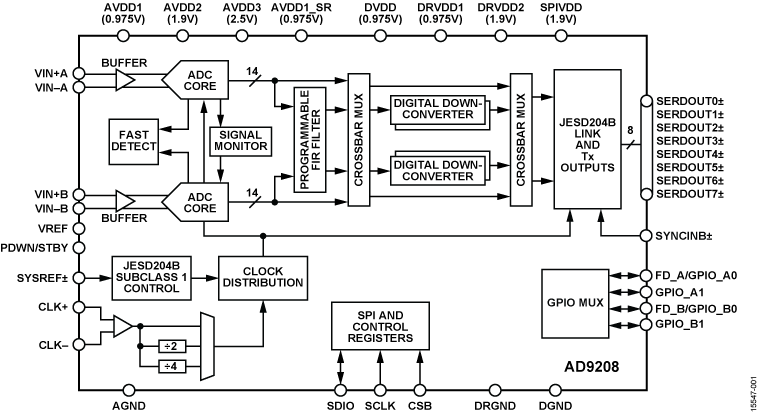

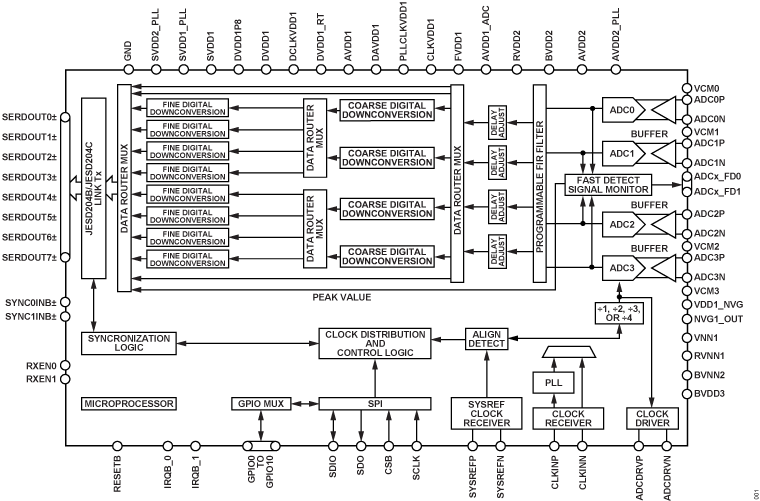

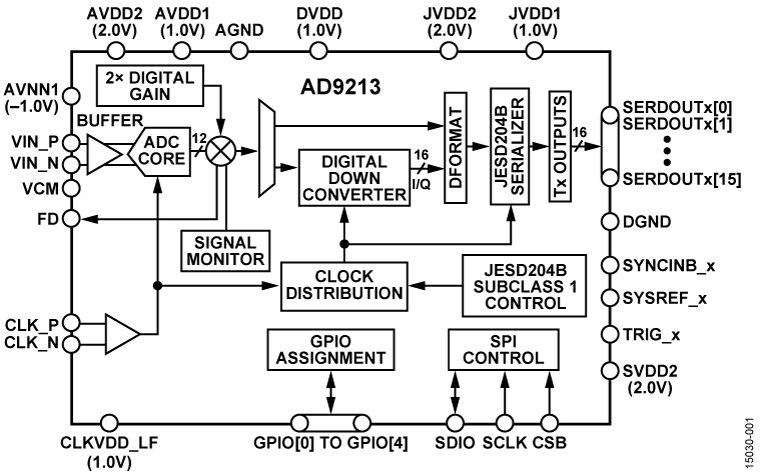

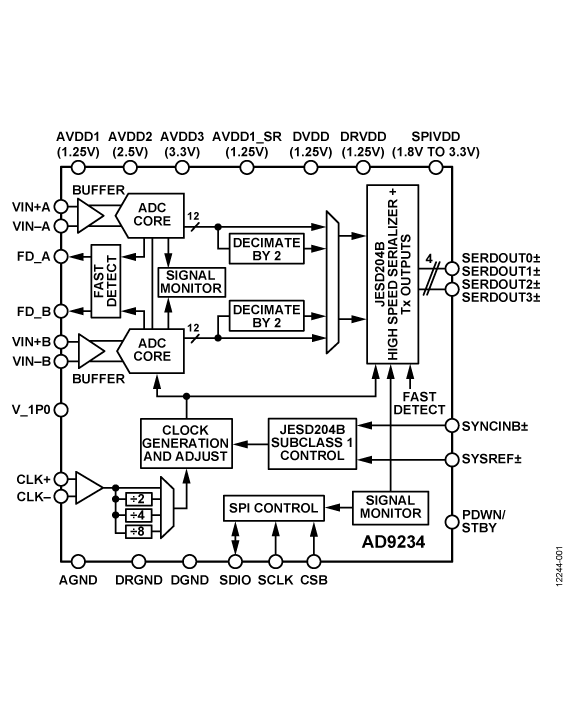

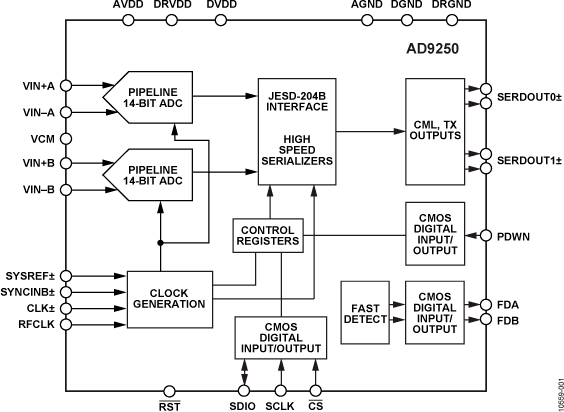

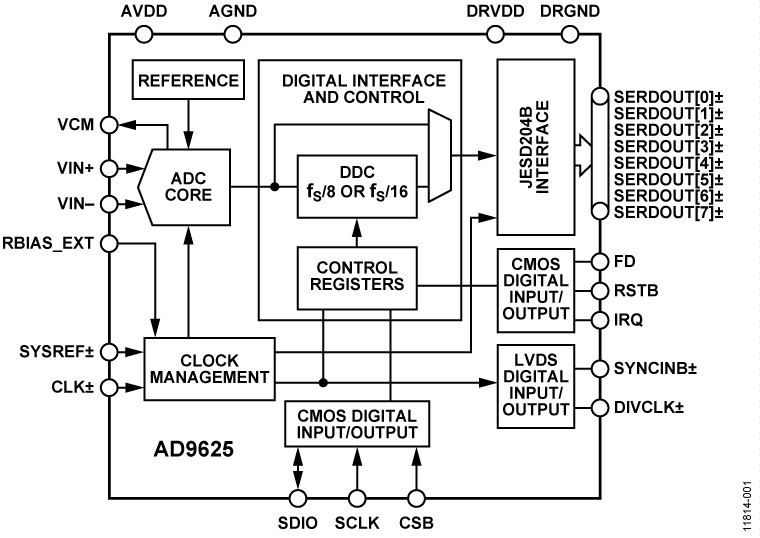

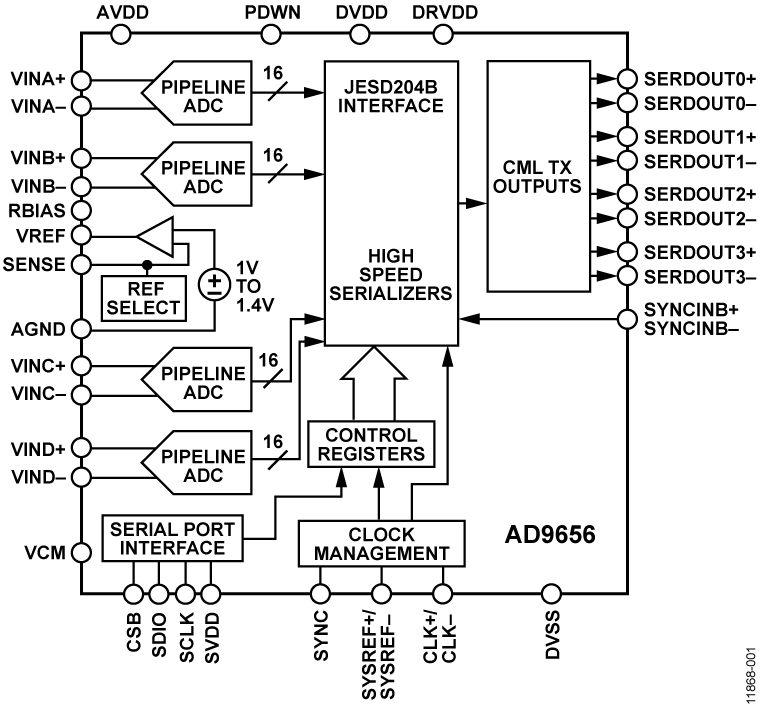

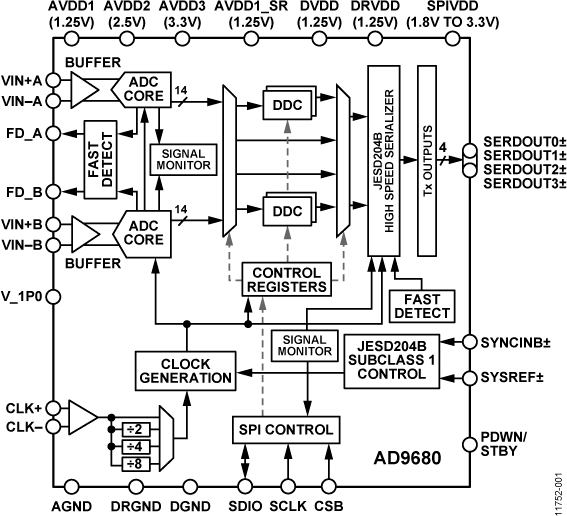

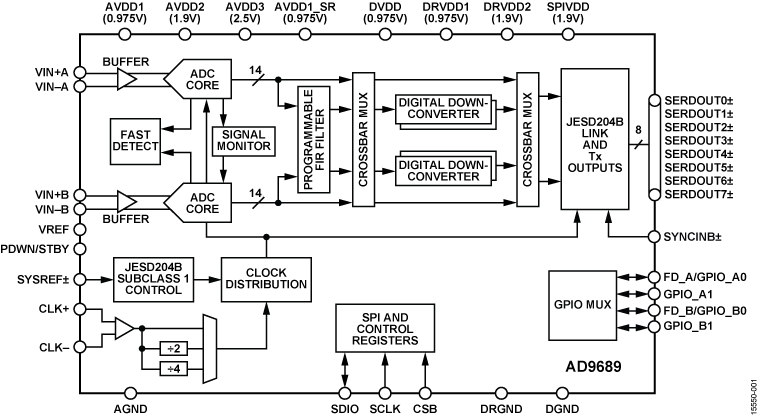

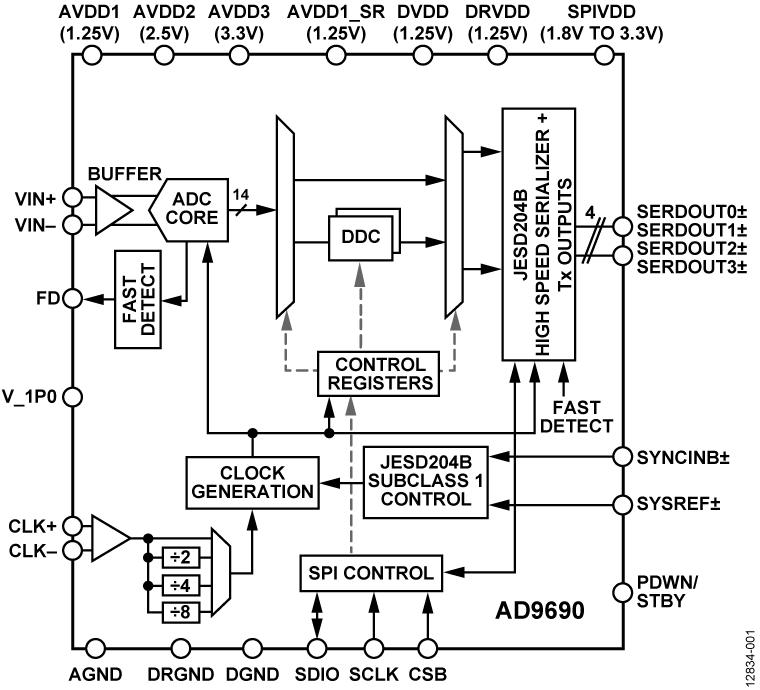

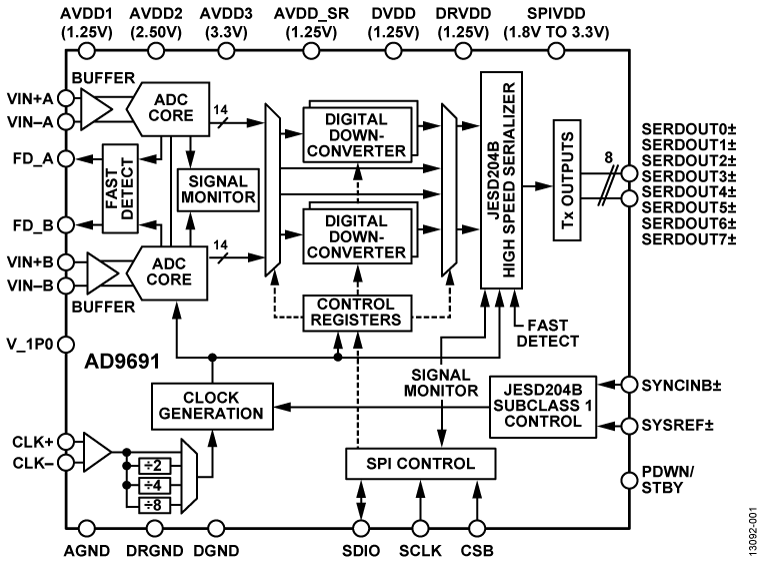

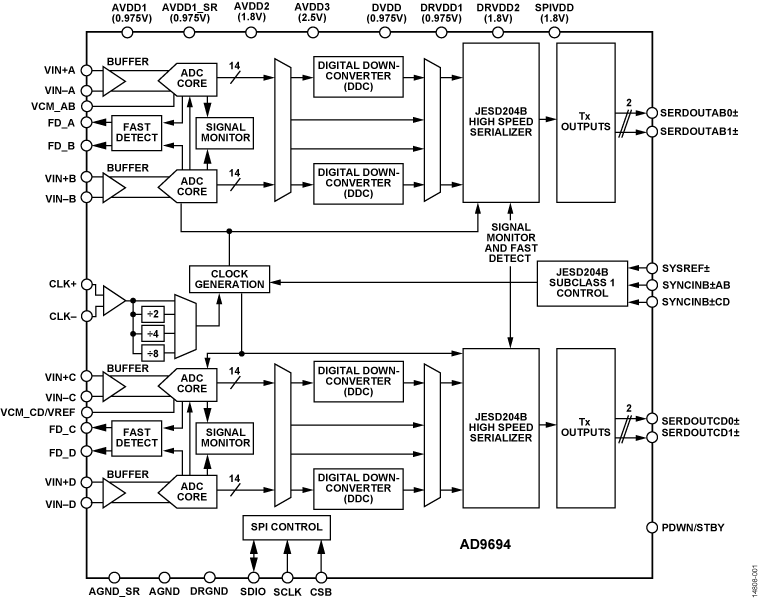

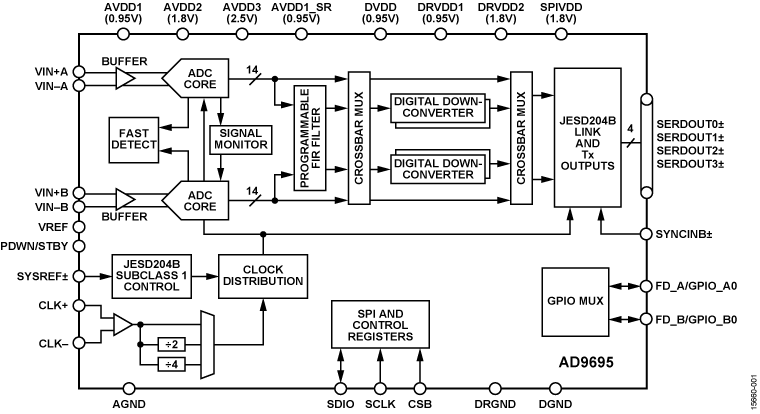

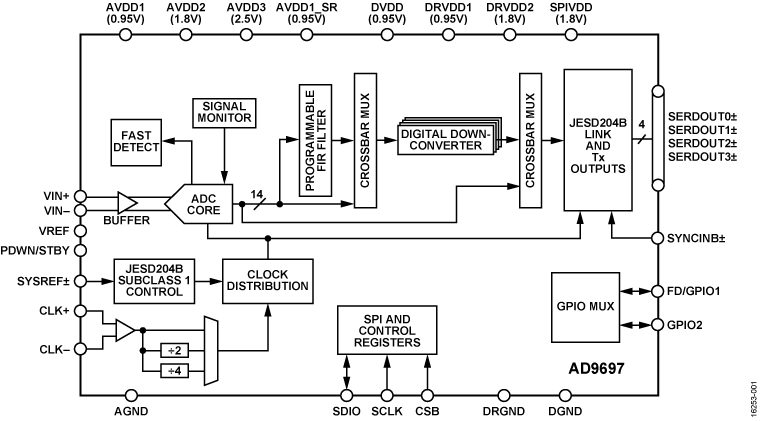

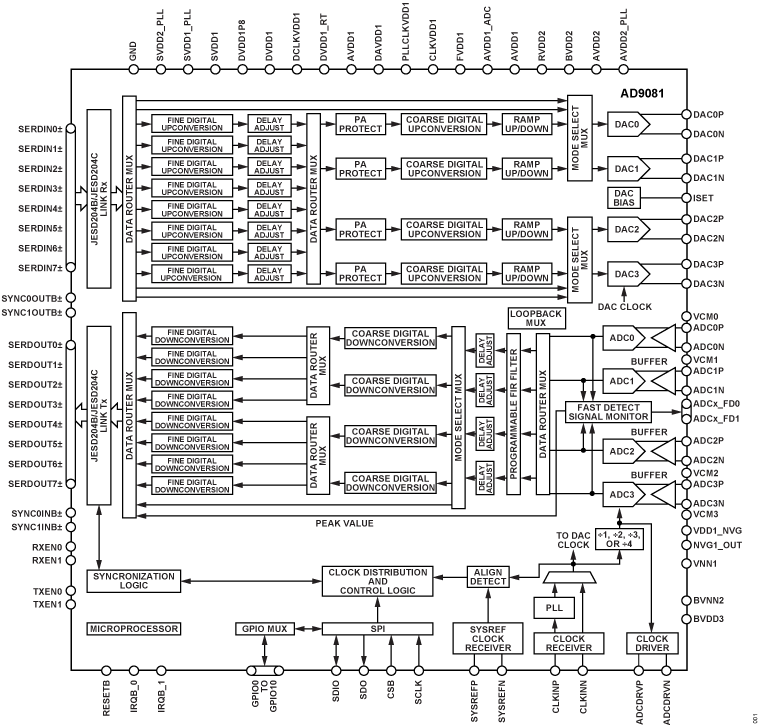

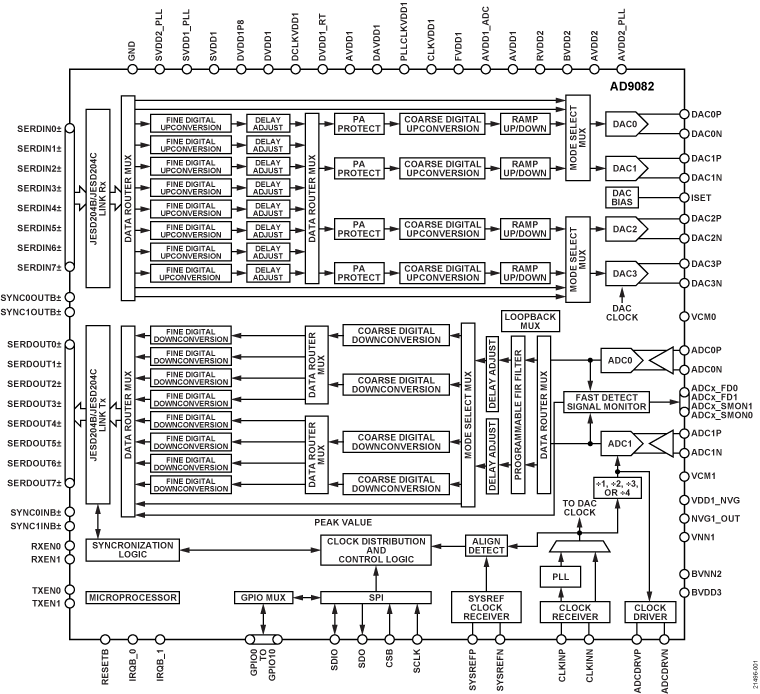

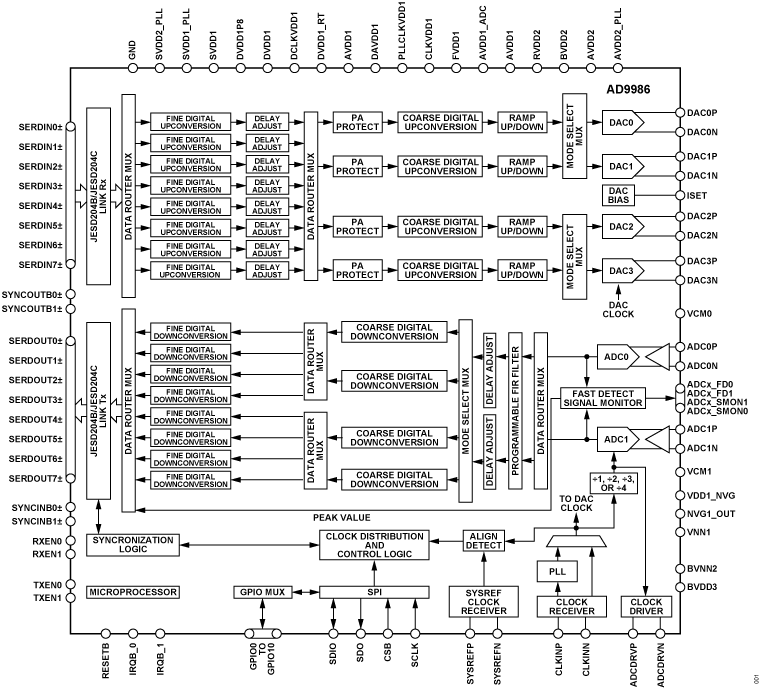

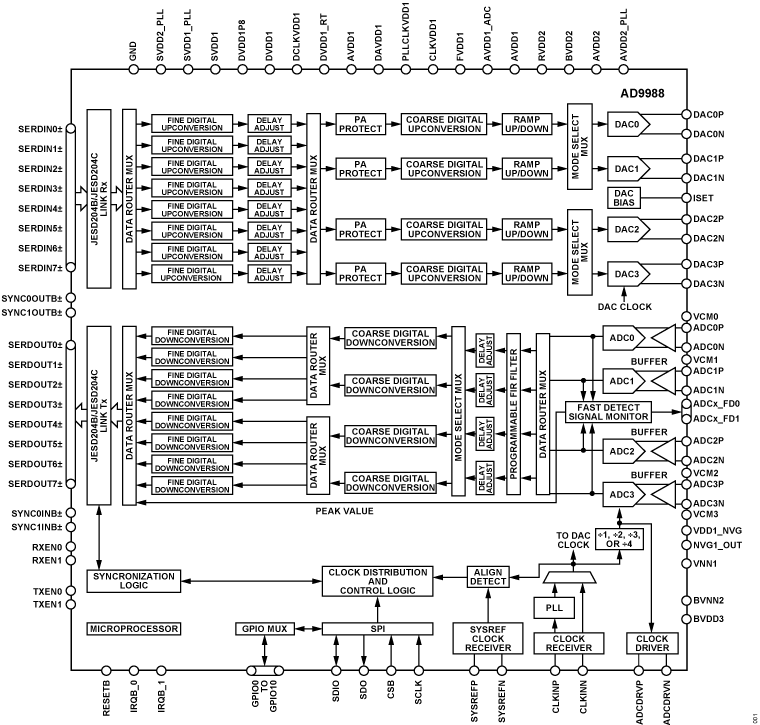

高速ADCおよびIF/RFレシーバ製品 (22)

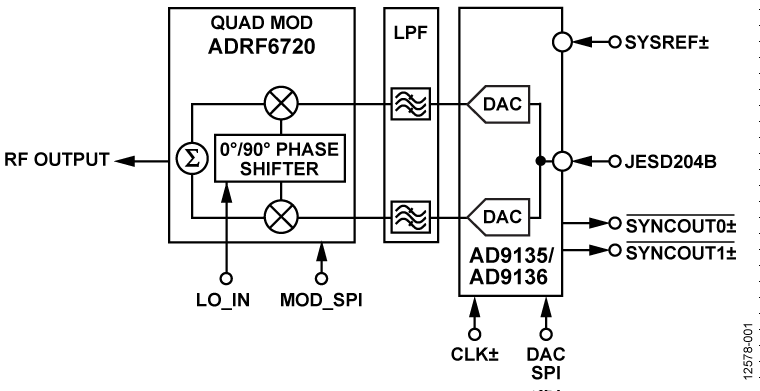

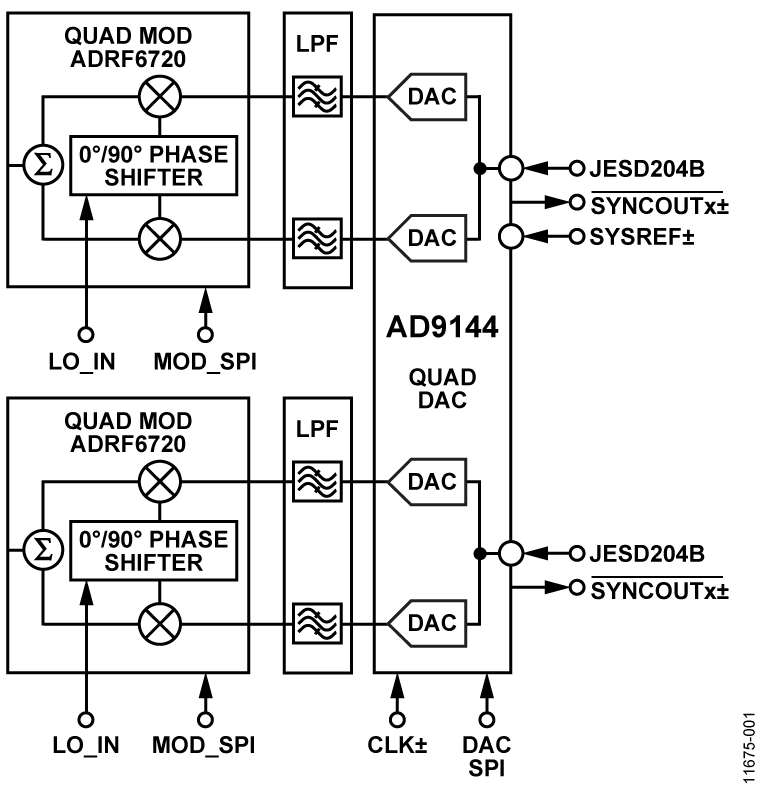

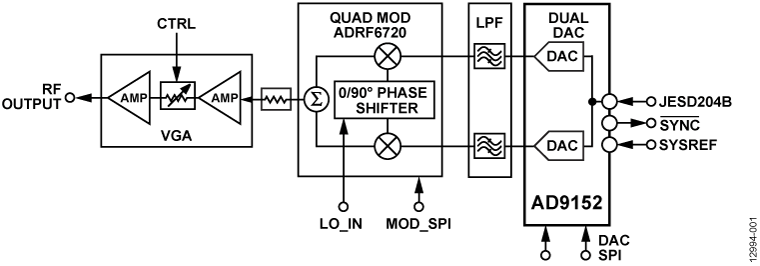

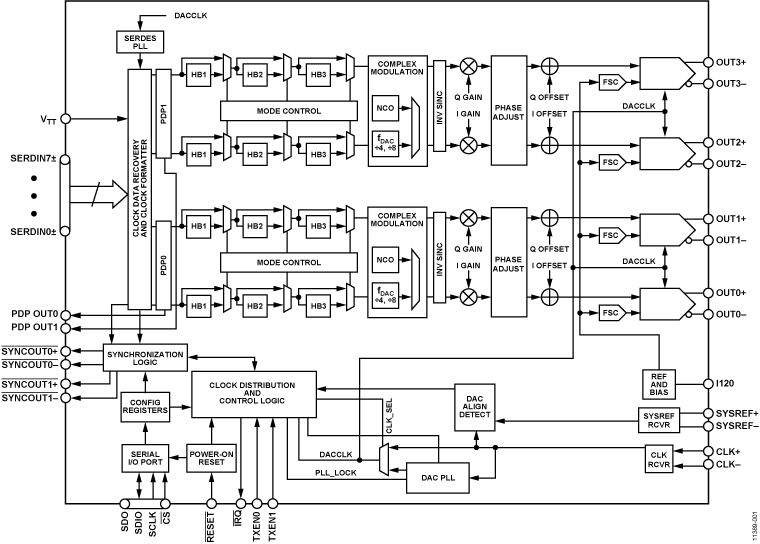

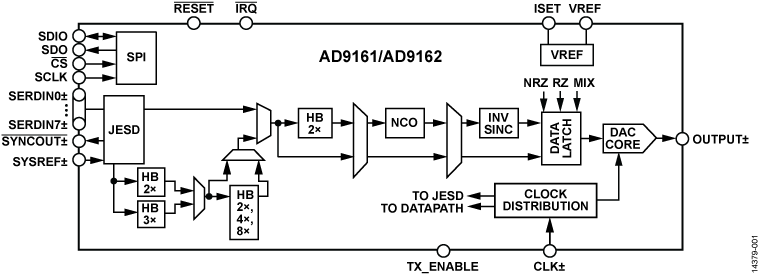

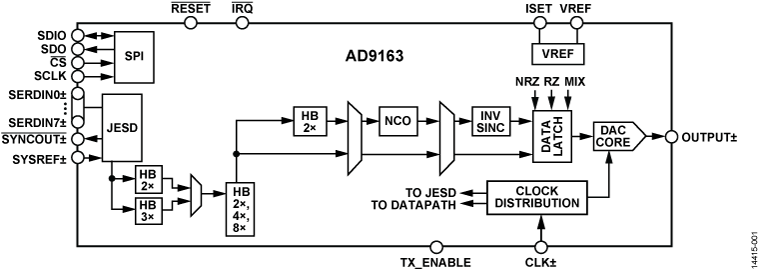

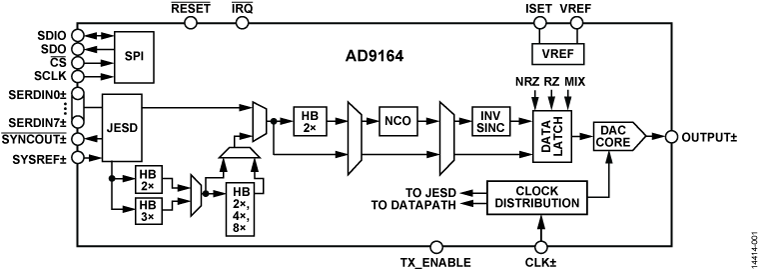

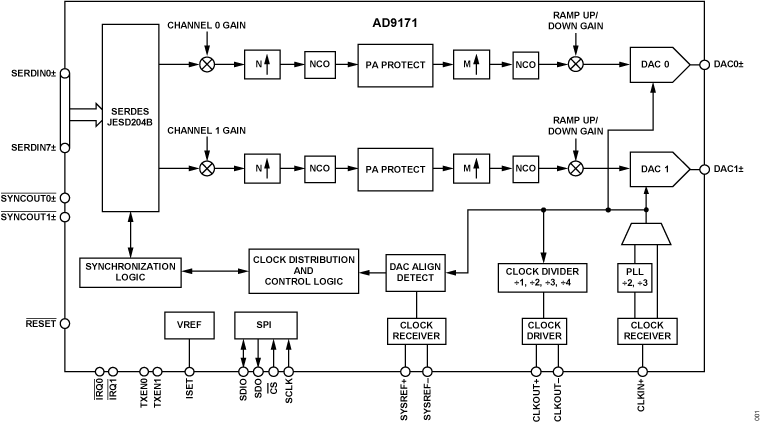

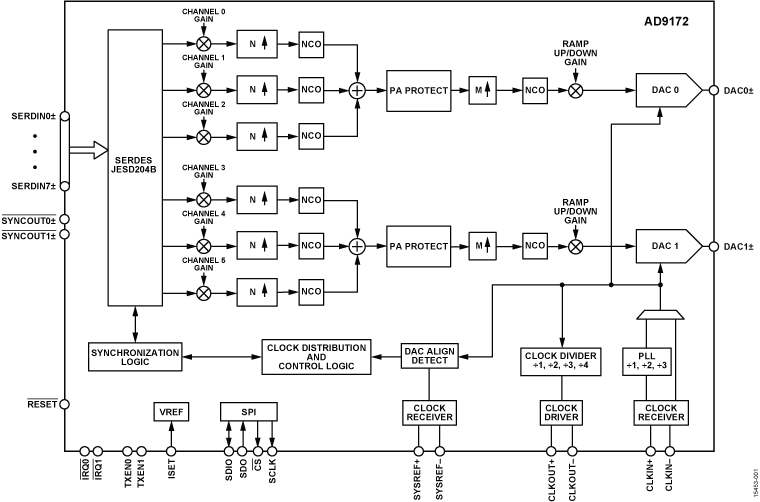

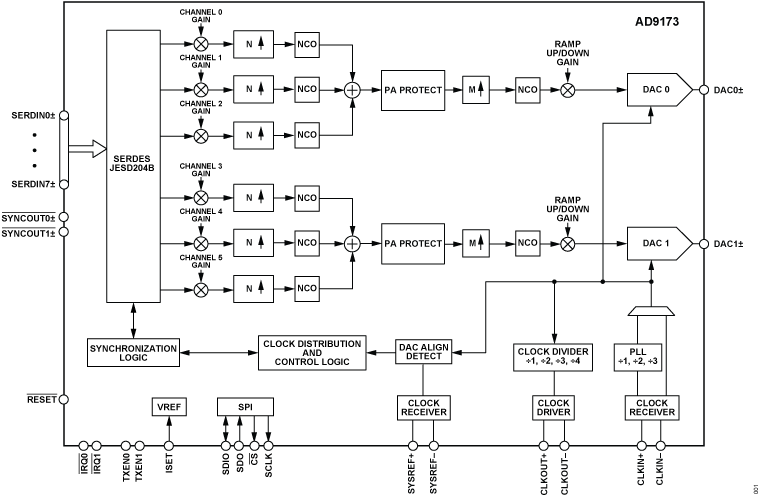

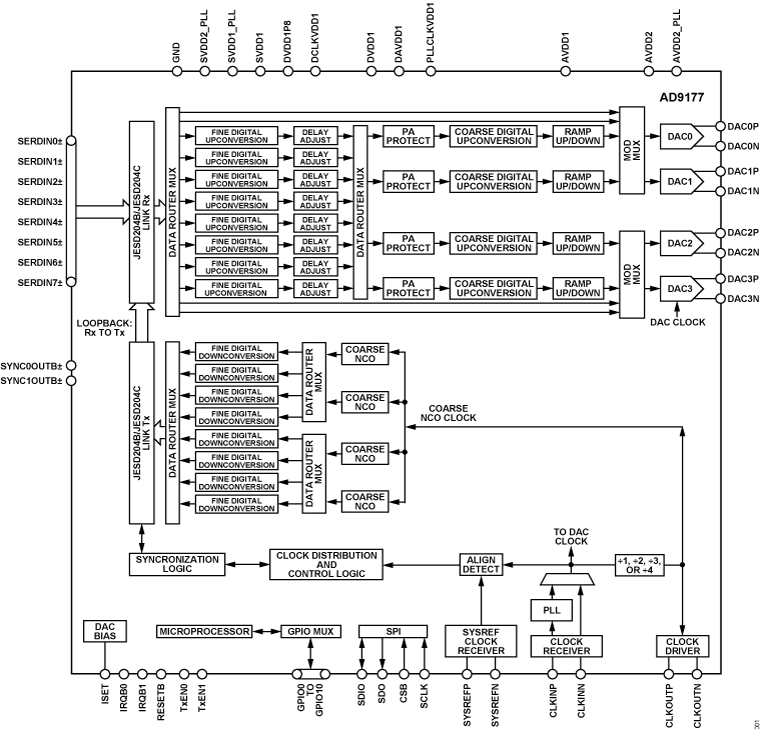

高速DAC製品 (13)

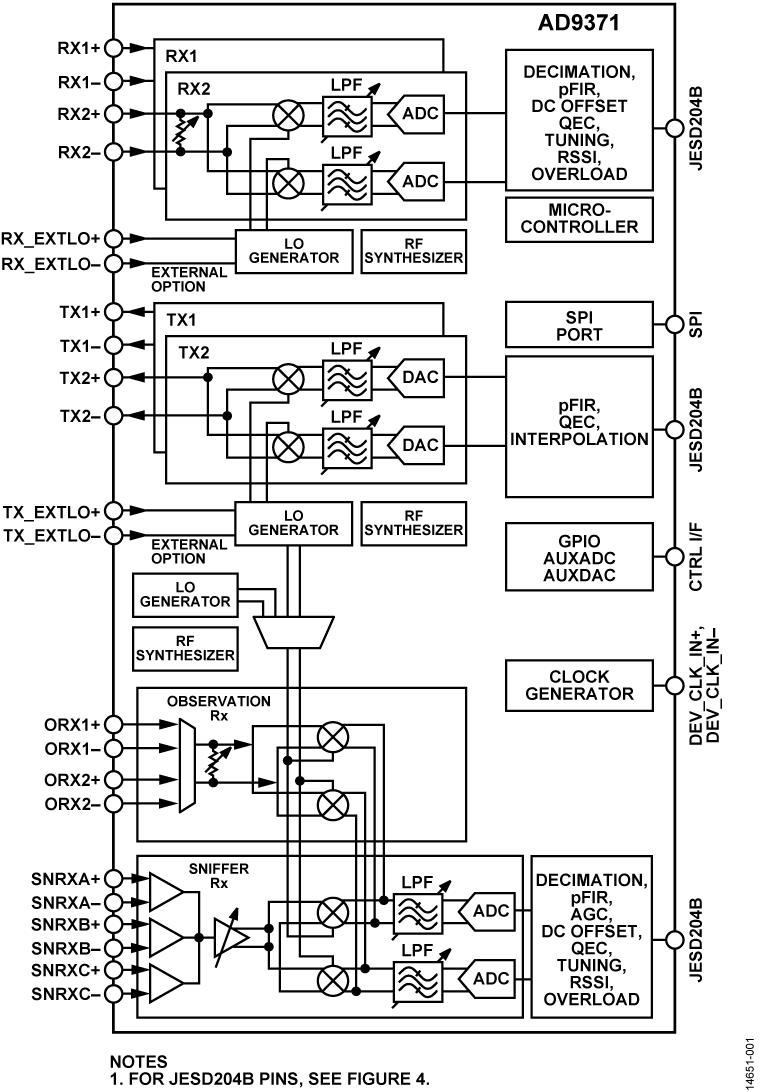

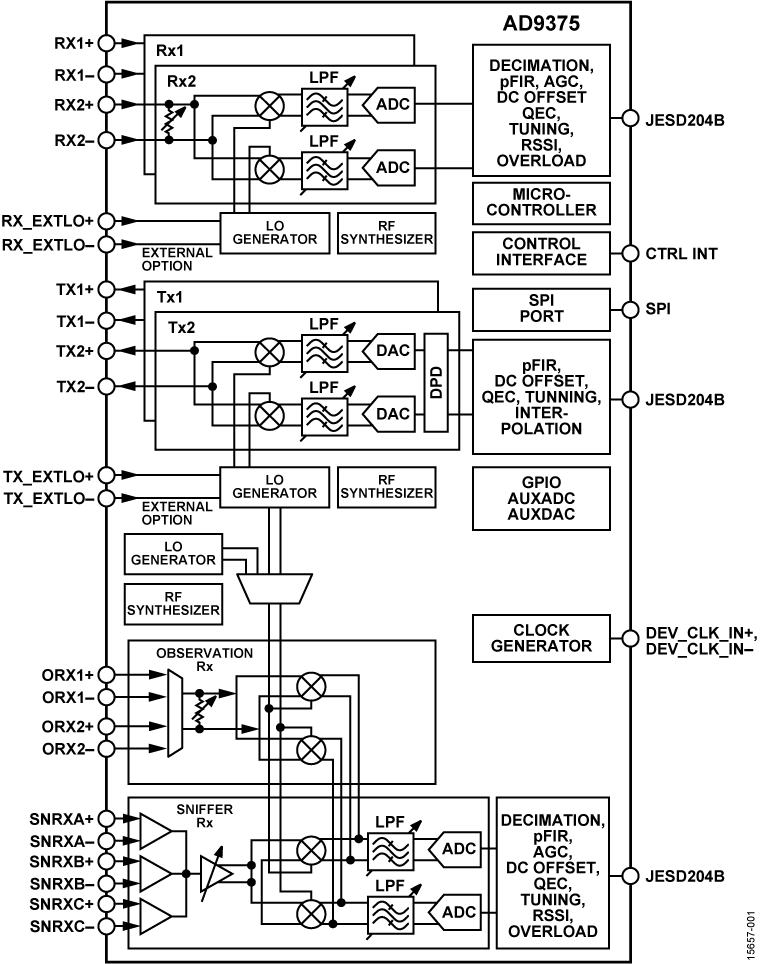

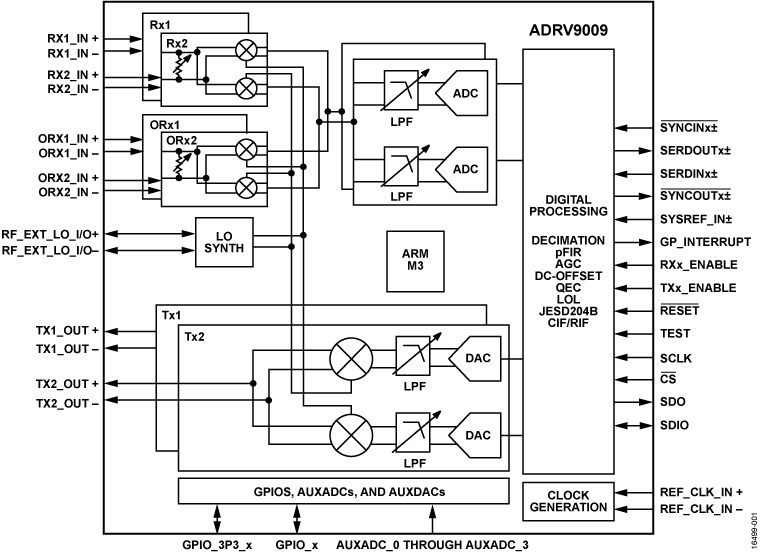

RFトランシーバ製品

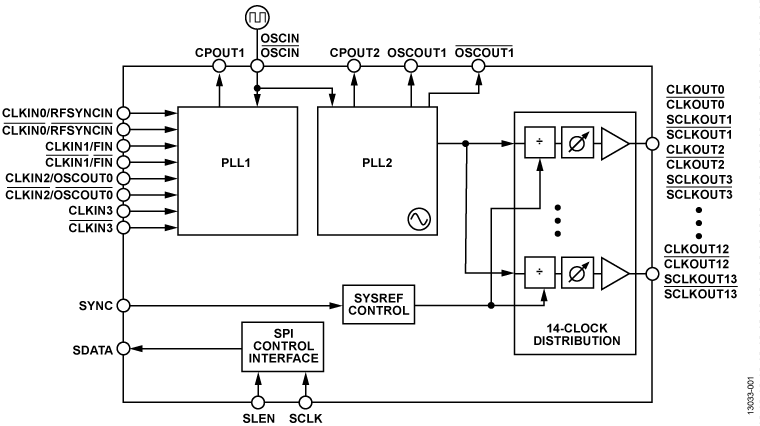

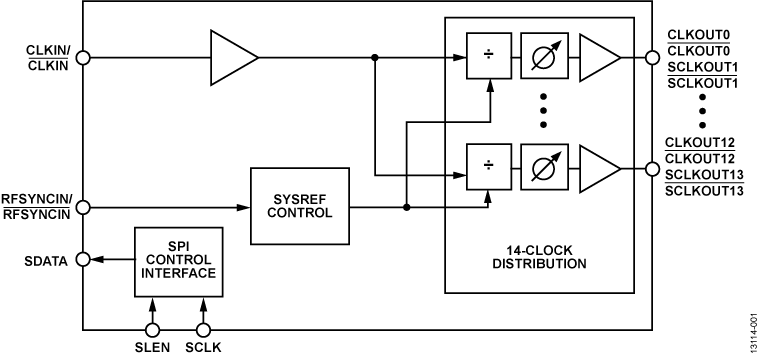

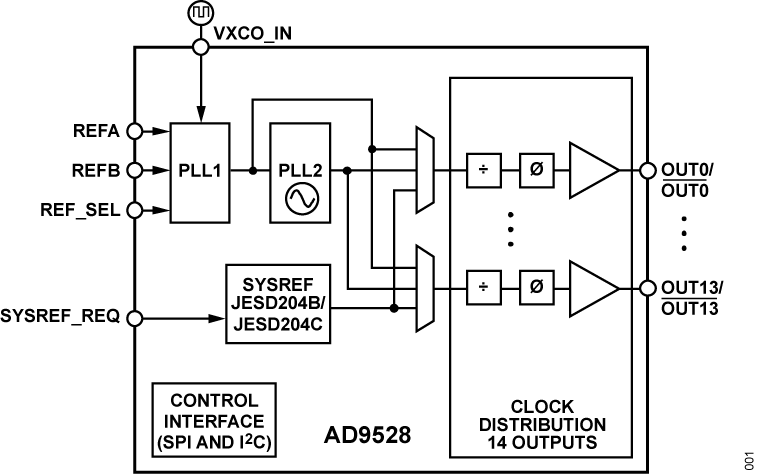

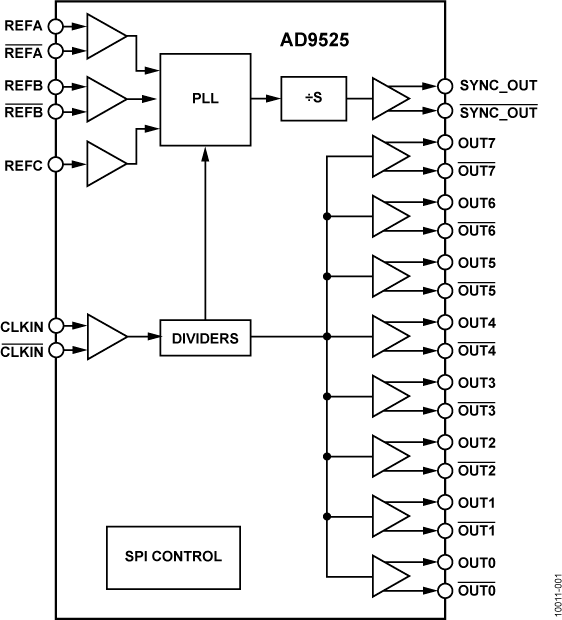

クロック製品

最新情報

評価用ソフトウェア

ウェブキャスト

- Streamlining Flexible System Design using RF ADCs with DSP

- JESD204B Link Debugging Guidelines

- Designing Wideband Frontends for GSPS Converters

- ADI Clocks: Optimizing and Supporting JESD204B Interfaces

- 高性能GSPSデータ・コンバータによるレーダー/EWアーキテクチャの改善

- Demystifying the JESD204B High-Speed Data Converter-to-FPGA Interface

技術記事

- Understanding JESD204B Link Parameters

- JESD204B サバイバル・ガイド 2017 PDF

- MS-2503: JESD204Bによるシステム問題の解決 PDF

- Understanding Layers in the JESD204B Specification: A High Speed ADC Perspective, Part 2

- Prototyping Systems: JESD204B Converters and FPGAs

- Why there's no need to fear JESD204B

- Pair The Right JESD204B Converter With Your FPGA

- Synchronize Multiple ADCs With JESD204B

- Link Synchronation and Alignment in JESD204B: Understanding Control Characters

- LVDS Is Dead? Long Live LVDS & JESD204b

- JESD204B: Critical Link In The FPGA-Converter Chain

- Kick Start Your Designs with JESD204B

- Faster JESD204B Standard Presents Verification Challenges

- What is JESD204 and why should we pay attention to it?

- Understand the digital-output options for high-speed ADCs

- The JESD204/A/B Standard – "Where the Rubber Meets the Road"

ビデオ

- AD-FMCDAQ2-EBZ ワイドバンド RF DAQ ラピッド プロトタイピング FMC モジュール

- High Speed ADC FMC Development Board with JESD204B

- JESD204B and Why It Should Matter to You (Part 1 of 3)

- Rapid JESD204B Data Converter-to-FPGA Prototyping (Part 2 of 3)

- Implementing JESD204B A/D Converters-to-FPGA Designs (Part 3 of 3)

- Rapid Prototyping with JESD204B using FMC and Xilinx FPGAs

- A Look at the JESD204B Serial Interface EYE Diagram

FPGA相互運用性レポート

- Intel AN-927 (AD9081/AD9082 Rx Path JESD204C Interoperability with Stratix 10)

- AD9217 and Intel Stratix 10 Interoperability report and Reference Design

- Intel AN-916 (AD9081/AD9082 JESD204C Interoperability with Stratix 10)

- AD9213/Stratix 10 Interoperability Report

- Intel AN-915 (AD9208/AD9689/AD9694/AD9695, Stratix 10)

- Intel AN890 - AD917x/Stratix10 JESD204B Interoperability Report

- PolarFire FPGA and AD9371 Interoperability Testing

- ComCores JESD204B IP and AD9152 Interoperability Report

- Validating ADI Converters Inter-operability with Xilinx FPGA and JESD204B/C IP PDF

- JESD204B Interoperative Report (AD9250 Xilinx Kintex7)