AD9088

新規設計に推奨Apollo MxFEオクタル16ビット16GSPS RF DACおよびオクタル12ビット8GSPS RF ADC

- 製品モデル

- 1

- 1Ku当たりの価格

- 最低価格:$2695.00

製品情報

- 設定変更可能なミックスド・シグナル・プラットフォーム設計

- 8個ずつの16ビットRF DACと12ビットRF ADC(8T8R)

- 使用可能RFアナログ帯域幅:最大16GHz

- 高速AGC用の低遅延・高速検出

- スペクトラム・スニファおよびモニタ

- 低速AGC用の信号モニタ

- 複数ループバック(ADCからDAC)

- パワー・アンプ後段の保護回路

- 最大DAC/ADCサンプル・レート:16GSPS/8GSPS

- 汎用デジタル機能

- 最大瞬時帯域幅:チャンネルあたり3.2GHz(6T6R)または2.7GHz(8T8R)

- ADCおよびDACの最大サンプル・レートでプログラム可能なFIRフィルタ

- 設定変更可能な微調整および粗調整DDC/DUC

- プロファイルによる高速周波数ホッピング

- SPI、HSCI、GPIO、または外部トリガ(TRIG)を通じた動的設定

- JESD204BおよびJESD204C:20Gbpsおよび28.21Gbps

- 温度モニタリング・ユニット内蔵

- パッケージ:24mm × 26mm、0.80mmピッチの899ボールBGA_ED

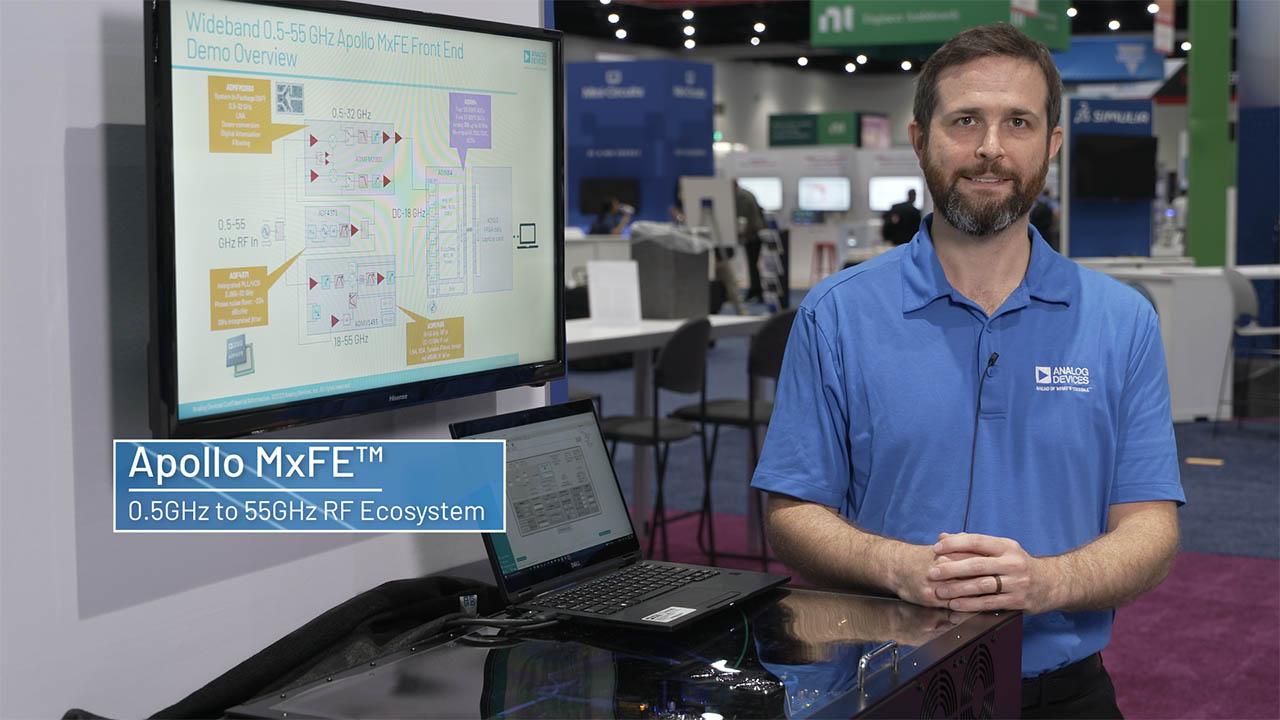

このミックスド・シグナル・フロントエンド(Apollo MxFE)は、16ビットで最大サンプル・レートが16GSPSのRF D/Aコンバータ(DAC)コア、および12ビットで最大サンプル・レートが8GSPSのRF A/Dコンバータ(ADC)コアを内蔵した高集積デバイスです。AD9088は、8つのトランスミッタ・チャンネルと8つのレシーバ・チャンネルをサポートしており、広範な瞬時帯域幅の信号を処理するために広帯域のADCとDACが必要なアプリケーションに最適です。本デバイスは、48レーンの28.21Gbps JESD204Cまたは20Gbps JESD204Bデータ・トランシーバ・ポート、オン・チップ・クロック逓倍器、およびデジタル・シグナル・プロセッサ(DSP)機能を搭載し、広帯域またはマルチバンドのDC~RFアプリケーションを対象としています。また、DSPデータパスをバイパスしてADCまたはDACコアの全帯域幅を使用できるバイパス・モードを備えています。更に、フェーズド・アレイ・レーダー・システムと電子戦アプリケーションを対象とした低遅延ループバック・モードと周波数ホッピング・モードも備えています。

AD9088は、24mm × 26mmの899ボールBGA_EDに収められ、−40°C~+110°Cのジャンクション温度範囲で動作できます。

アプリケーション

- レーダーおよびフェーズド・アレイ・システム

- シーカ・フロント・エンド

- 戦術防衛無線インフラストラクチャ

- 電子戦およびシグナル・インテリジェンス

- ワイヤレス通信インフラストラクチャ

- ワイヤレス通信テスト(5Gミリ波、5G Cバンド、バックホール)

ドキュメント

データシート 1

ユーザ・ガイド 2

アプリケーション・ノート 1

技術記事 21

ビデオ 27

FPGA相互運用性レポート 5

製品選択ガイド 1

サードパーティ・ソリューション 1

デバイス・ドライバ 3

アナログ・ダイアログ 3

ウェブキャスト 2

ビデオ・シリーズ 1

| 製品モデル | ピン/パッケージ図 | 資料 | CADシンボル、フットプリント、および3Dモデル |

|---|---|---|---|

| AD9088BBPZ-MX-SE-SW5 | BGA_ED |

これは最新改訂バージョンのデータシートです。

ソフトウェア・リソース

API Device Drivers 1

Device Application Programming Interface (API) C code drivers provided as reference code that allows the user to quickly configure the product using high-level function calls. The library acts as an abstraction layer between the application and the hardware. The API is developed in C99 to ensure agnostic processor and operating system integration. Customers can port this application layer code to their embedded systems by integrating their platform-specific code base to the API HAL layer.

To request this software package, go to the Software Request Form signed in with your MyAnalog account and under “Target Hardware” select “High Speed Data Converters” and choose the desired API product package. In addition, there are two SW packages available specifically for Apollo MxFE™. There is a PyApp/ACE evaluation package and there are FPGA bin files supporting various use cases. You will receive an email notification once the software is provided to you.

デバイス・ドライバ 4

評価用ソフトウェア 2

JESD204x Frame Mapping Table Generator

The JESD204x Frame Mapping Table Generator tool consists of two Windows executables that will allow the user to input any valid combination of JESD204x parameters (L, M, F, S, NP) in order to output a .csv file that illustrates the frame mapping of the JESD204x mode in table format. There is an executable that allows the user to input a single JESD204x mode and another, that allows the user to input the parameters for multiple JESD204x modes in a specified .csv format in order to output a .csv file that illustrates the frame mapping of each of the JESD204x modes that were input into separate tables.

ハードウェア・エコシステム

| 製品モデル | 製品ライフサイクル | 詳細 |

|---|---|---|

| スイッチング・レギュレータ & コントローラ 3 | ||

| LT8627SP | 新規設計に推奨 | 18V/16A超低ノイズリファレンス内蔵降圧Silent Switcher®(サイレント・スイッチャ)3 |

| LTM4702 | 新規設計に推奨 | 16VIN、8A超低ノイズ、Silent Switcher®(サイレント・スイッチャ)μModuleレギュレータ |

| LTM8074 | 新規設計に推奨 | 40 VIN、1.2 A Silent Switcher ®(サイレント・スイッチャ) µモジュール・レギュレータ |

| パワー・システム・マネージメント(PSM) & シーケンサ 1 | ||

| LTC2977 | 新規設計に推奨 | 正確な出力電圧測定を特長とする8チャネルPMBusパワーシステム・マネージャ |

| リニア・レギュレータ 2 | ||

| LTM4709 | 新規設計に推奨 | 設定可能な出力アレイを備えた、トリプル3A、超低ノイズ、高PSRR、超高速のμModuleリニア・レギュレータ |

| LT3094 | 新規設計に推奨 | −20 V、500 mA、超低ノイズ、超高 PSRR、負電圧のリニア電圧レギュレータ |

ツールおよびシミュレーション

周波数折り返しツール

このツールは、ADCのデジタル化における入力信号とその高調波のエイリアシング効果を可視化します。シングル・トーン信号か変調搬送波入力信号を選び、最大10のナイキスト領域におけるエイリアシングを確認することができます。

ツールを開くコヒーレント・サンプリング計算ツール

コヒーレント・サンプリング周波数およびコヒーレント入力周波数を計算します。

ツールを開くSNR/THD/SINAD 計算ツール

SNR、THD、SINADからENOBとノイズを計算によって変換します。また、SNR、THD、またはSINADの1つを他の2つから計算します。

ADIsimPLL™

ADIsimPLLは、アナログ・デバイセズの新しい高性能PLL製品の迅速で信頼性の高い評価を可能にします。これは、現在利用できる最も包括的なPLLシンセサイザ設計およびシミュレーション・ツールです。実施されるシミュレーションには、PLL性能に影響を与える重要な非線形効果がすべて含まれます。ADIsimPLLは、設計プロセスから1回以上の反復作業を削除し、設計から市場投入までの時間を短縮します。

ツールを開くデータ変換計算ツール

有効ビット数、S/N比、信号/ノイズ + 歪み(SINAD)、THDを計算します。

ツールを開くクロックおよびタイミング・ツール

アナログ・デバイセズは、エンジニアが有線および無線ネットワーク向けの重要なクロックおよびタイミングICソリューションを構築できるように、製品ポートフォリオと連携する設計ツールを提供しています。

ツールを開くSパラメータ 1

熱モデル 1

AD9084/AD9088 AMIモデル

AD9084およびAD9088用の設計ファイル・パッケージ。

ツールを開く