概要

アナログ・デバイセズは、ソフトウェア無線向けの最新ソリューションとなるMxFE®(ミックスド・シグナル・フロント・エンド)ファミリの製品を提供しています。その特徴の1つは、7.5GHzという非常に広い帯域幅に対応している点にあります。MxFE製品は、D/Aコンバータ(DAC)とA/Dコンバータ(ADC)のコアをベースとしています。それらで使用するサンプリング・クロックは、MxFE製品が内蔵するフェーズ・ロック・ループ(PLL)または外部のクロック源のうちいずれかによって生成します。どのようなクロック・ソリューションを採用すべきなのかを検討する際には、「ADIsimPLL™」を活用するとよいでしょう。このPLLシンセサイザ用の設計/シミュレーション・ツールを使用すれば、最適なソリューションを容易に見いだせます。ADIsimPLLの現行バージョンでは、MxFEのモデルも利用できるようになりました。そのため、対象とする無線ソリューションに最適な高性能のサンプリング・クロック回路を容易に設計できます。ADIsimPLLでは、主要な性能/仕様に適合するようループ・フィルタを最適化するために、PLLのパラメータを調整することができます。本稿では、同ツールを使用して、MxFEやRFDAC(RF信号に対応可能なDAC)が内蔵するPLLとVCO(Voltage Controlled Oscillator)をモデル化する方法を紹介します。

はじめに

クロックを生成する回路を設計する際には、最適なコンポーネントを選択しなければなりません。それにより、そのクロックを使用するプラットフォームの性能を最大限に引き出すことが可能になります。

クロックを生成する回路を設計/選択する際には、考慮すべき重要な項目があります。それは、位相ジッタと位相ノイズ・フロア(以下、PNフロア)です。これらは、クロックを使用するデータ・コンバータ(ADCやDAC)のS/N比に大きな影響を及ぼします。

本稿で対象とするのは、アナログ・デバイセズのMxFE製品とRFDACである「AD917x」です。それらはすべて、DAC/ADCのサンプリング・クロックを生成するためのものとしてインテジャー型のPLLシンセサイザを集積しています。そのPLL/VCOシンセサイザを使用すれば、入力リファレンスに対してロックされたクロックを生成し、DAC/ADCを動作させることができます。アプリケーションの種類にもよりますが、そのクロックの位相ノイズ/積分ジッタ性能によって十分に要件を満たせるケースも多いでしょう。ただ、一部のアプリケーションでは、内蔵PLL/VCOよりも位相ノイズが小さい外部のクロック源を使用しなければならない可能性があります。ADIsimPLLによって、位相ノイズ/ジッタ性能をモデル化すれば、開発工程の早い段階でそのような判断を下すことができます。

ADIsimPLLを使用すれば、位相ノイズと積分ジッタのシミュレーションを実施し、その結果を即座に取得することが可能です。そのためには、内蔵PLL/VCOのモデルを適切に構成しなければなりません。また、利用する入力リファレンスの特性もモデル化しておく必要があります。MxFE/RFDACが内蔵するチャージ・ポンプの電流値とループ・フィルタ用の外付けコンポーネントについても、ADIsimPLL向けにモデル化しておけば最適な値を決定することができます。候補となるリファレンス源をモデル化し、それをADIsimPLL上で使用すれば、リファレンスのノイズがサンプリング・クロックに及ぼす影響を簡単に確認することができます。その結果、リファレンス・クロックの選定作業が容易になります。

本稿では、ADIsimPLLによって、MxFE製品用のクロック源の設計/シミュレーションを実施する方法を紹介します。MxFE製品の具体的な例としては「AD9081」を取り上げます。つまり、ADIsimPLLでは同ICのモデルを使用します。ただ、すべてのMxFE製品とAD917x(RFDAC)については同じ手順で作業を進められます。本稿では、入力リファレンス周波数が500MHz、VCOの周波数が12GHzのPLLを設計するケースを例にとります。また、500MHzのリファレンス源については、ADIsimPLLで使用可能なモデルの作成方法も紹介することにします。ADIsimPLLでは、それらのモデルを使用することで、サンプリング・クロックの位相ノイズ/rmsジッタの値を簡単に求めることができます。本稿では、そのシミュレーション結果と、MxFE製品の評価用ボードで取得した実測結果の比較も実施します。

MxFE用のサンプリング・クロック回路の設計

ここからは、MxFE用のサンプリング・クロックを生成する回路の設計手順を示していきます。まずは、analog.com/ADIsimPLLからADIsimPLLをダウンロードしてインストールしてください。

インストールが完了したら、ADIsimPLLを起動して設計作業を開始します。

図1. ADIsimPLLの「Welcome」画面

インストールの完了後に図1の画面が表示されたらチュートリアルを閉じます。

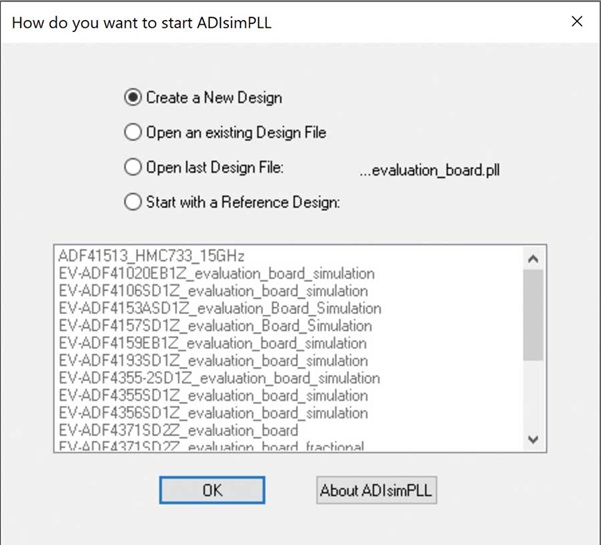

図2. 新規設計の開始

次に表示される画面では「Create a New Design」をチェックし、「OK」ボタンを押します(図2)。

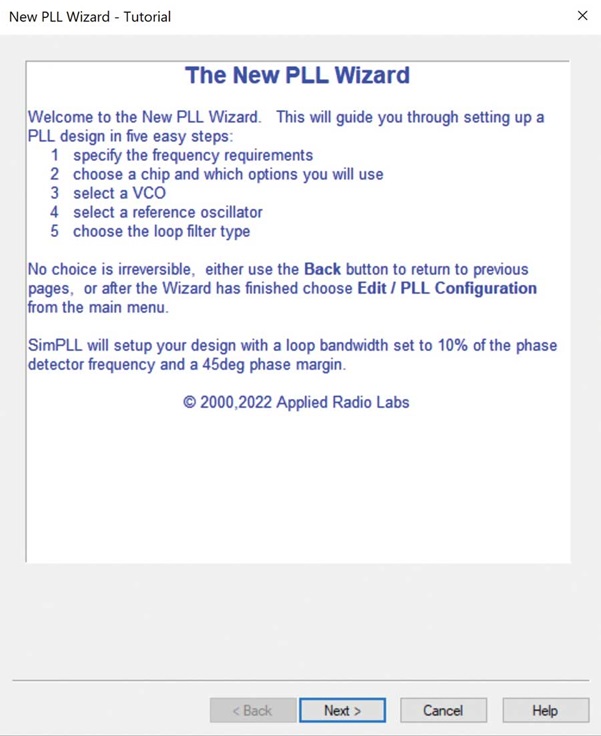

すると、PLLを新規に設計するためのウィザードが表示されます(図3)。ここでは「Next」をクリックしてください。

図3. PLLの新規設計用ウィザード

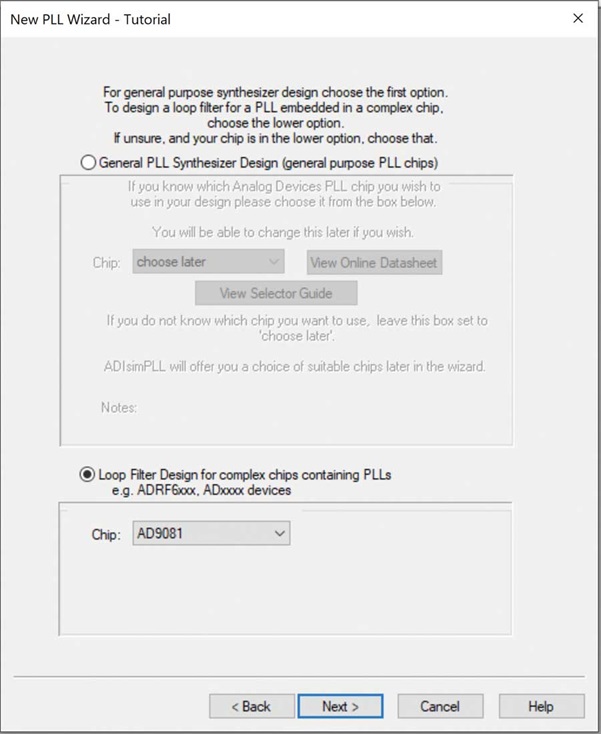

図4. 「AD9081」の選択

次に表示される画面では、「Loop Filter Design for complex chips containing PLLs」を選択します(図4)。

そして、「Chip」のドロップダウン・リストから「AD9081」を選択し、「Next」をクリックしてください。

続いて、AD9081のPLLシンセサイザに関する設定を行います。そのためのものとして、図5に示すようなグラフィカルな設定ページが表示されます。これを見ると、PLLのブロック図、重要なレジスタ、周波数、設計オプションが表示されていることがわかります。このページでは、標準的な一連の設定の中から適切なものを選択することによって作業を進められるようになっています。ただ、レジスタやその他のオプションを直接変更し、満たすべき条件に応じた詳細な設定を行うことも可能です。

表示されている回路図には、緑色の枠で囲まれたボックスが存在します。それらについては直接データを入力できるようになっています。その値に応じ、他のセルの値も自動的に更新されます。また、カウンタの値は、セルの上にカーソルを合わせてマウス・ホイールを操作することで変更できます。各種のオプションについては、ドロップダウン・リストを使用することで選択を行うことが可能です。なお、周波数とレジスタの制限値はリアルタイムにチェックされます。制限値を外れた場合、エラー・メッセージが表示されると共に、問題のある個所の表示が赤色に変わります。

図5. AD9081用のPLLの設定画面

ここでは、fDAC = 12GHzという条件でシミュレーションを行ってみます。そのために、緑色の「DACCLK Freq」のボックスの値を12GHzに変更してください(図6)。「CLK IN Freq」のデフォルトの値は500MHzになっているはずです。

図6. fDACの値の変更

この状態で「Next」をクリックすると、図7の画面が表示されます。

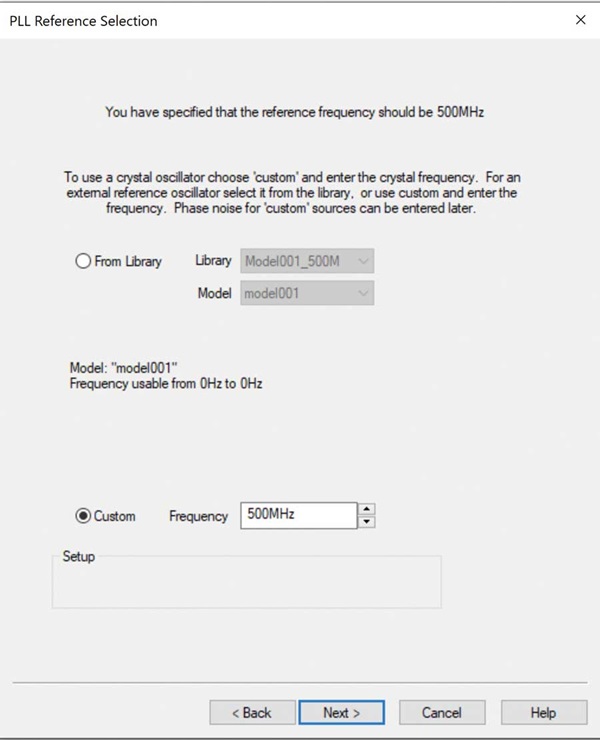

図7. PLL用のリファレンスの選択画面

CLKINにリファレンスとして入力する信号については、発振器の特性を反映させることができます。位相ノイズの実測データを使用したい場合には、「Reference Library Editor」によってモデルを作成し、それをライブラリ・ファイルとして保存します。そうすれば、そのモデルを「From Library」で選択できるようになります。このエディタの詳しい使用方法については、後ほど「ADIsimPLLでリファレンスのモデルを作成する」のセクションで説明します。

ここでは、図7の「Next」をそのままクリックしてください。すると、PLLの設定画面が表示されます(図8)。

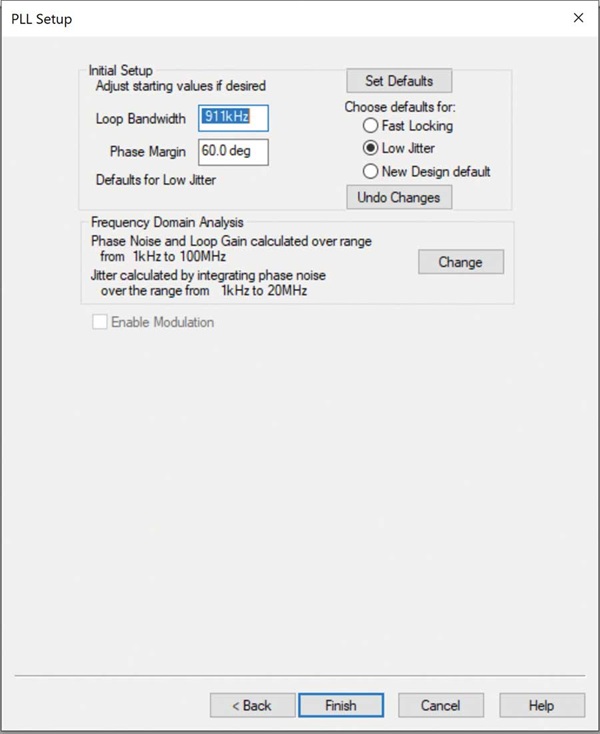

図8. PLLの設定画面

図8の画面では、「Fast Locking」または「Low Jitter」を選択して「Finish」ボタンをクリックします。

すると、図9の画面が表示されます。これは、PLLシンセサイザの設計に関する情報を示すための「Report」タブです。この画面には、12GHzを選択した場合の周波数領域の解析結果と、ブリック・ウォール・フィルタを使用した場合の位相ジッタの値が表示されます。画面の最下部にはいくつかのタブが用意されています。具体的には、このPLLシンセサイザのモデルに関連して、「Components」、「FreqDomain」、「Schematic」、「DACn」というタブが表示されます。いずれかを選択すれば、各タブに直接移動します。

図9. 「Report」タブ

ここでは「Components」タブを選択してみましょう。すると、図10の画面が表示されます。この画面では、解析の対象とする周波数(12GHz)におけるVCOの位相ノイズとリファレンスの位相ノイズの特性を確認できます。上側のグラフに示されているのは、自走設定(PLL内に含まれていないアンロックの状態)で測定されたVCOの位相ノイズの値です。PLL内でVCOがロックされている場合、PLLのループ帯域幅に含まれる周波数では出力位相ノイズが大きく低減されます。下側のグラフに示されているのは、リファレンス源の位相ノイズの特性です。リファレンスの位相ノイズは、主にループ帯域幅内ではPLLの出力位相ノイズに大きな影響を及ぼします。

図10. 「Components」タブ

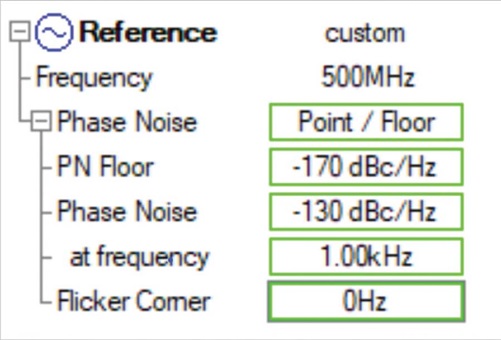

デフォルトでは、リファレンスの位相ノイズは「None」としてモデル化されています。リファレンスのノイズの値を変更するには、画面左のデータ・パネルに用意されている「Reference」を使用します(図11)。この「Reference」フォルダを開き、「Phase Noise」を「None」から別の設定に変更してください。選択肢としては、「Point/Floor」、「Corner/Floor」、「Leeson」が用意されています。図11では「Point/Floor」を選択しています。この場合、1つの周波数ポイントにおける位相ノイズとPNフロアの値を指定できます。「Corner/Floor」を選んだ場合には、PNフロアとコーナー周波数の値を指定することが可能です。「Leeson」では、発振器のパラメータ(パワー、ノイズ指数、負荷Qなど)を指定します。

図11. リファレンスの詳細設定

続いて、「FreqDomain」タブを選択してみてください。すると、オープンループのゲイン/位相と、モデルの出力位相ノイズが表示されます(図12)。出力位相ノイズは、PLL内でロックされた状態のVCOの位相ノイズを表しています。これには、PLL内のすべてのノイズ源の寄与分が含まれています。ここで、画面左側のデータ・パネルにおいて「FreqDomain」フォルダを展開してみてください。それにより、必要に応じてグラフの最小周波数/最大周波数を変更することができます。

図12. 「FreqDomain」タブ

次に「Schematic」タブを試してみましょう。このタブを選択すると、シンセサイザの簡略化された回路図が表示されます(図13)。

図13. 「Schematic」タブ

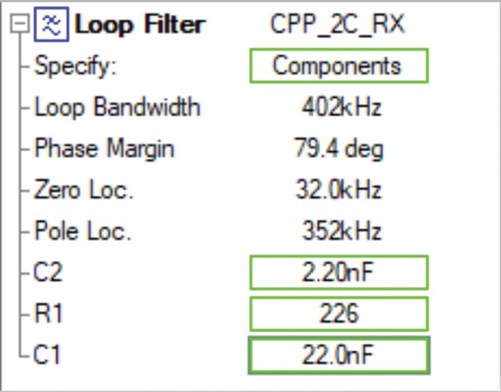

ここで、データ・パネルの「Loop Filter」フォルダを展開してみてください(図14)。ここでは、作成中の回路図や評価用ボードの回路図などに合致するようループ・フィルタのコンポーネントの値を変更することが可能です。図14に示したように「Components」を選択すれば、「Schematic」タブに表示されたループ・フィルタのコンポーネントの値を変更できます。

図14. コンポーネントの値の変更

続いて「DACn」タブを選択してみましょう。このタブでは、DACの出力の位相ノイズを確認することができます。図15のグラフは、3GHzのDACの出力をモデル化したものです。これは、「DDS div」の値として4を設定することで実現しています。「DDS div」の値として整数ではない値を設定することも可能です。図15のようにマーカーをイネーブルの状態にすれば、位相ノイズの値を読み取ることができます。

図15. 「DACn」タブ

ADIsimPLLでリファレンスのモデルを作成する

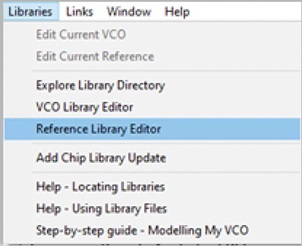

リファレンスのモデルは、Reference Library Editorを使用して作成します。メイン・メニューの「Libraries」から「Reference Library Editor」を選択してください(図16)。それにより、同エディタが起動します。

図16. Reference Library Editorの起動

次に図17をご覧ください。ここでは、青色の枠で囲まれている「New」ボタンをクリックします。

図17. 新規にモデルを作成するための「New」ボタン

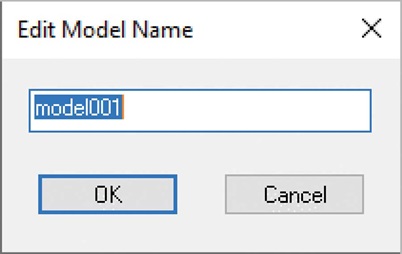

すると、図18のようにモデルの名前を入力するよう促されます。任意の名前を入力して「OK」ボタンを押してください。

図18. 新規モデルの名前の入力

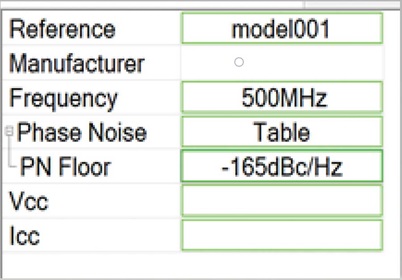

続いて、図19に示したように、左のメニューで「Table」を選択します。その上で、使用するリファレンス周波数とPNフロアの値を入力します。

図19. リファレンス周波数とPNフロアの値の入力

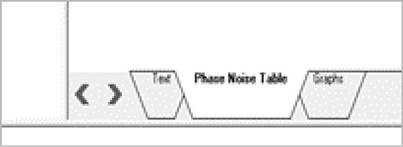

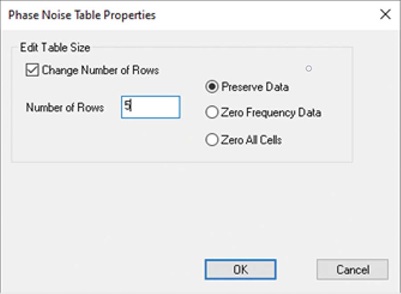

次に、図20のメニューから「Phase Noise Table」を選択し、トップ・メニューから「Properties」を開きます。

図20. 「Phase Noise Table」の選択

図21に示した画面が表示されるので、「Change Number of Rows」にチェックを入れます。ここでは、位相ノイズの測定データの数に応じて「Number of Rows」の値を変更し、「OK」ボタンをクリックします。

図21. 「Number of Rows」の値の変更

すると、図22の画面が表示されます。このテーブルに、リファレンスの位相ノイズの測定データを入力していきます。各ペアの左側の項目にはオフセット周波数の値を入力してください。右側の項目にはその周波数における位相ノイズの値を入力します。なお、オフセット周波数は昇順で入力する必要があります。

図22. 位相ノイズの測定データの入力

入力が完了したら、左上の「Save」のアイコンをクリックして、リファレンス用のフォルダにデータを保存します。

以上の操作によって、ライブラリにモデルが保存されます。それにより、新規に設計を行う際、このモデルを選択できるようになります。

シミュレーション結果と実測結果の比較

最後に、ADIsimPLLで作成したモデルの精度を確認しておきましょう。そのために、ここでは実測結果との比較を行います。実測評価には、AD9081の評価用ボード「EVAL-AD9081」を使用します。同ボードは、fDACが12GHzで3GHzのDACの出力が生成されるように構成しました。図23、図24には、位相ノイズの実測結果とシミュレーション結果を重ねて示してあります。青色のプロットが実測結果、赤色のプロットがADIsimPLLのモデルを使用したシミュレーション結果です。図23は、チャージ・ポンプの電流(ICP)がデフォルトの値(2mA)である場合の結果を表しています。図24は、ICPが最大値(6.4mA)の場合の結果です。

図23. AD9081のICPが2.0mAの場合の位相ノイズ。fDACは12GHz、DACの出力は3GHzです。

図24. AD9081のICPが6,4mAの場合の位相ノイズ。fDACは12GHz、DACの出力は3GHzです。

まとめ

アナログ・デバイセズが提供するADIsimPLL(現行バージョン)には、MxFE製品とRFDAC(AD917x)のモデルが含まれています。ADIsimPLLでこれらのモデルを使用すれば、サンプリング・クロックの設計に要する時間を大幅に短縮できます。本稿で示したように、MxFEのモデルを使用したシミュレーション結果は、実測結果とほぼ一致します。このことから、回路設計に着手する前にADIsimPLLのモデリング機能を活用する手法が非常に有用であることがわかります。