概要

設計リソース

設計/統合ファイル

• Schematic• Bill of Materials

• Gerber Files

• Layout Files (Allegro)

• Assembly Drawing 設計ファイルのダウンロード 1.53 M

評価用ボード

型番に"Z"が付いているものは、RoHS対応製品です。 本回路の評価には以下の評価用ボードが必要です。

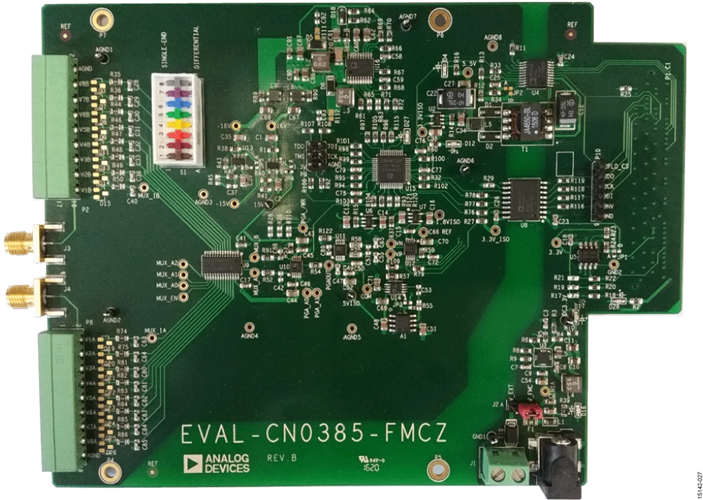

- EVAL-CN0385-FMCZ ($269.35) Isolated, Multichannel Data Acquisition System with PGIA

- EVAL-SDP-CH1Z ($458.85) Eval Control Board

デバイス・ドライバ

コンポーネントのデジタル・インターフェースとを介して通信するために使用されるCコードやFPGAコードなどのソフトウェアです。

AD400x PyADI-IIO (Python Interface for IIO Drivers)

FPGA/HDL

機能と利点

- 絶縁型マルチチャンネル・データ・アクイジション・システム

- 標準的な工業用信号レベルに適合

- 18 ビット、 2MSPS 変換

- 750kHz チャンネル・スイッチング・レート

製品カテゴリ

マーケット & テクノロジー

使用されている製品

参考資料

-

CN0385 Evaluation Board and Software User Guide2018/10/16WIKI

-

CN-0385: 工業用シングル・エンドおよび差動信号対応 PGIA 付き絶縁型マルチチャンネル・データ・アクイジション・システム2016/10/10PDF525 K

回路機能とその特長

図 1 に示す回路は、費用効率の高い、絶縁されたマルチチャンネルのデータ・アクイジション・システムで、標準的な工業用信号レベルに適合しています。サンプル間のセトリング時間を最適化するように部品を厳選し、最高約 750 kHz のチャンネル・スイッチング・レートで、18 ビット動作が可能です。

この回路は利得が独立した 8 個のチャンネルを処理することができ、シングル・エンドと差動のどちらの入力信号にも互換性があります。

アナログ・フロント・エンドには、マルチプレクサ、可変ゲイン計装アンプ(PGIA)、シングル・エンドから差動へ変換するための高精度A/D コンバータ(ADC)ドライバ、アクティブ・チャンネルで信号をサンプリングするための 18 ビット、2.0 MSPS 高精度PulSAR® ADC が実装されています。利得設定は、0.4、0.8、1.6、および 3.2 が可能です。

システムの最大サンプリング・レートは、ターボ・モードで 2 MSPS、通常モードで 1.5 MSPSです。チャンネル・スイッチングのロジックは ADC の変換に同期しており、最大のチャンネル・スイッチング・レートは1.5 MHz です。ターボ・モードでは、1 個のチャンネルが、18 ビットの分解能で最大 2 MSPS のサンプリングが可能です。最高 750 kHz のチャンネル・スイッチング・レートでも 18 ビットの分解能を実現します。

回路説明

図 1 に示した回路は、絶縁型マルチチャンネル・データ・アクイジションのシグナル・チェーンで、マルチプレクサ、プログラマブル・ゲイン段、ADCドライバ、完全差動高精度逐次比較レジスタ(SAR)ADC からなっています。チャンネル・スイッチングおよびゲイン・スイッチングは、ADC の変換周期と同期しています。

このシステムでは、1 個の ADC を使用して最大 8 チャンネルをモニタすることができ、1 チャンネルにつき 1 個の ADC を使用するシステムに比べ、部品数および費用が削減できます。チャンネルごとに異なるゲインを設定できるので、入力範囲の柔軟性を可能にします。コンプレックス・プログラマブル・ロジック・デバイス(CPLD)で制御するため、Labview のグラフィカル・ユーザ・インターフェース(GUI)で設定が可能です。各チャンネルの実効的なサンプリング・レートは、ADC のサンプリング・レートをサンプリング対象のチャンネル数で割った値に等しくなります。

システムの最大サンプリング・レートは、アナログ・フロント・エンドでの各部品のセトリング時間(例えばプログラマブル・ゲイン・アンプ(PGA)の帯域幅や RC フィルタの帯域幅など)と、75 MHz で動作する絶縁型デジタル・インターフェースのクロック・レートによって制限されます。多重化された信号は、本来は不連続で、サンプリングの間に大きな電圧ステップが生じる可能性があります。ADC が変換を実行する前に、これらのステップが安定するまでの適切な時間を、信号チェーンの部品に設定しておく必要があります。信号を安定化させる時間を最大にするために、マルチプレクサ・チャンネルの切り替えは ADC が新しい変換を始めた直後に行います。

ボードへの電源供給は、DC ジャックからの 5~12 V または SDP-H1 コントローラ・ボードからの 12 V の DC 入力が使用可能です。 ADP2441 DC/DC コンバータは 3.3 V の電圧を発生し、デジタル・インターフェースと ADuM3470 の一次側電源入力に供給します。ADP5070、ADP7118 および ADP7182 は正負の電源で、±15 V の電圧を発生します。ADP7118 はアナログおよびデジタル電源で、5 V、3.3 V、および 1.8 V を発生します。絶縁型高速 SPI 通信には、ADuM141E を使用しています。この部品はデータ・レートが最大 150 Mbpsで、伝搬遅延が短く、動的電力消費が低いことが特徴です。

部品の選択

ADG5207 は、ラッチアップ保護機能付き高電圧 8 チャンネル・差動マルチプレクサです。ここで用いられているスイッチは、容量とチャージ・インジェクションが極めて小さく、低グリッチと高速セトリングを必要とするデータ・アクイジションやサンプル&ホールドのアプリケーションにとって最適なソリューションです。ADG5207 の入力部のスイッチング・ネットワークによって、シングル・エンドと差動の両方の入力信号に互換性があります。アクティブ・チャンネルはデバイスのアドレス・ピンを通じて選択されますが、GUI で設定可能で、CPLD によって制御されます。

AD8251 は、プログラマブル・ゲイン計装アンプで、ゲイン設定は 1、2、4、および 8 が選択できます。ゲイン設定を高くすればするほど、AD4003 への入力信号のフル・スケール入力範囲は小さくなります。各ゲイン設定には、それぞれ最適な入力範囲があり、これを表 1 に示します。

| Gain | Full-Scale Input Range |

| 0.4 | ±10.24 V |

| 0.8 | ±5.12 V |

| 1.6 |

±2.56 V |

| 3.2 | ±1.28 V |

AD8475 減衰アンプは、高精度減衰(0.4 ×)、正確なコモンモード・レベル・シフト、およびシングル・エンドから差動への変換機能を備えています。低出力ノイズ・スペクトル密度(10 nV/√Hz)と高速セトリング時間(2 V の出力ステップに対して誤差 0.001 % に達する時間が 50 ns)を特長としているので、AD4003 を駆動するのに最適です。

AD4003 は、完全差動、2 MSPS、18 ビットの高精度 SAR ADCで、4.096 V のリファレンスを使用時に、標準S/N 比(SNR) 98 dB を実現できます。AD4003 はまた低消費電力で、最大処理時でも約 17 mW しか消費しません。この電力消費は処理量に比例し、低サンプリング・レートで動作することで電力消費を抑制することができます(例えば、100 kSPS では 0.17 mW です)。

システムの DC 確度誤差

図 2 にデータ・アクイジション・システムの理想的な伝達関数を示します。

データ・アクイジションの信号チェーンの各部品で、それぞれのオフセット誤差とゲイン誤差が加わるため、システムの実際の伝達関数には、図 2 に示した理想的な伝達関数からのずれが生じます。それらの誤差が累積された影響をシステムレベルで測定するには、既知の DC 値(ゼロに近い値やフル・スケール値)を ADG5207 に入力させ(RC フィルタが実装されている場合はこれに入力させ)、AD4003 から最終的に出力されるコードと比較します。こうすると、システムのキャリブレーション・ファクタを求めることができます。

オフセット誤差の測定

理想的なバイポーラ差動 ADC では、0 V の差動入力に対し、0 のコードが出力されます。実際の ADC では通常、ある程度のオフセット誤差(εb)があります。これは、0 V を入力した時の理想的な出力コードと測定された出力コードとの偏差として定義されます。

データ・アクイジション・システムでのオフセット誤差は、入力を接地して、最終的な出力コードを測定するれば確認できます。この誤差は、AD8251 の各ゲインの設定値間で異なり、ADG5207 の各チャンネル間でも異なります。このため、オフセット誤差は4 通りのゲイン設定すべてにおいて、チャンネルごとに測定します。

このシステムは複数のチャンネルをモニタするため、チャンネル間でのオフセット誤差の偏差を定量化することも重要です。オフセット・エラー・マッチ(Δεb, MAX)とは、チャンネルごとのオフセット誤差と全チャンネルのオフセット誤差の平均値との間の最大偏差を表す尺度のことをいいます。

次式を用いてオフセット・エラー・マッチを計算できます。

ここで、εb,i と εb,j はそれぞれ i チャンネルと j チャンネルでのオフセット・エラーです。.

このオフセット・エラー・マッチは各ゲイン設定に対して存在します。オフセット誤差は、コード単位でもボルト単位でも表現できることに注目してください。

ゲイン誤差の測定

システムのゲイン誤差は、システム全体の不正確さにもつながります。AD4003 の理想的な伝達関数を図 2 に示します。ここで、−217 と 217 − 1 の出力コードが、それぞれ、負のフル・スケール入力電圧(-FS)と正のフル・スケール入力電圧(+FS)に対応しています。しかし、オフセット誤差(εb)とゲイン誤差(εm)が組み合わされると、この関係からの偏差が生じます。

ゲイン誤差は実際のシステム・ゲインと理想的なシステム・ゲインとの間の誤差をパーセンテージで表したものです。より一般的な表現はパーセント・フル・スケール誤差(%FS)で表され、これは217 − 1 のコードを出力する入力電圧の理想値と実測値の間の誤差を表す尺度です。

理想的なフル・スケール入力電圧(VFS, IDEAL)は、ADCの解像度(AD4003 では 18 ビット)とリファレンス電圧(VREF)の精度の関数で表せます。リファレンス電圧の誤差は、ADC のゲイン誤差につながります。リファレンス誤差を ADC のゲイン誤差から切り離すために、VREF を高精度マルチ・メータで測定します。理想的なフル・スケール入力電圧は、次式で計算できます。

実際のシステム・ゲインは、複数の入力電圧のグループとその出力コードの線形回帰の傾き(mLR)を計算し、次のように求めることができます。

従って、フル・スケール入力電圧の実測値(VFS, REAL)は次式から計算できます。

これより、ゲイン誤差(%FSで表したもの)は次式で計算できます。

システムのゲイン誤差は AD8251 のゲインに応じて変化しますが、チャンネルごとに独立しています。そのため、このシステムでは、ゲイン誤差は 4 つのゲイン設定のそれぞれについて測定する必要がありますが、チャンネルについては ADG5207 の 1 チャンネルを用いるだけで済みます。

システム・ノイズ解析

高精度データ・アクイジション・システムの主要な設計目標の 1 つは、高い SNR を実現することです。これは、フル・スケールの信号振幅を増大するか、システムの部品が生成するノイズ・パワーを減少すれば達成することができます。

システムに存在する全ノイズ・パワーは、AD4003 の入力に関わる、個々の部品に起因するノイズ・パワーの二乗和平方根(rss)を取って次式のように求めることができます。

従って、システムの SNR の予測値(SNREXPECTED)は、次のように求まります。

システムの各部品がどのくらいノイズ発生に関わっているかの予測と、全システムの最終的な SNR 性能の予測を、表 2 に示します。この全システムのノイズ計算では、システムの受動部品が関与する熱雑音は無視しています。

AD4003 ADC によるノイズ

AD4003 ADC のノイズは、固有の量子化誤差と内蔵部品(例えば熱雑音を生成する受動部品)に起因するノイズの両方を含む関数で表せます。AD4003 の rms 入力電圧ノイズは、規定されている SNR を用いると、次式で計算できます。

AD4003 の SNR(SNRAD4003)は 4.096 V のリファレンス電圧に対し、約 98 dB と規定されています。

AD4003 の入力で、単極 RC フィルタが上流部品からの広帯域ノイズを制限しています。フィルタの帯域幅をより狭くすればノイズ・パワーはさらに抑制され、SNR は改善します。しかし、その時定数も十分に短くし、電圧キックバックを安定化する必要があります。この電圧キックバックは、アクイジション・フェーズの間に、AD4003 の入力がフロントエンド回路に再接続する際に発生する電荷注入によって起こります。システムに最適な帯域幅は、5 MHz 以上です(詳細については Analog Dialogue の記事、「高精度SAR A/Dコンバータ(ADC)のフロントエンド・アンプとRCフィルタの設計」をご覧ください)。

AD8475 減衰アンプによるノイズ

AD8475 が関与する rms ノイズ(vn, AD8475)は、出力ノイズ・スペクトル密度(NSD)(eAD8475)と AD4003 入力の RC フィルタの帯域幅(BWRC)を含む関数で表され、次式で求められます。

ここで eAD8475 = 10 nV/√Hz。

AD8251 計装アンプによるノイズ

AD8251 は利得段として機能し、小振幅信号の SNR を改善します。これは、信号の振幅を大きくして ±VREF の範囲一杯にし、AD4003 に入力させることにより実現できます。理想的には、システム・ゲインが G 倍だけ増加すると、入力信号の SNR(dB 表示)は次の値だけ改善します。

しかし、実際にはこれだけの改善は得られません。これは、広帯域のノイズも回路のノイズ・ゲイン分だけ増幅されるためです。幸いなことに、この劣化の度合いは、信号ゲインによる改善効果ほどは大きくありません。

AD8251 が関与する rms ノイズは、入力 NSD(eAD8251)、利得設定(GAD8251)、AD8475 の減衰係数(GAD8475)、およびAD4003 入力のノイズ・フィルタの帯域幅を含む関数として次式で表されます。

eAD8251 の値は AD8251 のゲインにも依存します。eAD8251 の値は AD8251 のデータシートに記載されています。

ADG5207 マルチプレクサによるノイズ

ADG5207 が関与する NSD とその結果生じる rms ノイズは、このデバイスがソースと残りのアナログ・フロント・エンド間で直列抵抗として動作するため、ジョンソン・ナイキスト・ノイズの式を用いて求めることができます。

そして

各チャンネルの抵抗値(RON)は、ADG5207 のデータシートに記載されています。

システムのノイズ特性の計算結果を表 2 にまとめます。ノイズ全体に最も影響を与えているのは、AD8251 計装アンプとAD4003 ADC です。

| Gain | ADG5207 | AD8251 | AD8475 | AD4003 | Total | ||||

| en, ADG5207 (nV/√Hz) |

vn, ADG5207 (μV rms) |

en, AD8251 (nV/√Hz) |

vn, AD8251 (μV rms) |

en, AD8475 (nV/√Hz) |

vn, AD8475 (μV rms) |

vn, AD4003 (μV rms) |

vn, total (μV rms) |

SNR (dB) |

|

| 0.4 | 2.04 | 2.29 | 40 | 44.7 | 10 | 28 | 35.4 | 63.6 | 93.2 |

| 0.8 | 2.04 | 4.57 | 27 | 60.4 | 10 | 28 | 35.4 | 75.5 | 91.7 |

| 1.6 | 2.04 | 9.15 | 22 | 98.4 | 10 | 28 | 35.4 | 108.6 | 88.5 |

| 3.2 | 2.04 | 18.3 | 18 | 161 | 10 | 28 | 35.4 | 168.2 | 84.7 |

セトリング時間の分析

図 1 に示す回路が複数のチャンネルをサンプリングすると、異なる入力から取り込まれた各々の信号は、ADG5207 によって時分割多重されます。多重化された信号は、本来は不連続で、通常は短い時間間隔で発生する大きな電圧ステップとなります。図 1 に示すシステムでは、ADG5207 の入力部で 2 個の隣接するチャンネル間の電位差が、20 V もの大きさとなる場合がありますが、セトリングのために割り当てられる時間は、サンプリング期間と同じ長さしか取れません。

図 1 の回路のセトリング時間のモデルを図 3 に示します。システムの各部品には、それぞれのセトリング特性があります。(以降のセクションをご覧ください)。

図 3. CN-0385 回路のセトリング時間モデル

セトリング時間は、アナログ・フロント・エンド回路が入力ステップをある精度に安定化させるために必要な時間と定義されています。この精度は普通、パーセント誤差(例えば、0.1 % や 0.01 % など)で指定されますが、変換システムの場合はこれを分解能で表現することも有用です。例えば、16 ビットの分解能にセトリングすることは、0.001 % にセトリングすることと概ね同等です。表 3 には単極システムについて、パーセント誤差でのセトリングと、分解能でのセトリングの関係を示します。

| Resolution, No. of Bits | LB (%FS) | No. of Time Constants = –ln (%Error/100) |

| 6 | 1.563 | 4.16 |

| 8 | 0.391 | 5.55 |

| 10 |

0.0977 | 6.93 |

| 12 | 0.0244 | 8.32 |

| 14 | 0.0061 | 9.70 |

| 16 | 0.00153 | 11.09 |

| 18 | 0.00038 | 12.48 |

| 20 | 0.000095 |

13.86 |

| 22 | 0.000024 |

15.25 |

複数の部品が実装されたアナログ・フロント・エンドのセトリング時間を見積もることは、さまざまな理由から、それほど容易ではありません。 まず、多くの素子について、セトリング特性がそれほど高精度に特定されているわけではありません。能動素子のセトリング時間もセトリングの精度に対して直線性を有するわけでもなく、0.01 % の精度の場合、0.1 % の精度に比べセトリング時間が最大 30 倍も長くなる場合があります。セトリング時間は、アンプ内部の長時間の熱的影響で決まる場合もあります。さらに、セトリング時間は、素子が駆動している負荷にも影響され、複数の負荷条件について一般的に定まるわけではありません。

また、高い精度でセトリングを測定することは、特別な特性評価プラットフォームがなくては困難です。これは、オシロスコープのオーバードライブと感度の影響を受け、また、十分な立ち上がり時間とセトリング時間を持つ入力パルスを生成することが困難なためです。

セトリング時間を見積もることは、回路を解析する際に、ある一定の範囲と仮定を設定した場合に可能なのです。全セトリング時間は、個別の部品のセトリング時間の rss から次式で計算できます。

システムの最大処理能力は全セトリング時間に逆比例し、次式のようになります。

ADG5207 のセトリング時間

CMOS スイッチの等価回路は、1 個の直列抵抗(RON)と、2 個の並列コンデンサ(CS, CD)をもつ理想的スイッチとして近似できます。従って、マルチプレクサ段と関連フィルタは図 4 に示すようにモデル化できます。

各チャンネルは、RC 回路と同様の働きをします。RC 回路には、セトリング時間を決定づける時定数があります。チャンネルを動的にスイッチングするので、信号のセトリングは複雑になります。これは、チャンネルがスイッチングされるとき、前の出力と現在の入力との差により、キックバック・トランジェントが発生するためです。このキックバックは、AD4003 がアクイジション・フェーズに入る際の入力信号に生じるキックバックと同様のものです。詳細については、Analog Dialogue の記事、「高精度SAR A/Dコンバータ(ADC)のフロントエンド・アンプとRCフィルタの設計」をご覧ください。

図 4 の回路は、図 5 に示すようにNI Multisim™ を用いてシミュレーションを行いました。その際、次の部品の値について、それぞれのデータシートの記載値を使用しました。

- RON = 250 Ω

- CS = 3.5 pF

- CD = 36 pF

- RIN||CIN = 1.25 GΩ||2 pF

AD8251 の入力抵抗(RIN)は、非常に大きく(1.25 GΩ)、シミュレーションからは省かれています。

シミュレーション結果を図 6 に示します。ADG5207 の出力が 10 V の 0.001 % に収まるのに要する時間 tS_ADG5207 は、188 ns です。

AD8251 と AD8475 のセトリング時間

AD8251 のデータシートには、様々な入力電圧のステップ・サイズに対し、ゲイン設定ごとに最小 0.001 % 誤差のセトリング時間の仕様値が記載されています。負荷抵抗が 10 kΩ で、ゲイン設定が 1 の場合、AD8251 は出力で、20 V ステップを約 1 µs 以内に 0.001 % に安定化させます。ゲイン設定が 1 のとき、最長のセトリング時間が必要となります。そのため、セトリング時間解析では 1 µs という値を使用します。

しかし、この 1 µs という値は、AD8251 が AD8475 の 1 個の入力を駆動している場合は正確でないことがあります。AD8475 の入力インピーダンスが 10 kΩ ではなく、2.92 kΩ だからです。さらに、セトリング時間と精度の関係が非線形のため、18 ビット分解能での AD8251 のセトリング時間を確認することもできません。このため、セトリング時間の最良の見積もりは、0.001 % 誤差(または 16 ビット分解能)の場合になります。

AD8475 のセトリング時間の仕様値は、2 V の差動出力ステップに対し 0.001 % 誤差で 50 ns です。AD8475 の出力で見込まれる最大電圧ステップ・サイズは、リファレンス電圧(VREF)の 2 倍、すなわち約 8 V です。セトリング時間が出力電圧ステップに比例すると仮定すると、8 V ステップに対する 0.001 % 誤差(16 ビット分解能)でのセトリング時間は約 200 ns(4 × 50 ns)となります。

このため、各アンプのセトリング時間は、以下のようになります。

- tS_AD8251 = 1 μs

- tS_AD8475 = 200 ns

RC ノイズ・フィルタとAD4003 のセトリング時間

図 7 に、AD4003 入力の等価回路を示します。REXT と CEXT は、ADC 前段の RC 広帯域ノイズ・フィルタを構成する部品です。RIN と CIN はそれぞれ、AD4003 の入力抵抗と入力コンデンサです。CIN は、主に内部容量性D/A コンバータ(DAC)によるものです。CPIN は、主にピン容量で、無視できます。これらの部品の値は次のとおりです。

- REXT = 200 Ω

- CEXT = 120 pF

- RIN = 400 Ω

- CIN = 40 pF

AD4003 では、内部容量性 DAC と電荷再配分アルゴリズムを使用して、出力コードを決定しています。変換プロセスは、アクイジションとコンバージョンの 2 つのフェーズからなります。アクイジションの間は、容量性 DAC は AD4003 の入力端子に接続されています。コンバージョンの間は、DAC は入力端子から切断され、内部ロジックが電荷再配分アルゴリズムを実行します。他の PulSAR ADC と比較して、AD4003 ではコンバージョン時間が大変短く、このためユーザはコンバージョンの終了を待たずにアクイジション・フェーズに戻ることができます。従って、ユーザがこの ADC を遅い処理能力で動作させる場合には、キックバックを安定化させる時間を多く取ることができます。

正確なコンバージョンのためには、信号はアクイジション・フェーズが終わるまでに安定している必要があります。信号がセトリングするための許容時間を最大限にするために、マルチプレクサは AD4003 がコンバージョン・フェーズを開始した直後に、チャンネルを切り替えます。

AD8475 の出力からの多重化信号を安定化させることに加え、RC ノイズ・フィルタと AD4003 の入力では、アクイジション・フェーズの開始時に発生する電圧キックバックを安定化させる必要もあります。詳細については、Analog Dialogue の記事「高精度SAR A/Dコンバータ(ADC)のフロントエンド・アンプとRCフィルタの設計」をご覧ください。

図 7 に示す回路のセトリング時間のシミュレーションは、図 8 に示すように NI Multisim で行いました。V1 は、(AD8475 のシングル・エンド出力からの)AD4003 への各入力に見込まれる最大の電圧ステップを表します。CNV と S1 はコンバージョン・フェーズ(V1 が変化する時に開始)からアクイジション・フェーズ(コンバージョン開始後 300 ns)への AD4003 のスイッチングをシミュレートします。V1 が 0 V から 4 V に切り替わった後、CNV は 300 ns まで S1 をオープンに保っており、コンバージョン・フェーズからアクイジション・フェーズへの遷移を表現しています。ADC_IN は、CNV の立ち上がりエッジで AD4003 がサンプリングする電圧です。

システムのこの部分のセトリング時間は、V1 が 4 V に切り替わる時(TIME = 0、図 9 を参照)から ADC_IN が 4 V の 0.001 % に収まるまでの時間に等しくなります。

シミュレーション結果を図 9 に示します。出力が 4 V の 0.001 % に収まるのに要する時間 tS_AD4003 は 711 ns です。

全セトリング時間

図 1 に示す回路全体の全セトリング時間は、各部品のセトリング時間の rss を計算し、次のとおり見積もることができます。

従って、システムのチャンネル・スイッチングのサンプリング・レートの最大値は、次のように見込まれます。

オフセット誤差とゲイン誤差の影響

図 1 の回路の各ゲイン設定において、チャンネルごとに測定したオフセット誤差を、LSB 単位で表 4 に示します。また、表 4 には各ゲイン設定での全チャンネルのオフセット誤差の平均値も示します。

このオフセット誤差の測定は、全てのチャンネル入力を接地し、各ゲイン設定においてチャンネルごとに取得したサンプリングデータを 32,768 点集め、これを平均して行いました。

| Gain | Channel 1 | Channel 2 | Channel 3 | Channel 4 | Channel 5 | Channel 6 | Channel 7 | Channel 8 | Channel Average |

| 0.4 | 1.34 | 1.33 | 1.31 | 1.36 | 1.44 | 1.45 | 1.46 | 1.48 | 1.40 |

| 0.8 | 1.98 | 1.99 | 2.02 | 2.06 | 2.00 | 1.98 | 1.99 | 1.97 | 2.00 |

| 1.6 |

3.25 | 3.19 | 3.22 | 3.19 | 3.17 | 3.08 | 3.13 | 3.14 | 3.17 |

| 3.2 | 5.57 | 5.66 | 5.67 | 5.55 | 5.57 | 5.50 | 5.54 | 5.52 | 5.57 |

表 5 に、図 1 の回路の各ゲイン設定に対するゲイン誤差の測定値を示します。%FS 誤差は上述の解析方法を用いて求め、V/V 単位の実際のゲインは、理想的なゲインからこの誤差を差し引いて計算しました。

| Gain | Gain Error (%FS) |

| 0.4 | 0.02 |

| 0.8 | 0.02 |

| 1.6 |

0.03 |

| 3.2 | 0.02 |

チャンネル切り換えがない場合の特性結果

図 10、図 11、図 12、および図 13 に、単一チャンネルに 10 kHzのフル・スケールの正弦波を入力させ、ゲイン設定をそれぞれ、0.4、0.8、1.6、および 3.2 にした場合の高速フーリエ変換(FFT)を示します。表 6 に、各ゲイン設定で測定した SNR と rms ノイズを示します。

| Gain | SNR (dB) | RMS Noise (μV rms) |

THD (dB) |

| 0.4 | 93.9 | 55.2 | –99.2 |

| 0.8 | 92.8 | 62.6 | –98.2 |

| 1.6 |

90.6 | 80.7 | –97.0 |

| 3.2 | 88.0 | 108.9 | – 94.6 |

入力信号は Audio Precision SYS-2700 シリーズの信号発生器を使用して供給し、ボードの設定は差動入力モードとしました。図 14 に、各ゲイン設定での入力信号周波数に対する全高調波歪み(THD)の測定値を示します。

チャンネル切り換えがある場合のシステム特性

複数チャンネルのスキャン時のシステム性能を評価するため、いくつかの試験を行いました。高精度 DC 電源を使用した実験では、出力コードの誤差を、サンプリング・レート(同様の試験については回路ノート CN-0269 をご覧ください)とチャンネル間の電圧ステップ・サイズを変化させて測定しました。AC 特性の評価も行い、高精度 AC 電源(Audio Precision AP SYS-2712)から供給される 2 つの位相の異なるフル・スケール入力間のスイッチングを測定しました。

図 15 および図 16 はそれぞれ、DC および AC 特性試験の構成を示しています。チャンネル・スイッチング・レートとは、ADG5207 があるチャンネルから別のチャンネルに切り替えるレートのことで、AD4003 のサンプリング・レートと等価なものです。

DC 特性試験では、2 チャンネル間の電圧ステップ・サイズとチャンネル・スイッチング・レートを変化させて測定しました。チャンネル・スイッチング・レートの変化量は、50 kHz から 1 MHz まで、50 kHz 刻みとしました。電圧ステップ・サイズは、各ゲイン設定に対応した範囲で変化させました。平均コードの結果は、チャネルごとに電圧ステップ・サイズとチャンネル・スイッチング・レートを変化させて測定し、チャンネルごとに取得した 8,192 サンプルついて平均化したものです。静的な(チャンネル切り替えがない)場合についても、チャンネルごとの平均コードの結果を測定しました。以下で検討する平均コード誤差は、静的チャンネルで測定した平均コードと、スイッチング・チャンネルで測定した平均コードとの差を取ることで求まります。

図 17、図 18、図 19、および図 20 には、4 通りのゲイン設定それぞれについて、複数のスイッチング・レートで電圧ステップ・サイズを変えたときの平均コード誤差を示しています。図 21 から図 24 には、それぞれ 4 通りのゲイン設定について、スイッチング・レートを変えたときのフル・スケール電圧ステップでの平均コード誤差を示しています。

電圧ステップ・サイズとチャンネル・スイッチング・レートが増加するにつれ、平均コード誤差は増大します。この増大は、信号チェーン内に存在する部品のスルーとセトリング時間による制限が組み合わされた結果です。ステップ・サイズが大きくなると、システムはより大きな電圧変動を安定化させなければなりません。また、チャンネル・スイッチング・レートが上がると、こうした変動を安定化するためのシステムの許容時間が短くなります。ゲイン設定が 0.4 の場合に見られるように(図 17 および図 21 を参照)、ステップ・サイズやスイッチング・レートが十分に大きくなると、平均コード誤差は予測できないほど増大します。このコード誤差は、AD8251 計装アンプ内の入力バッファ・アンプのスルー・レートの制限が原因です。

AC 電源を使用した場合のシステム性能は、チャンネル・スイッチング・レートに対する THD を比較して評価しました。AP SYS-2712 を用いて、フル・スケールの正弦波を一方のチャンネルに入力し、その正弦波を反転したものをもう一方のチャンネルに入力しました。THD の測定は、サンプリング・レートを 25 kSPS から 1.5 MSPS まで 25 kSPS 刻みで変えて行いました。図 25 に、ゲイン設定ごとに各チャンネルについて測定した THD を示します。

システムの THD 特性はおよそ 700 kSPS で劣化し始めます(ゲイン設定に依存します)。全信号チェーンの SNR と THD 特性は、主に PGA の AD8251 によって制限されます。また、AD4003 前段の RC フィルタの帯域幅を狭くすると、チャンネル・スイッチング・サンプリング・レートが高い場合の THD を改善します。

バリエーション回路

AD4003 ADC は、他のさまざまな 14 ビット、16 ビット、および 18 ビットの 10 ピン 高精度 SAR ADC とピン互換です。また、他のさまざまな ADC も CN-0385 システムに使用可能です。帯域幅がより広い ADG1207 は ADG5207 の代わりに使用できます。ADG5248F には、故障保護検出機能があり、シングル・エンド入力として使用できます。AD8475 が出力する差動出力信号は、AD7690 のような他の差動 ADC にも適用可能です。ADA4805-1 オペアンプは、疑似差動またはシングル・エンドの ADC(例えば AD4000)を駆動する場合に、AD8475 の代わりに使用できます。ADP7102 や ADP7142 のような、アナログ・デバイセズの他の LDO は ADP7118 と置き換えが可能です。

回路の評価とテスト

この回路は EVAL-CN0385-FMCZ 回路ボードと EVAL-SDP-CH1Z SDP-H1 システム・デモンストレーション・プラットフォーム・コントローラ・ボードを使用します。これら 2 枚のボードは 160 ピン接続用コネクタを備えているので、手早くセットアップして回路の性能を評価することができます。この回路ボードには、本回路ノートに記載したとおり、評価対象の回路が実装されており、SDP-H1 コントローラ・ボードを CN-0385 評価用ソフトウェアとともに使用すると、回路ボードからデータが取得できます。

必要な装置

以下の装置類が必要になります。

- USB ポート付き Windows® XP、Windows Vista®(32 ビット)又は Windows 7 (32 ビット)対応の PC

- EVAL-CN0385-FMCZ 回路評価ボード

- EVAL-SDP-CH1Z SDP-H1 コントローラ・ボード

- CN-0385 評価用ソフトウェア(ftp://ftp.analog.com/pub/cftl/CN0385/ からダウンロード)

- 5~12 V の DC 電源または電源アダプタ(EVAL-CN0385-FMCZ ボード付属の 9 V 電源アダプタ)

- micro-USB 変換ケーブル

- 出力電圧 ±10 V の低歪み、低出力インピーダンスの信号発生器

- 出力電圧 ±10 V の低ノイズ高精度 DC 電源

評価開始にあたって

評価用ソフトウェアを ftp://ftp.analog.com/pub/cftl/CN0385/ からダウンロードし、PC にインストールします。

機能ブロック図

回路ブロック図については図 1 をご覧ください。また、完全な回路図は EVAL-CN0385-FMCZ-SCH.pdf をご覧ください。このファイルは CN-0385 デザイン・サポート・パッケージ(www.analog.com/CN0385-DesignSupport から入手可能)に含まれています。図 26 にテスト・セットアップの機能ブロック図を示します。

ハードウェア構成

EVAL-CN0385-FMCZ 評価用ハードウェアを図 27 に示します。SDP-H1 ボードについての詳細は、SDP-H1 ユーザー・ガイドを参照してください。

回路ボードの 160 ピン・コネクタを SDP-H1 コントローラ ボードの J4 コネクタに接続します。

まず、5~12 V の DC 電源アダプタを P3 DC ジャックまたはターミナル・ブロック J1 に接続し、ジャンパ J2 を V_EXT の位置に接続します。もしくは、J2 を V_FMC に接続し、SDP-H1 ボードからの 12 V 電源を使用します。次に SDP-H1 ボードを micro-USB 変換ケーブルを介して PC に接続します。

テスト

電源または DC 電源アダプタと USB ケーブルを接続し、評価用ソフトウェアを立ち上げます。USB 通信が確立すると、SDP-H1 ボードを使用して EVAL-CN0385-FMCZ ボードからのデータの送受と取得ができるようになり、時間および周波数ドメインでのデータ解析を実行できます。テスト・セットアップとキャリブレーションについての詳細、およびデータ取得のための評価用ソフトウェアの使用方法については、CN-0385 ソフトウェア・ユーザー・ガイドに記載されています(www.analog.com/CN0385-UserGuide から入手可能)。