AN-1291: デジタル・ポテンショメータの FAQ

はじめに

このアプリケーション・ノートでは、アナログ・デバイセズのデジタル・ポテンショメータ (digiPOT) 製品に関して、よくある質問 (FAQ) に答えます。一般的な質問はもちろん、および製品固有の質問にもお答えします。さらに、digiPOT の設定に関しても情報を提供します。

digiPOT とは?

digiPOT はデジタル的に制御される抵抗で、RDAC レジスタにロードされたコードに応じて、ピン間とワイパーとの間のインピーダンスを変化させます。デジタル・ポテンショメータは、物理的なサイズ、摩耗、損傷、さらに振動、温度、湿度に対する感受性のような機械的ポテンショメータで生ずる問題を回避します。digiPOT は、ポテンショメータとレオスタット(可変抵抗器)の 2 つのモードに設定することができます。

ポテンショメータ (図 1 参照) には 3 本のピンがあります。Aピン、B ピン、W ピン (ワイパー)です。

図 1.ポテンショメータ・モード

レオスタットは、ピンの内 1 本を A ピンまたは B ピンへハードワイヤ接続して構成します (図 2 参照)。製品によっては、Aピンと W ピンの 2 ピンのみを提供する場合もあります。

図 2.レオスタット・モード

評価用ボードに関係する評価ツールとソフトウェアはどこで見つけますか?

Windows®互換評価ソフトウェアとドライバ・ソフトウェアは、通常、評価用ボード・キットに付属している CD に含まれています。新しい製品の場合、大部分の情報はオンラインで提供しています。

digiPOT のテクニカル・サポートを受ける方法は?

EngineerZone は、アナログ・デバイセズのオンライン・サポート・コミュニティです。digiPOT のサポートは、高精度 DAC という名前のコミュニティから提供しています。全世界のお客様が、質問を掲示し、既存の質問と回答を閲覧し、このコミュニティで進行中のディスカッションを検討したり、これに参加することができます。

カテゴリごとのDigiPOTに関するFAQ

一般的な FAQ

推奨パワーアップ・シーケンスはありますか?

はい、製品データシートにデバイスのパワーアップ前に参照すべき推奨スタートアップ・シーケンスを記載してあります。

一般に、最初に VDD をオンにし、次に VSS をオンにします。VA、VB、VW の順序は重要ではありませんが、これらは最後にオンにする必要があります。

VDD と A、B、W の各ピンとの間には ESD 保護ダイオードがあります。例えば、ダイオードの 1 つのカソードが VDD に接続され、アノードが A ピンに接続されています。このため、VDD がオンになる前に A ピンに電圧が発生すると、ダイオードが順方向にバイアスされて VDDがオンになってしまいます。

digiPOT によっては、デジタル信号の電源も VDD の後にオンにする必要があります。これは、該当するデータシートに記載されています。

すべての digiPOT は |5 V|に制限されていますか?

いいえ、大きな単電源と両電源に対応するため、digiPOT の広範なポートフォリオを提供しています。最新の製品リストについては、オンライン・カタログを参照してください。

digiPOT はバイポーラ動作と AC 動作が可能ですか?

はい、アナログ・デバイセズは、バイポーラ動作または AC 動作が可能な±2.5 V、±5 V、または±15 V の両電源に対応するdigiPOT を提供しています。DC オフセットを上げれば DC 単電源でも AC 動作が可能です。A ピン、B ピン、W ピンには、相互に極性の制約はありません。

両電源 digiPOT で、VDD/VSSがそれぞれ+2.5 V/−2.5 V の場合、ロジック・レベルの変換なしで標準 3.3 V CMOS ロジック部品からデジタル入力を供給することができますか?VDD = +2.5 V で VSS = -2.5V の場合、ロジック・レベル・スレッショールドはどうなりますか?

バイポーラ ±2.5 V digiPOT を使用する場合、最大デジタル電源は VDD +0.3 V または VLOGIC + 0.3 V に制限されます。そうしないと、内蔵保護ダイオードが電圧をクランプするため、損傷することがあります。digiPOT レベルの詳細については、データシートで確認してください。

ロジック・レベルと消費電力との間には相互依存性がありますか?

あります。ロジック・レベルがロジック電源 (VDD またはVLOGIC (存在する場合))より低い場合、入力ゲートは完全にスイッチしないため、デバイスの消費電力が大きくなります。

なぜ機械的ポテンショメータを digiPOT で置き換えるのですか?

機械的ポテンショメータの使用に対して digiPOT の使用には次のような利点があります。

- 高い分解能

- 高い信頼性

- 優れた安定性

- 迅速な調整

- 多くの機能

- 優れたダイナミック制御

ただし、digiPOT は機械的ポテンショメータに対する直接の置換品ではありません。詳細については「デジタル・ポテンショメータは機械的ポテンショメータに対する真の置換品ですか、または電圧について制約がありますか?」の質問を参照してください。

デジタル・ポテンショメータは機械的ポテンショメータに対する真の置換品ですか、または電圧について制約がありますか?

デジタル・ポテンショメータは、機械的ポテンショメータに対する正確な置換品ではありません。VA と VB は VDD より高くしてはならず、VSS より低くしてもいけません(デバイスに VSSピンがない場合は GND)。例えば、VA と VB をそれぞれ +2 Vと -2 V とすると、VDDは+2 V 以上で VSSは-2 V 以下である必要があります。

詳細については、 AN-1121 アプリケーション・ノート「Replacing Mechanical Potentiometers with Digital Potentiometers」を参照してください。

不揮発性メモリを持たない digiPOT の場合、パワーアップ時の状態はどうなりますか?

アナログ・デバイセズの大部分の digiPOT (ただし AD8400/AD8402/AD8403 は除きます) は、パワーオン・リセット(POR) 回路を内蔵しています。この回路が、ワイパー―ピン間抵抗をピン―ピン間抵抗の中心値に設定します。例えば、RAB= 10 kΩ の場合、パワーアップ時に RWB = RWA = 5 kΩ になります。この機能を持たない digiPOT では、ワイパー―ピン間抵抗はパワーアップ時に不定になります。詳細については、該当するデータシートを参照してください。

特別な低消費電力デジタル・ポテンショメータはありますか?

あります。AD5165 は、超低消費電力のアナログ・デバイセズ製品です。最新の製品リストについては、オンライン・カタログを参照してください。

メモリを使うと、マイクロプロセッサからの更新なしでデバイスを最後に保存された値に戻すことができますか?

はい、そのとおりです。デバイスがパワーオンするごとに、前に保存された値に自動的に設定されます。デフォルトでは、EEPROM は出荷時にミツドスケールに設定されます。

デュアル・デジタル・ポテンショメータでの Ch1 と Ch2 の間の抵抗の整合性はどの程度ですか?

整合性は 0.1%~0.2% (typ)で、±1%は通常最大値として規定されています。

デバイス間の抵抗の整合性はどうですか?

同じバッチからのデバイスの場合、デバイス間の抵抗の整合性は ±1%と考えられています。

digiPOT の抵抗許容誤差は?

正確な値については、該当するデータシートを参照してください。ポテンショメータを 3 ピン分圧器モードで使う場合 (直列抵抗なし)、抵抗 RWAと RWBの比に意味があるため許容誤差は無関係になります。ポテンショメータを 2 ピンのレオスタット・モードで使用する場合は、ワーストケースの変動を考慮する必要があります。

不揮発性 digiPOT によっては、抵抗許容誤差を 0.1%精度で出荷時にメモリに格納しているものがあります。ユーザーは抵抗許容誤差を取り出して、システムをキャリブレーションすることができます。

必要な抵抗値または分解能を得るために、複数の digiPOTをカスケード、直列、または並列に接続できますか? ステップあたり約 1 Ω の 250 Ω デジタル・ポテンショメータを必要としています。4 個の 1 kΩ AD8403 を並列に接続し、各々を同じ公称値に設定することを考えています。

そのとおりです。 AN-582 アプリケーション・ノート「複数のデバイスによるデジタル・ポテンショメータの分解能の向上 」を参照してください。

デジタル・ポテンショメータはどのようにデザインされていますか?ワイパー・スイッチは理想的ですか?

digiPOT は純粋な CMOS デバイスです。すべてのスイッチは均一な小さい RDS(on)を得るためにリニア領域で動作する大型のCMOS トランスミッション・ゲートから構成されています。すべての抵抗エレメントはポリシリコンまたは薄膜抵抗です。

デジタル・ポテンショメータの温度係数は?

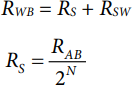

与えられた設定に対して抵抗を構成する成分は 2 つあります。この 2 つの成分は、ポリシリコン抵抗または薄膜抵抗 (ステップ抵抗 Rs)と CMOS スイッチ抵抗 (5 V 電源で Rsw=50 Ω)です。これは次のように加算されます。

データシートで公表されているステップ抵抗の温度係数(tempco) は一般に、薄膜では-35 ppm/°C、ポリシリコンでは600 ppm/°C です。これに対して、スイッチ抵抗は 100°C で 2 倍になります。このため、全体の温度係数は非線形になるので、スイッチ抵抗が支配的な小さいコード値では悪くなります。詳細については、データシートの温度係数のグラフを参照してください。

デジタル・ポテンショメータに流せる最大電流は?

最大電流は、与えられた抵抗設定で 3 つの境界により制限されます。この 3 つの境界とは、A ピン、B ピン、W ピンの内の任意の 2 ピンに加えられる最大電圧、パッケージの消費電力、内蔵スイッチの最大電流処理能力です。

各データシートでは、絶対最大定格のセクションにこの最大電流を記載しています (表 1 の例を参照)。

アナログ・デバイセズの digiPOT は、回路のゲインに影響を与えるリーク電流の影響を受けますか?

DigiPOT は非常にリークの小さいアナログ・スイッチ・プロセスで製造されているため、リーク電流は小さくなっています。通常、1 nA (typ)の同相モード・リーク電流として規定されています。

| Parameter | Rating |

| IA, IB, IW Pulsed Frequency > 10 kHz RAW = 5 kΩ and 10 kΩ RAW = 80 kΩ Frequency ≤ 10 kHz RAW = 5 kΩ and 10 kΩ RAW = 80 kΩ Continuous RAW = 5 kΩ and 10 kΩ RAW = 80 kΩ |

±6 mA/d ±1.5 mA/d ±6 mA/√d ±1.5 mA/√d ±6 mA ±1.5 mA |

| d はパルス・デューティ・ファクタ。 | |

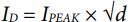

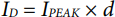

パルス電流の計算は、周波数に依存します。周波数が 10 kHz 以下の場合は、次式のようになります。

周波数が 10 kHz 以上の場合は、次式のようになります。

ここで、

Id = 最大 DC 電流

Ipeak = 波形の最大ピーク電流値

d = デューティ・ファクタ (0.1 = 10% デューティ・サイクル)

R-DNL の仕様に関して、相対的な調整についてのみ懸念を持っています。digiPOT 内の実際の抵抗値についての懸念はないのですが、digiPOT は単調である必要がある場合どうなるでしょうか?

レオスタット・モードの digiPOT では、R-INL(抵抗積分非直線性)および R-DNL(抵抗微分非直線性)と呼ばれる 2 つの仕様があります。INL は、DAC の理論出力値と実際の出力レベルとの最大誤差として定義されます。R-INL は、最大抵抗ワイパー・ポジションと最小抵抗ワイパー・ポジションとの間で測定された理論値からの差を表します。DNL は、DAC 伝達関数で 2つの連続するコード間の最大誤差です。R-DNL は、連続タップ・ポジション間での理論値からの相対的ステップ変化を表します。

アナログ・デバイセズのすべての digiPOT は単調性が保証されています。

デュアル digiPOT の Ch1 と Ch2 の間で、Ch1 に入力された正弦波が Ch2 に現れるなどのクロストークがありますか?

あります。通常、製品データシートにこのような性能を記載してあります。一般に−70 dB です。

図 3.アナログ・クロストーク

Ch 1 をゼロスケールからフルスケールへ変化させた場合、Ch 2 に影響がありますか?

これはステップ応答クロストークです。これはアナログ・クロストークとは異なります。通常、データシートにこの情報は記載されています。このクロストークは一般に、5 nV/sec~10nV/sec の範囲です。

図 4 に、デジタル・クロストークの例を示します。

図 4.デジタル・クロストーク

デジタル・フィードスルーはどうですか?

デジタル・フィードスルーは、クロックまたはデータから出力へ混入するノイズの大きさを意味します。通常は非常に小さい値です (数 nV/sec の範囲)。図 5 に、デジタル・フィードスルーの例を示します。

図 5.デジタル・フィードスルー

デジタル・ポテンショメータの THD 性能は?

このパラメータはコードと VDD に依存します。一般に、−86.02dB ~ −60 dB の範囲です。特定の性能については製品データシートを参照してください。デバイスを最大動作電圧で動作させたとき、最適 THD 性能が得られます。AD5292 は、最大 −100dB の THD を実現しています。

コントローラから 8 ビットのワード長を使って 6 ビットのワード長を必要とする digiPOT をどのように制御するのですか?

SPI インターフェースのデジタル・ポテンショメータは、先頭 2ビットの MSB を無視し、次の 6 ビットを読出すことにより動作します。詳細については、製品データシートを参照してください。

コントローラから 8 ビットのワード長を使って 12 ビットのワード長を必要とする digiPOT をどのように制御するのですか?

2 バイト・ワードを発行します。先頭の 4 ビットの MSB を無視します。詳細については、製品データシートを参照してください。

複数の digiPOT をどのようにデイジーチェーン接続しますか?

digiPOT をデイジーチェーン接続するときは、前のパッケージの SDO ピンを次のパッケージの SDI ピンに接続する必要があります。伝搬遅延のため、クロック周期を大きくする必要があることがあります。

図 6 では、2 個の AD5122 digiPOT が接続されています。このセットアップでは、32 ビットが必要です。最初の 16 ビットが U2へ、次の 16 ビットが U1 へ、それぞれ送信されます。この 32ビット書込みの間、SYNCはロー・レベルに維持されます。

図 6.DigiPOT のデイジーチェーン接続

すべてのビットが入力されたとき、SYNC ピンをハイ・レベルにして書込みを完了します。AD5144 および同様の SPI デバイスでは、例えば、ノイズのためにデータが壊れるのを防止するため、digiPOT はカウンタを内蔵しています。クロック数が予想に反する場合、データを無視します。SYNC をハイ・レベルにすると、カウンタがリセットされます。詳細については、製品データシートを参照してください。

マルチチャンネル・デジタル・ポテンショメータの 2 チャンネルを同時に設定することができますか?

はい、できます。AD5251/AD5252/AD5253/AD5254 や AD5232/AD5233/ AD5235 のような digiPOT を選択すると、すべてのチャンネルを同時にインクリメント/デクリメントすることができます。さらに、各 EEMEM に書込みを行った後に、RESET コマンドを発行して、すべての RDAC 設定を同時に更新することができます。

AD5144 のような幾つかの製品には、LRDAC ピン (RDAC 入力レジスタのロード) があり、これを使ってデータを入力レジスタから RDAC レジスタへ転送してワイパー位置を更新します。1 つの RDAC レジスタまたはすべてのレジスタを 1 回で更新することができます。

digiPOT のワイパー設定をリードバックできますか?AD5242 や AD5282 のようなデュアル I2C 互換 digiPOT の2 つの RDAC レジスタ値についてはどうですか?

可能です。digiPOT を選択してワイパー設定値をリードバックすることができます。

RDAC レジスタ値 (特定チャンネルの RDAC 値)をリードバックすることもできます。ただし、前の書込みモードで選択したRDAC チャンネルのみを読出すことができます。読出したいチャンネルが前に書込んだチャンネルと異なる場合は、目的のチャンネルを選択するためにダミーの書込みコマンドが必要です。詳細については、該当するデータシートを参照してください。

パラレル入力から制御される digiPOT はありますか?

ありません。

WP、PR、RDY の機能は?

WP は書込み保護です。例えば、ADN2850 では、WPがスクラッチパッド・レジスタ値の変更をディスエーブルします。スクラッチパッド・レジスタがデジタル抵抗ワイパーを直接制御するため、変更回数の制限はありません (書込み回数が制限される EEPROM とは異なります)。

ただし、EEPROM を使ってワイパー位置を復元するコマンドは依然使用できます。つまり、WP ピンは EEPROM 値を保護する方法として使用されます。

さらに、ADN2850 では、ハードウェア優先プリセット (PR)ピンを使って、スクラッチパッド・レジスタを EEPROM 値で上書きすることができます。

RDY ピンは、コマンドが完了して次のコマンドに対する準備ができたことを表示します。

詳細については、特定の製品データシートを参照してください。

デジタル・ポテンショメータの ESD 定格は?

すべての digiPOT の ESD 定格は 1 kV より高くなっています。詳細については、製品データシートを参照してください。

digiPOT パッケージのピン間 RAB 抵抗値はどのように指定しますか?

各データシートのオーダー・ガイド・セクションには、モデル番号とブランド・コードが記載してあります。例えば、AD8400は SOIC パッケージを採用し、AD8400AR1、AD8400AR10、AD8400AR100 のブランドで表されます。これらは、それぞれ 1kΩ、10 kΩ、または 100 kΩの RABを表します。さらに小型のパッケージでは、3 文字のコードが使用されています。データシートのブランド・コードを使用すると、RAB の識別に役立ちます。

EEPROM メモリ内蔵 DigiPOT についての FAQ

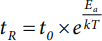

55°C で動作させた場合、15 年後に EEMEM のデータをリフレッシュする必要がありますか?

あります。EEPROM セルは 55°C で動作した場合、15 年を過ぎると電荷を失います。

保持時間として測定した後、De Salvo およびその他の著者による 「 Experimental and Theoretical Investigation of Nonvolatile Memory Data-Retention」で定義されたモデルを使ってそれを外挿しています。この IEEE 文献はオンラインで提供されています。

ここで、

tRは温度に基づく保持時間。

t0 は無限温度に対応する保持時間。

Eaは活性化エネルギー。

k はボルツマン定数。

T は温度。

その他の動作温度については、 図 7 を参照してください。アナログ・デバイセズの digiPOT は、規定のジャンクション温度(TJ = 55°C)での JEDEC データ保持時間の仕様(A117)に準拠して評価されています。

図 7. 温度対データ保持時間の例

この認定手順の一部として、フラッシュ/EE メモリを規定の書き変え回数までサイクル・テストした後に、データ保持時間をキャラクタライゼーションしています。これは、フラッシュ/EEメモリでは、書き変えるごとに規定のデータ保持時間データを保持することが保証されていることを意味します。0.7 eV の活性化エネルギーに基づくデータ保持時間は、TJ の上昇とともに短くなることにも注意してください。このデータは不揮発性メモリを採用するすべての digiPOT に適用されます。

規定の EEMEM データ保持時間が経過した後、電源をオフにした後オンに戻すと、デバイスは "リフレッシュ" されたと見なすことができるのですか?

いいえ違います。これにより RDAC レジスタはリフレッシュされますが、EEPROM はリフレッシュされません。15 年後にデータを再ロードして、EEPROM セルに新しい電荷を与える必要があります。これを行うときは、15 年が経過する前に RDAC ワイパー・レジスタに書込みを行って、EEPROM のデータを元に戻します。

幾つかの DigiPOT の最大動作温度は、なぜ標準の 125°C ではなく 85°C なのですか?

EEPROM を内蔵する digiPOT は通常、最大 85°C まで動作します。これは、EEPROM の安全な動作は 85°C 以下であるためです。

アプリケーション情報

オーディオ

デジタル・ポテンショメータをオーディオ・ボリューム制御で使用する場合、ジッパー・ノイズが発生しますか?

ジッパー・ノイズが聞こえます。ただし、アナログ・デバイセズは、AD5292 デジタル・ポテンショメータを使ったグリッチ低減機能を持つログ・オーディオ・ボリューム制御を開発しました。AN-1209 アプリケーション・ノート 「Logarithmic Audio Volume Control with Glitch Reduction Using the AD5292 Digital Potentiometer」を参照してください。

図 8.グリッチ低減機能を持つ対数オーディオ・ボリューム制御 (簡略化した回路図: デカップリングとすべての接続は省略)

デジタル・ポテンショメータは対数テーパ調整が可能ですか?

オーディオ制御のようなアプリケーションでは、疑似対数テーパ調整がよく使用されます。ただし、AD5231/AD5232/AD5233/AD5235 または ADN2850 のユーザーに対しては、答えはイエスです。これに対して、シンプルな設定を持つその他のリニア調整ポテンショメータでは、疑似対数テーパの調整が可能です。詳細については、2000 年 1 月出版の Hank Zumblen 著「Tack a Log Taper onto a Digital Potentiometer」がオンラインで提供されています。

オーディオ・ボリューム制御

AD7376 は優れた THD 性能と高電圧能力を備えているため、デジタル・ボリューム制御に使用することができます。AD7376を直接オーディオ減衰器またはゲイン・アンプとして使用する場合、ボリューム・レベルに任意の時間に大きなステップ変化があると、オーディオ信号に突然の不連続が生じることがあり、可聴ジッパー・ノイズが発生します。これを防止するには、ゼロ交差ウィンドウ検出器をCS ラインに挿入して、オーディオ信号がウィンドウと交差するまでデバイスの更新を遅延させることができます。入力信号は絶対ゼロ・ボルト・レベルではなく任意の DC レベルに重ねて動作できるため、この場合のゼロ交差は、信号が AC 結合されて、DC オフセット・レベルが信号のゼロ・リファレンス・ポイントになることを意味します。

ジッパー・ノイズを小さくする構成とこの構成を使用した結果を、それぞれ図 9 と図 10 に示します。入力は C1 で AC 結合され、減衰させた後に U2、U3、U4B で構成されたウィンドウ・コンパレータに供給されます。U6 を使って信号ゼロ・リファレンスを設定します。コンパレータの上限はオフセットの上に設定されるため、この例では入力が 2.502 V ~ 2.497 V (すなわち0.005 V ウィンドウ)の範囲内に入るごとにハイ・レベルの出力パルスが発生します。この出力とチップ・セレクト信号とのAND をとって、信号がウィンドウと交差するごとに AD7376 が更新されます。デバイスが絶え間なく更新されるのを回避するため、チップ・セレクト信号を AD7376 データシートに示す 1個ではなく 2 個のパルスとして設定する必要があります。

図 9.オーディオ・ボリューム制御

図 10. 図 9 の回路の入力(トレース 1) と出力 (トレース 2)

図 10 の下のトレースは、ゼロ交差ウィンドウ付近で信号が変化するとき 1/4 スケールからフルスケールまでボリューム・レベルが変化することを示しています。 AD7376 のシャットダウン・スリープ・モード設定機能を使うと、パワーアップ時に SHDNをロー・レベルにホールドしてゼロスケールを設定して、デバイスをミュートさせることができます。

ボリューム制御付きのオーディオ・アンプ

AD5228 と SSM2211 でボリューム制御付きの 1.5 W オーディオ・アンプを構成することができます。このアンプは、PDA や携帯電話のような携帯機器向けに十分な電力と品質を持っています。SSM2211 は、ピン 5 とピン 8 の間に接続した 1 個のスピーカを出力コンデンサなしで差動駆動することができます。ハイパス・カットオフ周波数は fH1 = 1/(2 × π × R1 × C1)です。

SSM2211 は、 2 個のスピーカも駆動することができます(図 11参照)。 ただし、スピーカはシングルエンド・モードに構成する必要があり、DC 電流を阻止するための出力結合コンデンサが必要です。 出力コンデンサとスピーカ負荷により、ハイパス・カットオフ周波数 fH2 = 1/(2 × π × R5 × C3)が追加されます。このため、周波数を fH1 まで下げるため C3 と C4 を大きくする必要があります。

図 11.ボリューム制御付きのオーディオ・アンプ

インターフェース

ビデオ信号のゲイン調整の場合、1 MHz~10 MHz の周波数で digiPOT を調整できますか?

帯域幅は、コードとピン間抵抗 RABの関数になっています。RABとコードが小さいほど、帯域幅は広くなります。digiPOT の中には 10 MHz 以上の帯域幅が可能なものもあることに注意してください。ボード線図については、製品データシートを参照してください。

デジタル・ポテンショメータの CLK 入力に供給可能な最大周波数は?

SPI および Up/Down (U/D) デジタル・インターフェースのdigiPOT の場合、最大クロック周波数は 10 MHz ~ 50 MHz の範囲です。I2C 互換 digiPOT の場合、最大クロック周波数 400 kHzを保証しています。

LCD パネルの VCOM調整

AD5259 の特別な機能は、VLOGICピンと VDD 電源ピンの分離です。この分離により、必要な電源電圧を常に提供しないアプリケーションで柔軟性が強化されています。

特に、LCD パネルでは 3 V ~ 5 V の範囲の VCOM 電圧が必要とされます。

図 12 に、デジタル・ポテンショメータに供給する 5 V 電源が存在する珍しい例外を示します。

図 12.VCOM 調整アプリケーション

図 13 に示すさらに一般的なケースでは、アナログ 14.4 V 電源とデジタル・ロジック 3.3 V 電源しか使いません。デジタル・ポテンショメータの上方と下方にディスクリート抵抗を接続すると、抵抗ストリング自体から VDD を取り出せるようになります。選択した抵抗値では、VDD電圧はこの場合 4.8 V になり、ワイパーは 4.8 V まで安全に動作することができます。 VDD 電流は μA のオーダーであるためノードのバイアスに影響を与えません。VLOGICは MCU 3.3 V デジタル電源に接続します。これはEEPROM の書込み時に VLOGICから 35 mA を供給するためです。70 kΩ抵抗を通して 35 mA を供給することは実用的でないため、VLOGICは VDDと同じノードには接続しません。

図 13.VDD電源が分離されていない場合の回路

このため、 VLOGICと VDD は分離した 2 本の電源ピンとして扱い、相互に接続するか別々に使用することができます。VLOGIC はロジック/EEPROM の電源として使い、VDD は A、B、W ピンにバイアスを供給して、柔軟性を向上させます。

このアプリケーションの詳細については、雑誌 EDN の 2004 年9 月 30 日号に記載の「Simple VCOM Adjustment uses any Logic Supply Voltage」を参照してください。オンラインでも提供されています。

ロータリ・エンコーダによる手動制御

図 14 に、ロータリ・ノブ操作で機械的ポテンショメータをエミュレートするもう 1 つの AD5227 の使い方を示します。ロータリ・エンコーダ U1 には、グラウンドピン C および位相が異なる 2 本の信号 A と B があります。

図 14.手動ロータリ制御

U1 を時計向きに回すと、B ピンから発生するパルスは A ピンから発生するパルスより位相が進みます。逆に回すと逆になります。U1 の信号 A と信号 B は、U1 の A と B の位相差を U3AD5227 の互換入力へ変換する直交デコーダ U2 を通過します。したがって、B が A より位相進み (時計回り)の場合、U2 はハイ・レベルの U/D 信号を AD5227 に供給します。逆の場合は逆になります。U2 は、ノイズ、ジッタ、その他の過渡電圧、さらに U1 で発生する接点バウンスもフィルタで除去します。

従来型のダイアル・インターフェースで AD5111、AD5113、AD5115 を制御する方法については、AN-1150 アプリケーション・ノートを参照してください。

6 ビット・コントローラ

AD5227 をクロック・ジェネレータ、コンパレータ、出力部品と組み合わせて使うと、シンプルな 6 ビット・コントローラを構成することができます。 図 15 に、コンパレータを備えた一般的な 6 ビット・コントローラを示します。このコンパレータはサンプリング出力をリファレンス・レベルと比較して、ハイ・レベルまたはロー・レベルを AD5227 U/D ピンへ出力します。次に AD5227 は U/D の状態で表示される方向に各クロック・サイクルでステップを変化させます。この回路は自己充足的で、デザインが容易なため、種々のアプリケーションで使用することができます。

図 15.6 ビット・コントローラ

本の I2C バス上の複数のデバイス

AD5253/AD5254 には 2 本のアドレッシング・ピン AD1 と AD0があります。これらのピンを使うと、1 本の I2C バス上で最大 4個の AD5253/AD5254 を動作させることができます。これを実現するには、最初に各デバイスで AD1 と AD0 の状態を定義しておく必要があります。

表 2 と図 16 に例を示します。I2C による書込みでは、各デバイスにはアドレス指定のために異なるスレーブ・アドレス-01011(AD1)(AD0)-が発行されます。

| AD1 | AD0 | Device Addressed |

| 0 | 0 | U1 |

| 0 | 1 | U2 |

| 1 | 0 | U3 |

| 1 | 1 | U4 |

図 16.1 本のバス上の複数の AD5253/AD5254 デバイス

デジタル・ポテンショメータのアレイを使ってパワー・アンプをバイアスするワイヤレス基地局のスマート・アンテナ・システムでは、外付けのデコーダ、スイッチ、I/O バスを使って多数の AD5253/AD5254 をアドレス指定します(図 16 参照)。例えば、合計 16 個のデバイスと通信するためには、4 個のデコーダと 16 セットの組み合わせスイッチが必要です(図 16 では 4 セットのみ表示)。2 本の I/O バスは 4 個の 2 × 4 デコーダの共通入力として機能し、各組み合わせで 4 セットの出力を選択します。図 16 に示すように 4 セットの組み合わせスイッチ出力はユニークであるため、I2C を 01011(AD1)(AD0)と定義したスレーブ・アドレスでプログラミングすることにより特定のデバイスをアドレス指定することができます。

この動作を使うと、2 個のデコーダの入力状態が変化しない限り、16 個のデバイスの中から 1 個をアドレス指定することができます。特定のデバイスの動作が完了した後は、デコーダの入力を変更することができます。

双方向インターフェース用のレベル・シフト

大部分の従来型システムは 1 つの電圧で動作できますが、新しい部品は別の電圧で最適化されていることがあります。2 つのシステムが同じ信号を異なる 2 つの電圧で動作させる場合、レベル・シフトが必要です。例えば、3.3 V の EEPROM を使い、5 V のデジタル・ポテンショメータにインターフェースさせることがあります。デジタル・ポテンショメータの設定値をEEPROM に読み書きする双方向通信を可能にするにはレベル・シフト方式が必要となります。 図 17 に、レベル・シフト構成の 1 つを示します。M1 と M2 には N チャンネル信号 FET を使うことができ、あるいは VDDが 2.5 V を下回る場合、M1 と M2に FDV301N のような低スレッショールド FET を使うことができます。この回路は 1.8 V ロジック・レベルには適しません。

図 17.異なる電圧での動作のためのレベル・シフト

ゲイン

次の回路は DC 動作向けにデザインされています。この回路をAC 信号による励起と組み合わせて使うと、不安定性の問題が生じることがあります。回路の発振を防止するため、帰還ループ内に 10 pF のコンデンサを接続することを推奨します。

さらに、推奨オペアンプを置き換える場合は、次の制約に注意してください。

GBP < BW (Vout)

ここで、

C は VOUT ピンに接続された合計容量(ピン容量)。

ROUT はアンプの出力インピーダンス。

ROUT は一般にデータシートの仕様または代表的性能特性のプロットで規定されます。アナログ・ダイアログの記事「Practical Techniques to Avoid Instability Due to Capacitive Loading」Volume38、Number 2、2004 年を参照してください。

リニア・ゲイン設定モード

詳細については、AN-1169 アプリケーション・ノート「Linear Setting Mode: A Detailed Description」を参照してください。

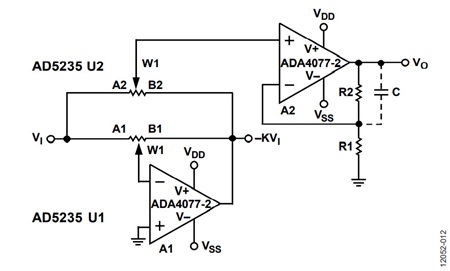

バイポーラ・プログラマブル・ゲイン・アンプ

バイポーラ・ゲインを必要とするアプリケーションの場合の一例を図 15 に示します。デジタル・ポテンショメータ U1 が調整範囲を設定し、U2 の設定に対して、ワイパー電圧(VW2)を VI~ -KVIの範囲で調整します。

ADA4077-2 (A2)を次の伝達関数を与える非反転アンプとして構成します。

ここで、K は U1 によって設定される比 RWB1/RWA1です。

簡単な(通常の)ケースでは、K = 1 であり、VO は次のように簡単になります。

ADA4077-2 (A2)をゲイン= 1、ゲイン= 2、ゲイン= 10 に設定して、D2 を調整した結果を表 3 に示します。リニアにプログラマブルなゲインと 1024 ステップの分解能を持つバイポーラ・アンプが得られます。

| D2 | R1 = ∞, R2 = 0 | R1 = R2 | R2 = 9 × R1 |

| 0 | -1 | -2 | -10 |

| 256 | -0.5 | -1 | -5 |

| 512 | 0 | 0 | 0 |

| 768 | 0.5 | 0 | 5 |

| 1023 | 0.992 | 1.984 | 9.92 |

ゲイン制御補償

デジタル・ポテンショメータは、非反転ゲイン・アンプとして広くゲイン制御で使われています(図 19 参照)。

図 19.ゲイン制御補償

RDAC の B ピンの寄生容量がオペアンプの非反転ノードに接続されると、1/βOの項にゼロ点が導入され 20 dB/dec となります。これに対して、代表的なオペアンプのゲイン帯域幅積(GBP)は-20 dB/dec の特性を持っています。大きな R2 と有限の C1 により、ゼロ周波数をクロスオーバー周波数より十分低くすることが可能です。このため、ゲイン勾配は 40 dB/dec になり、クロスオーバー周波数でのシステム位相マージンは 0°になります。入力に方形波パルスまたはステップ関数を入力した場合、出力にリンギングまたは発振が発生します。また、2 つのゲイン値の間で切り替えを行うことは、入力にステップを与えることと等価なため、同様にリンギングが発生します。

オペアンプの GBP に応じて、帰還抵抗を小さくすると、ゼロ周波数を十分遠くに持って行くことができるためこの問題を克服することができます。しかし、補償コンデンサ C2 を使用してC1 の影響を相殺する方法の方が優れています。最適補償は R1 ×C1 = R2 × C2 のとき得られます。R2 が変化するためこれは選択肢にはなりません。したがって、前述の関係を使い、R2 が最大値であるかのように C2 を調整することができます。R2 を小さい値に設定した場合、過補償になり性能が犠牲になることがあります。

その代り、最悪ケースでもリンギングや発振を防止することができます。クリティカルなアプリケーションに対しては、発振に適する C2 値を経験的に探す必要があります。一般に、数 pF~10 分の数 pF の範囲の C2 が補償に適しています。

同様に、W ピンと A ピンの容量は出力に接続されます(非表示)。このノードの影響は大きくないため、多くの場合補償する必要はありません。

LED ドライバ

手動調整可能な LED ドライバ

AD5228 は、LCD パネルのバックライト制御用の LED ドライバなどの多くの電気的レベル調整で使用することができます。 図20 に、手動で調整可能な LED ドライバを示します。AD5228 は、輝度制御用白色 LED D1 両端の電圧を設定します。U2 は最大250 mA を処理できるため、 VF が 3.5 V の代表的な白色 LED では、U2 電流を制限する抵抗 R1 が必要です。この回路はシンプルですが、電力効率はよくありません。U2 のシャットダウン・ピンを PWM 信号でトグルして、消費電力を減らすことができます。

図 20.低価格の調整可能な LED ドライバ

LED ドライバ向けの調整可能電流源

LED 輝度は順方向電圧ではなく電流の関数であるため、電圧源より調整可能な電流源の方が望まれます (図 21 参照)。

図 21.LED ドライバ向けの調整可能な電流源

負荷電流は、AD5227 の VWBを RSETで除算して求められます。

U1 の ADP3333ARMZ-1.5 は 1.5 V の LDO で、0 V の上下に上げ下げされます。AD5227 の VWBが最小値の場合、D1 を流れる電流はゼロで、U3 を両電源でバイアスした場合 U1 の GND ピンは−1.5 V になります。このため、幾つかの U2 に小さい抵抗ステップ変化があっても、U1 の GND ピンが 0 V より上にリフトされるまで、出力に影響を与えません。

AD5227 の VWBが最大値のとき、VOUTが VL + VABになるため、U1 の 電源電圧は十分なヘッドルームを持ってバイアスする必要があります。同様に、PWM 信号を U1 のシャットダウン・ピンに入力して、電力効率をよくすることができます。この回路は 1 個の LED に対してよく機能します。

電圧/電流変換

電圧 /電流変換: プログラマブルな電流源

図 22 に示す回路を使うと、高精度な電流源を構成することができます。

図 22.プログラマブルな電流源

REF191 は低電源ヘッドルーム高精度リファレンスであり、2.048 V で必要とされる 20 mA を供給することができます。負荷電流は、単純にデジタル・ポテンショメータの B ピンと W ピン の間の電圧を RSで除算した値になります。

回路は単純ですが、2 つの問題に注意する必要があります。先ず、REF191 のグラウンド電位は-2.048 V (ポテンショメータ設定のゼロスケール)から VL (ポテンショメータ設定のフルスケール)まで変化できるため、両電源オペアンプが最適です。回路は単電源でも動作しますが、システムのプログラマブルな分解能は低下します。2 つ目は、VL での電圧コンプライアンスが 2.5 V、すなわち等価負荷 125 Ω に制限されることです。高い電圧コンプライアンスが必要な場合は、デジタル・ポテンショメータ AD5260、AD5280、AD7376 が検討対象になります。 .

図 22 に、高電圧に適合する別の回路を示します。高電力 LEDの駆動などで高電流を実現するためには、U1 を LDO で置き換え、RSを小さくし、デジタル・ポテンショメータの A ピンに直列に抵抗を追加します。これにより、ポテンショメータの電流が制限されて、電流調整分解能が向上します。

電圧/電流変換: プログラマブルな双方向電流源

双方向電流制御や高い電圧コンプライアンスが必要なアプリケーションに対しては、Howland 社の電流ポンプが 1 つのソリューションになります。

図 23.プログラマブルな双方向電流源

抵抗が整合している場合、負荷電流は次式で与えられます。

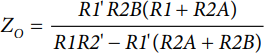

理論的には R2B を必要なだけ小さくして、A2 内部での出力電流駆動能力に必要な電流を得ることができます。この回路で、ADA4077-2 は両方向に±5 mA を供給し、電圧コンプライアンスは 15 V に近づきます。出力インピーダンスは次式で表されます。

抵抗 R1 と R2 がそれぞれ R1 と R2A + R2B に正確に整合すると、ZO は無限大になります。一方、抵抗が整合してない場合、ZO が負になることがあります。

そのため、1 pF ~ 10 pF の範囲の C1 を接続して、負インピーダンスによる発振を防止する必要があります。

フィルタ機能

プログラマブルなローパス・フィルタ

A/D 変換では、サンプリング信号の帯域を制限するアンチエイリアシング(折返し誤差防止)・フィルタを使用することが一般的です。このため、2 チャンネルの AD5235 を使って、2 次Sallen-Key ローパス・フィルタを構成することができます(図24 参照)。

図 24.Sallen-Key ローパス・フィルタ

設計式は、

先ず、コンデンサに対して手頃な値を選択します。Q = 0.707 となる最も平坦な帯域幅を実現するため、C1 のサイズを C2 の 2倍にして、R1 = R2 とします。R1 と R2 を同じ設定に同時に調整して、所望の帯域幅を実現します。

プログラマブルな状態可変フィルタ

状態可変アクティブ・フィルタは、ローパスまたはバンドパス・フィルタの作成に使用される標準的な回路の 1 つです。AD5233 をこのアプリケーションで使うと、周波数、ゲイン、フィルタ出力の Q の全てがプログラム可能になります。

±2.5 V のピーク入力/出力振幅を可能にする 2.5 V の仮想グラウンドを使用したフィルタ回路を図 25 に示します。RDAC2 とRDAC3 がローパス、ハイパス、バンドパスのカットオフと中心周波数をそれぞれ設定しています。RDAC2 と RDAC3 には (連動ポテンショメータの場合と同様)同じデータを設定して、回路 の最適な Q を維持します。

図 25.プログラマブルな状態可変フィルタ

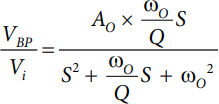

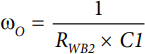

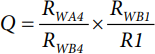

バンドパス・フィルタの伝達関数は、

ここで、AOはゲイン。

RWB2(D2) = RWB3(D3)の場合、R1 = R2 かつ C1 = C2、

バンドパス出力でのフィルタ応答の測定値は 2 kHz~20 kHz の中心周波数範囲を発生させる RDAC2 と RDAC3 の設定値の関数であることを図 25 は示しています。

バンドパス出力でのフィルタ・ゲイン応答を図 25 に示します。中心周波数 2 kHz で、ゲインは−20 dB~+20 dB の範囲で調節され、RDAC1 により決定されます。回路 Q は RDAC4 と RDAC1により調節されます。このアプリケーションに適するオペアンプは、ADA4077-2、AD8604、OP279、AD824 です。

その他の応用

出力ブースタ付きプログラマブル電圧源

大電流の調整が必要となるレーザ・ダイオード・ドライバまたはチューナブル・レーザのようなアプリケーションの場合、ブースト電圧源の使用を検討することができます(図 26 参照)。

図 26.プログラマブルなブースト電圧源

この回路では、オペアンプの反転入力が VOをデジタル・ポテンショメータで設定されたワイパー電圧に等しくなるよう強制します。負荷電流は、N チャンネル FET の N1を経由して電源から供給されます(図 26 参照)。N1 の電力処理能力は、(VI − VO)× ILの電力消費に対して十分である必要があります。

この回路は 5 V 電源で最大 100 mA を出力することができます。高精度なアプリケーションに対しては、ADR421 または ADR03のような電圧リファレンスを、デジタル・ポテンショメータのA ピンに接続することができます。

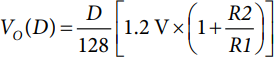

高電圧 DAC

AD7376 を最大 30 V の高電圧 DAC として構成することができます。回路を図 27 に示します。出力は次のようになります。

ここで、D は 0~127 の 10 進コード。

27.高電圧 DAC

プログラマブルなオシレータ

従来型 Wien ブリッジ発振器では、Wien 回路 (R||C、R'C')が正帰還を提供し、R1 と R2 が負帰還を提供します。

図 28.振幅制御機能付きプログラマブル・オシレータ

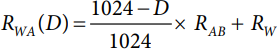

共振周波数 fo で全体の位相シフトがゼロになるため、正帰還により回路が発振します。R = R'、C = C'、R2 = R2A/(R2B +RDIODE) の場合、発振周波数は次式で与えられます。

Or

ここで、R = RWAとなり、

共振周波数では、R2/R1 = 2 に設定すると、ブリッジが平衡します。実用的には、R2/R1 を 2 より少し大きい値に設定して、発振の開始を確実にします。一方、ダイオード D1 と D2 の交互ターンオンにより、R2/R1 が確実に 2 より小さくなるので、直ちに発振を安定化します。周波数を設定した後、発振振幅を R2Bにより調整します。次の関係を使います。

VO、ID、VD は相互に依存する変数です。R2B を適切に選択すると、VO が収束して平衡状態が得られます。R2B をディスクリート抵抗と直列にして、振幅を大きくすることができますが、合計抵抗は出力が飽和するのであまり大きくすることはできません。

電源を使用した常時バイアスによる抵抗設定値の保持

EEMEM ポテンショメータを使用したいが、コスト増とデザインのプログラミングを許容できない場合は、電源によるAD5227 の常時バイアスを使った抵抗設定値の保持を検討してください (図 29 参照)

図 29.AD5227 の常時バイアスによる抵抗値の保持

AD5227 は、バッテリ駆動システムでも消費電力を節約できるように特別に低消費電力に設計されています。図 30 に示すように、同じような低消費電力デジタル・ポテンショメータを 3.4 V450 mA/hour のリチウムイオン携帯電話バッテリでバイアスします。計測値は、デバイスの消費電力は無視できることを示しています。ポテンショメータの常時バイアスは実用的な方法です。これは、大部分の携帯型機器では充電時にバッテリを取り外す必要がないためです。バッテリの交換の際に AD5227 の抵抗設定値が失われるとしても、多くのアプリケーションで不都合になるほど頻繁には発生しません。

図 30.バッテリ消費電力の測定値