ADRV9040

新規設計に推奨DFE、400MHz iBW RFトランシーバーを実装した8T8R SoC

- 製品モデル

- 1

- 1Ku当たりの価格

- 価格は未定

製品情報

- 8つの差動トランスミッタ(Tx)

- 8つの差動レシーバー(Rx)

- 2つのオブザベーション・レシーバー

- シングルバンドおよびマルチバンド(N x 2T2R/4T4R)機能

- 調整可能範囲内の4つの個別バンド・プロファイル1

- 調整可能範囲:650MHz~6000MHz

- 400MHz iBW、DPD対応

- ハードウェア・アクセラレート、電荷トラッピング補正アルゴリズムによりGaN PAに対応

- JESD204B/JESD204Cデジタル・インターフェースに対応

- すべてのLOおよびベースバンド・クロック用マルチチップ位相同期

- フル統合型フラクショナルN RFシンセサイザ

- システム温度ソリューションを簡略化

- 13Wの低消費電力(すべてのブロックを有効にした場合)2

- 最大ジャンクション温度は110℃、最大125°Cで動作3

- 完全内蔵型のDFE(DPD、CDUC、CDDC、CFR)エンジンにより、FPGAが不要となり、SERDESレーン・レートを半減

- パワー・アンプ直線化用のDPDアダプテーション・エンジン

- Tx/Rxチャンネルあたり最大8個のコンポーネントキャリア(CC)

- マルチステージCFRエンジン

- 完全内蔵型のクロック・シンセサイザ

1 バンド・プロファイルで、帯域幅とチャンネルの総合サンプリング・レートを定義します。 |

ADRV9040は、高度に集積化されたシステム・オン・チップ(SoC)のラジオ周波数(RF)アジャイル・トランシーバーで、集積化されたデジタル・フロント・エンド(DFE)を搭載しています。SoCには、8個のトランスミッタ、トランスミッタ・チャンネル監視用の2個のオブザベーション・レシーバー、8個のレシーバー、集積化されたLOおよびクロック・シンセサイザ、デジタル信号処理回路が搭載されています。また、スモール・セル基地局無線、マクロ3G/4G/5Gシステム、Massive MIMO(Multiple Input Multiple Output)基地局などのセルラ・インフラストラクチャ・アプリケーションに要求される、高い無線性能および低消費電力の要件を満たしています。

RxとTxの信号経路にはゼロIF(ZIF)アーキテクチャが使用され、連続/非連続マルチキャリア基地局のアプリケーションに適したダイナミック・レンジを持つ広帯域幅を提供します。ZIFアーキテクチャの長所は、低消費電力およびRF周波数と帯域幅のアジリティです。エイリアスおよび帯域外イメージが除去されるため、アンチエイリアス・フィルタとイメージ・フィルタが不要になります。これにより、システムの小型化とコスト削減の両方が実現します。また、帯域を独立させるソリューションが可能になります。

また、トランスミッタ出力を監視するための、広帯域幅のオブザベーション・パス・レシーバー・サブシステムを2個内蔵しています。このSoCサブシステムは、自動および手動の減衰制御、DCオフセット補正回路、直交誤差補正回路(QEC)、およびデジタル・フィルタリングの機能を備えてます。また、多数のデジタル制御オプションを提供するGPIOも内蔵されています。

デュアルLO機能、追加のLO分周器、および広帯域動作により、マルチバンド機能が有効になります。これにより、調整可能範囲内の4つの個別バンド・プロファイル1が可能になり、ユースケースの柔軟性を最大限まで高めることができます。

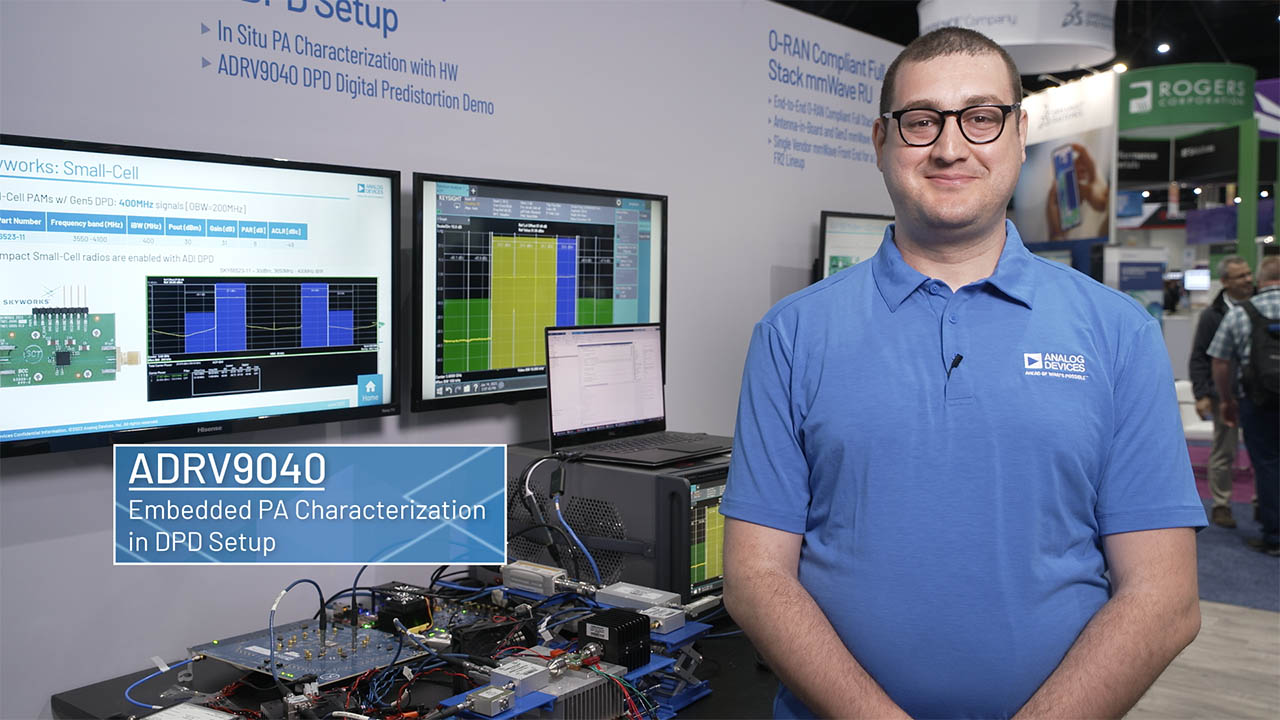

SoCは、高集積のデジタル・フロント・エンド(DFE)機能を備えています。これには、キャリア・デジタル・アップ/ダウン・コンバージョン(CDUC/CDDC)、クレスト・ファクタ低減(CFR)、デジタル・プリディストーション(DPD)、クローズド・ループ・ゲイン制御(CLGC)、および電圧定在波比(VSWR)モニタが含まれます。

ADRV9040のCDUC機能により、対象帯域内で個々の部品のキャリアをフィルタリングして配置します。CDDC機能は8個の並列回路を備え、シリアル・データ・インターフェースを介して送信する前に、各キャリアを個々に処理します。

CDUCおよびCDDCにより、非連続のキャリア設定において、SERDESインターフェースに必要なデータ・レートを軽減します。これにより、同等のFPGAベースの実装と比べ、消費電力も削減されます。

ADRV9040のCFRエンジンは、入力信号のピーク値と平均値の比を小さくして、ベースバンド・プロセッサの処理負荷を軽減しながら、効率の高い送信系列を実現します。

SoCには、パワー・アンプ(PA)直線化用の完全内蔵型DPDエンジンも搭載されています。DPDによって、高効率のPAを使用できるようになるため、基地局無線の消費電力を低減し、ベースバンド・プロセッサとのインターフェース接続に必要なSERDESレーンの数を削減することができます。DPDエンジンには、GaN PAに対応する専用の長期DPD(LT-DPD)ブロックが組み込まれています。ADRV9040では、LT-DPDブロックを使用してGaN PAの電荷トラッピングの特性に対処することで、放射とEVMが向上します。SoCには、ARM Cortex-A55クワッド・コア・プロセッサが搭載され、DPD、CLGC、およびVSWRモニタの機能を個別に提供します。DPDエンジンと専用のプロセッサにより、業界をリードするDPD性能を実現します。

シリアル・データ・インターフェースは、8つのシリアライザ・レーンと8つのデシリアライザ・レーンで構成されています。インターフェースはJESD204B規格およびJESD204C規格の両方をサポートし、固定小数点と浮動小数点の両方のデータ・フォーマットに対応しています。浮動小数点フォーマットを選択すると、内部自動ゲイン制御(AGC)が可能になり、ベースバンド・プロセッサに対してトランスペアレントになります。

ADRV9040は0.8V、1.0V、1.8Vのレギュレータから直接給電し、標準SPIのシリアル・ポートで制御します。また、通常使用の消費電力を最小限に抑えるために、包括的パワーダウン・モードを搭載しています。デバイスは、27mm × 20mm、736ボールのグリッド・アレイ・パッケージを採用しています。

アプリケーション

- 3G/4G/5G TDD/FDDスモール・セル、Massive MIMO、およびマクロ・セル基地局

ドキュメント

データシート 2

アプリケーション・ノート 7

技術記事 3

製品ハイライト 1

秘密保持契約(NDA)をリクエスト

技術文書一式は、秘密保持契約(NDA)の締結後にご利用いただけます。

秘密保持契約(NDA)をリクエストビデオ 3

ウェブキャスト 1

製品ハイライト 1

ソート・リーダーシップ 1

珍問/難問集 1

アナログ・ダイアログ 2

| 製品モデル | ピン/パッケージ図 | 資料 | CADシンボル、フットプリント、および3Dモデル |

|---|---|---|---|

| AD80560DLIC | NON PHYSICAL PRODUCT |

これは最新改訂バージョンのデータシートです。

ソフトウェア・リソース

APIデバイス・ドライバ 1

デバイスのアプリケーション・プログラミング・インターフェース(API)のC言語ドライバは、参照用コードとして提供されており、ユーザーが、高度な関数呼び出しを使用して製品を迅速に設定できるようにします。このライブラリは、アプリケーションとハードウェアの間で抽象化レイヤとして機能します。APIはC言語のC99で開発されており、プロセッサとオペレーティング・システムに依存しない統合を保証しています。プラットフォーム固有のコード・ベースをAPI HAL層に統合することで、このアプリケーション層のコードを組込みシステム/ベースバンド・プロセッサに移植することができます。このソフトウェア・パッケージをリクエストするには、MyAnalogアカウントでサイン・インした状態でソフトウェアのリクエスト・フォームにアクセスし、対象テクノロジーの項目で「Wireless Communications(ワイヤレス通信)」を選択し、「Processor/SOC (プロセッサ/SOC)」でADRV9040またはADRV9044を選択し、チェックボックスも選んでからフォームを送信してください。ソフトウェア・ダウンロードのためのリンク付きのメール通知が送信されます。

評価用ソフトウェア 1

必要なソフトウェア/ドライバが見つかりませんか?

ハードウェア・エコシステム

| 製品モデル | 製品ライフサイクル | 詳細 |

|---|---|---|

| RFスイッチ 1 | ||

| ADRF5250 | 新規設計に推奨 | 0.1 GHz to 6 GHz Silicon SP5T Switch |

| アンプベースのフロント・エンド 2 | ||

| ADRF5515A | 新規設計に推奨 | デュアル・チャンネル、3.3GHz~4.0GHz、20Wのレシーバー・フロント・エンド |

| ADRF5515 | 新規設計に推奨 |

デュアル・チャンネル、3.3GHz~4.0GHz、20Wレシーバー・フロント・エンド |

| クロックIC 2 | ||

| AD9528 | 新規設計に推奨 |

クロック・ジェネレータ、14 LVDS / HSTL出力、JESD204B対応 |

| AD9545 | 新規設計に推奨 | IEEE1588 バージョン 2 および 1 pps シンクロナイザおよび適応型クロック変換器 |

| スイッチング・レギュレータ & コントローラ 5 | ||

| LT83205 | 新規設計に推奨 | 18V、5A超低ノイズ・リファレンス付き降圧Silent Switcher®(サイレント・スイッチャ)3 |

| MAX20840T | 製造中 | 40A、2MHz、2.7V~16Vの統合型降圧スイッチング・レギュレータ(PMBus搭載) |

|

LT8625SP/ LT8625SP-1 |

18V/8A、超低ノイズ・リファレンス付き降圧Silent Switcher®(サイレント・スイッチャ)3 | |

| ADP5056 | 新規設計に推奨 | トリプル降圧レギュレータ内蔵の電源ソリューション |

| LT8627SP | 新規設計に推奨 | 18V/16A超低ノイズリファレンス内蔵降圧Silent Switcher®(サイレント・スイッチャ)3 |

| ロー・ノイズ・アンプ(LNA)&パワー・アンプ 2 | ||

| ADL5545 | 新規設計に推奨 | RF / IFゲイン・ブロック、30MHz~6GHz |

| ADL5611 | 新規設計に推奨 | RF/IFゲイン・ブロック、30 MHz ~ 6 GHz |