AD4080

新規設計に推奨20ビット、40MSPSの差動SAR ADC

低ノイズ、低消費電力、高速、高精度のSAR ADC

- 製品モデル

- 3

- 1Ku当たりの価格

- 最低価格:$55.99

製品情報

- 高性能

- スループット:40MSPS、46.25nsの変換レイテンシ

- INL:±4ppm(代表値)、±8ppm(最大値)

- SNR/THD

- fIN = 1kHzで、93.6dB(代表値)/−110dB(代表値)

- fIN = 1MHzで、93.5dB(代表値)/−104dB(代表値)

- ノイズ・スペクトル密度:−167.6dBFS/Hz

- 20ビット分解能、ノー・ミッシング・コード

- 低消費電力

- 40MSPS、−0.5dBFS正弦波入力で79.3mW(代表値)

- Easy Drive、完全差動入力

- 6V p-pの 差動入力レンジ

- 連続信号アクイジション

- 5μA/MSPSの入力電流を直線化

- 低ドリフトのリファレンス・バッファおよびデカップリングを内蔵

- VCM生成を内蔵

- デジタル機能とデータ・インターフェース

- 変換結果FIFO、16Kのサンプル深さ

- 最大210デシメーションのデジタル平均化フィルタ

- SPI設定

- データ・インターフェースを設定可能

- シングル・レーン、DDR、シリアルLVDS、レーンあたり800MBPS

- デュアル・レーン、DDR、シリアルLVDS、レーンあたり400MBPS

- シングル/クワッド・レーンSPIデータ・インターフェース

- パッケージ

- 49ボール、5mm × 5mm CSP_BGA、0.65mmピッチ

- 電源デカップリング・コンデンサを内蔵

- 動作温度範囲:−40°C~+85°C

AD4080は、高速、低ノイズ、低歪み、20ビット、Easy DriveのSAR(逐次比較レジスタ)ADC(A/Dコンバータ)です。AD4080は、1MHzを超える信号周波数で高い性能(信号/ノイズ + 歪み(SINAD)比 > 90dBFS)を維持することにより、様々な高精度で広帯域幅のデータ・アクイジション・アプリケーションに対応できます。入力アンチエイリアス・フィルタ設計の簡素化は、内蔵デジタル・フィルタリングおよびデシメーションと共にオーバーサンプリングを適用して、AD4080の最低レイテンシが不要なアプリケーションに対して、ノイズを低減し、出力データレートを下げることによって実現できます。

AD4080のEasy Drive機能は、シグナル・チェーンの複雑さと消費電力の両方を低減すると同時に、チャンネル密度の向上と関連部品の選択の柔軟性を実現します。本製品の入力構造は、任意の入力依存信号電流を最小化するように設計されているため、任意のコンバータ誘導性セトリング・アーチファクトを低減します。連続アクイジション・アーキテクチャにより、変換サイクル全体にわたってセトリングが可能になり、他の高速データ・コンバータと比較して、ADCドライバ・セトリングおよび帯域幅条件が緩和されます。

AD4080には、低ドリフトのリファレンス・バッファ、ADCコアおよびデジタル・インターフェース電源レールを生成するための低ドロップアウト(LDO)レギュレータ、およびデジタル・ホスト上の負荷を大幅に低減できる16K結果データの先入れ先出し(FIFO)など、データ・コンバータの統合を簡素化するいくつかの要素があります。更に、最適な性能を確保し、プリント基板(PCB)のレイアウトを簡素化し、ソリューション全体のフットプリントを縮小するために、重要な電源およびリファレンス・デカップリング・コンデンサがパッケージに内蔵されています。

アプリケーション

- デジタル・イメージング

- バッテリのセル解析

- 分光分析

- ATE(自動試験装置)

- 高速データ・アクイジション

- デジタル制御ループ、ハードウェア・イン・ザ・ループ

- 電力品質の解析

- ソース計測ユニット

- 電子およびX線顕微鏡

- レーダー・レベル測定

- 非破壊検査

- 予知保全と社会インフラ構造物の健全性管理

ソフトウェア・リソース

デバイス・ドライバ 1

必要なソフトウェア/ドライバが見つかりませんか?

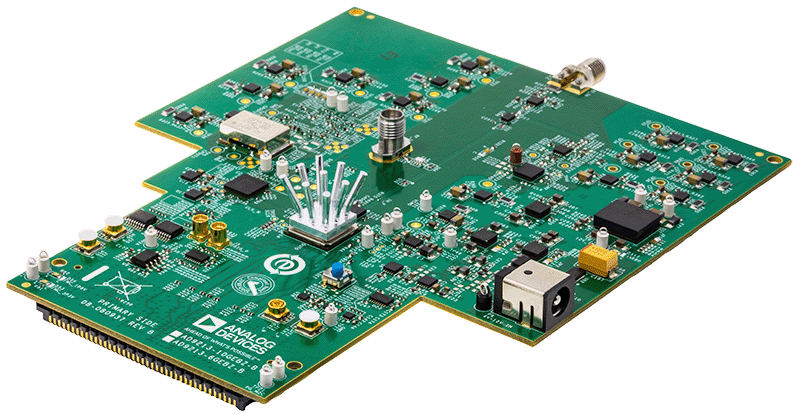

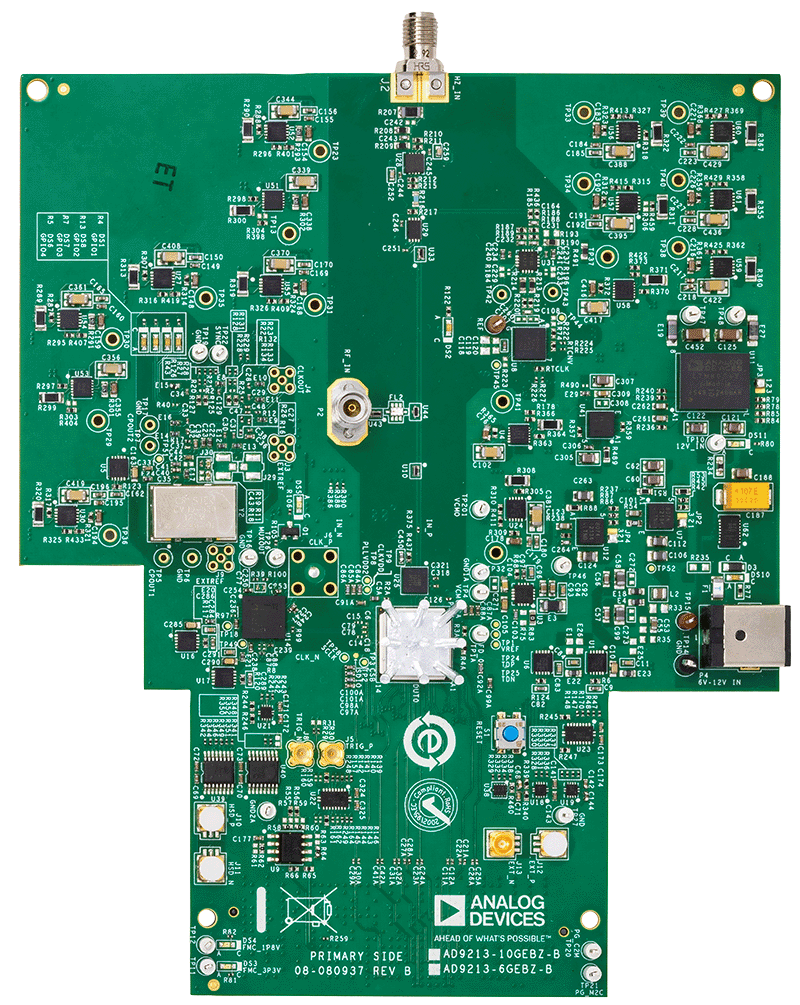

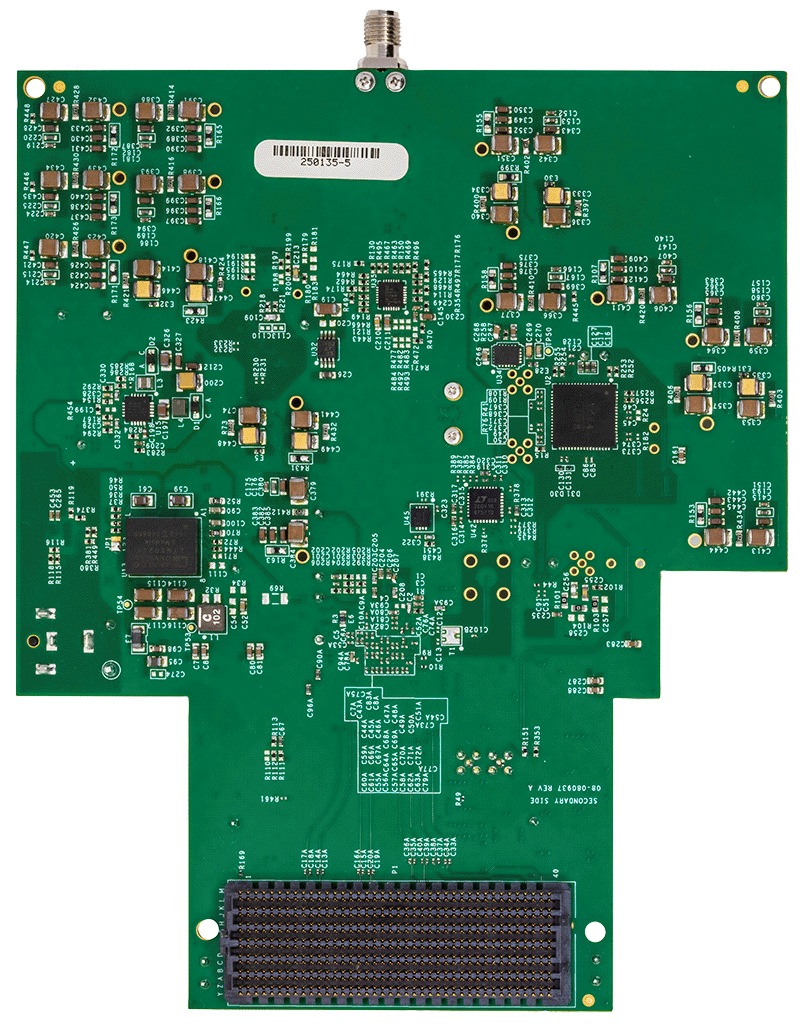

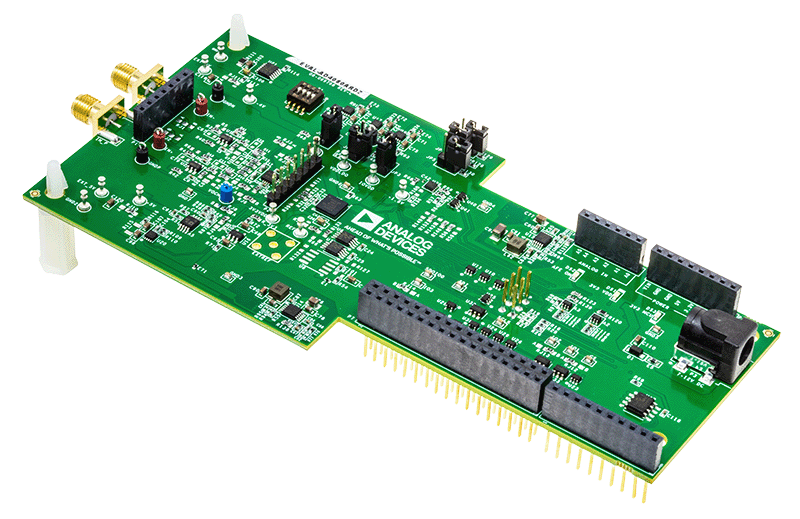

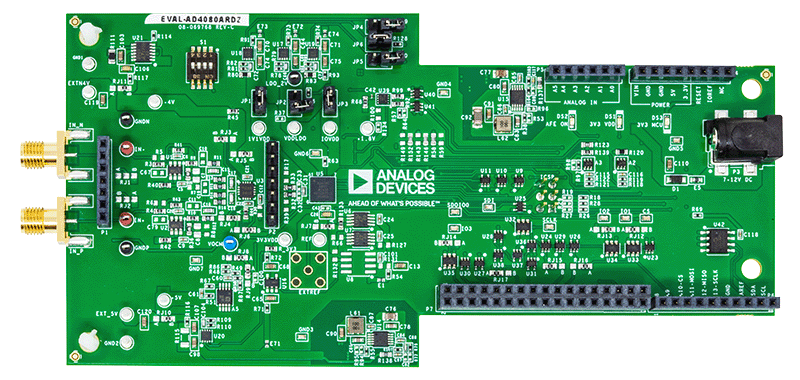

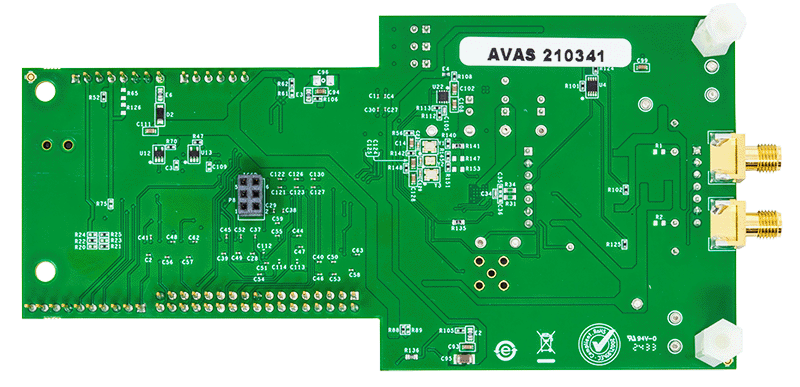

ハードウェア・エコシステム

-

Flow Cytometry Signal Chain -

Power Optimized Data Acquisition -

Low Noise Wideband Data Acquisition

| 製品モデル | 製品ライフサイクル | 詳細 |

|---|---|---|

| オペアンプ(OPアンプ) 1 | ||

| ADA4899-1 | 製造中 | オペアンプ、高速、安定したユニティ・ゲイン、超低歪み、1nV/√Hz |

| スイッチング・レギュレータ & コントローラ 1 | ||

| LT8604 | 新規設計に推奨 | 高効率42V/120mA同期降圧 |

| ファンアウト・バッファ 1 | ||

| AD9508 | 新規設計に推奨 | クロック・ファンアウト・バッファ、1.65GHz、出力デバイダおよび遅延調整機能付 |

| フェーズ・ロック・ループ(PLL)シンセサイザ 1 | ||

| ADF4350 | 製造中 | 広帯域シンセサイザ、VCO内蔵 |

| リニア・レギュレータ 4 | ||

| LT3045 | 新規設計に推奨 | 20V、500mA、超低ノイズ、超高PSRRのリニア・レギュレータ |

| ADP150 | 製造中 | リニア・レギュレータ、150mA、超低ノイズ、CMOS |

| MAX38912 | 新規設計に推奨 | 11µVRMS低ノイズ、500mA LDOリニアレギュレータ、低電力モード内蔵 |

| LT3045-1 | 新規設計に推奨 | 20V、500mA、超低ノイズ、 VIOC制御を備える超高PSRRリニア・レギュレータ |

| 差動アンプ 2 | ||

| ADA4945-1 | 新規設計に推奨 | 高速でオフセット・ドリフトが ±0.1µV/°Cの完全差動ADC用ドライバ |

| ADA4930-1 | 新規設計に推奨 | 超低ノイズ・ドライバ・アンプ、低電圧 A/D コンバータ向け |

| 電圧リファレンス 2 | ||

| LTC6655 | 製造中 | ノイズが0.25ppmの低ドリフト高精度リファレンス |

| ADR4530 | 製造中 | 3.0V電圧リファレンス、超低ノイズ、高精度 |

ツールおよびシミュレーション

LTspice 1

下記製品はLTspiceで使用することが出来ます。:

- AD4080

Signal Chain Designer

Signal Chain Designerは、複雑な高精度シグナル・チェーンの構築、シミュレーションを行うために設計されたウェブベースのツールです。PCBを作成する前に、伝達関数、ノイズ、消費電力、入力範囲、DCエラーなど、回路の性能を確認できます。さまざまな部品やアーキテクチャを素早く試すことができます。シグナル・チェーンはLTspiceにエクスポートして更に解析を行うことができます。

ツールを開くIBISモデル 1

LTspice®は、無料で提供される強力で高速な回路シミュレータと回路図入力、波形ビューワに改善を加え、アナログ回路のシミュレーションを容易にするためのモデルを搭載しています。