ADRV9040

推荐用于新设计具有DFE、400MHz iBW射频收发器的8T8R SoC

- 产品模型

- 1

概述

- 8个差分发送器(Tx)

- 8个差分接收器(Rx)

- 2个观察接收器(ORx)

- 单频段和多频段(N x 2T2R/4T4R)能力

- 可调范围1内4个波段轮廓

- 调谐范围:650 MHz至6000 MHz

- 400MHz iBW DPD支持

- 通过硬件加速电荷捕捉纠正算法实现GaN PA支持

- 支持JESD204B/JESD204C数字接口

- 适用于所有LO和基带时钟的多芯片相位同步

- 完全集成的N部射频频率合成器

- 简化系统散热解决方案

- 所有区块实现13W功耗2

- 110°C最高结温,工作温度最高达125°3

- 完全集成的DFE(DPD、CDUC、CDDC、CFR)引擎,免除FPGA的需要,SERDES通道速率减半

- DPD自适应引擎,实现功率放大器的线性化

- CDUC/CDDC——每个Tx/Rx通路最多8个分量载波(CC)

- 多级CFR引擎

- 完全集成的时钟频率合成器

1波段轮廓定义信道带宽和总采样率。 |

ADRV9040是一款高度集成的片上系统(SoC)射频(RF)捷变收发器,配有集成式数字前端(DFE)。SoC包含8个收发器、2个用于监测发射器通道的观测接收器、8个接收器、集成LO和时钟合成器,以及数字信号处理功能。SoC满足蜂窝基础设施应用(包括小型蜂窝基站无线电、宏3G/4G/5G系统和大规模MIMO基站)所需的高射频性能和低功耗。

Rx和Tx信号路径采用零中频(ZIF)架构,提供适合连续和非连续多载波基站应用的宽带宽和动态范围。ZIF架构具有低功耗+射频和带宽灵活等优点。由于没有混叠和带外图像,因而不需要抗混叠和图像滤波器。这样就减小了系统尺寸和成本,同时支持与频带无关的解决方案。

该器件还包括两个宽带宽观测路径接收器子系统,用于监测发射器输出。该SoC子系统包括自动和手动衰减控制、直流失调校正、正交误差校正 (QEC) 以及数字滤波功能。此外,还集成了提供一系列数字控制选项的GPIO。

双LO功能、额外的LO分频器和宽带宽操作支持多频段功能。这样就在可调谐范围内有4个单独的频带曲线1,从而尽可能提高用例灵活性。

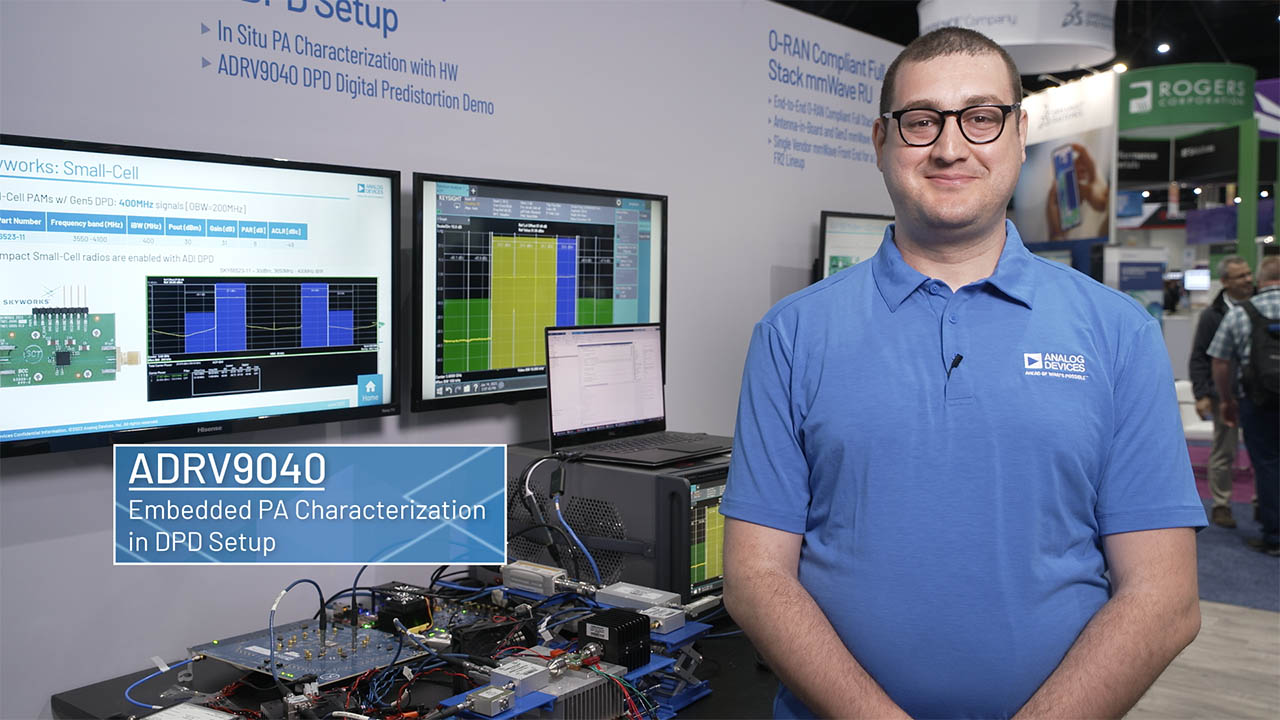

SoC具有完全集成的数字前端(DFE)功能,包括载波数字上/下变频(CDUC和CDDC)、削峰(CFR)、数字预失真(DPD)、闭环增益控制(CLGC)和电压驻波比(VSWR)监控。

ADRV9040的CDUC功能对目标频带内的单独分量载波进行滤波和放置。CDDC功能具有8个并行路径,对每个载波进行单独处理,再通过串行数据接口发送。

CDUC和CDDC降低了非连续载波配置中的SERDES接口数据速率。与基于FPGA的等效实现方案相比,这种集成设计还降低了功耗。

ADRV9040的CFR引擎降低了输入信号的峰均比(PAR),支持实现更高效率的传输线路升级,同时降低了基带处理器的处理负荷。

SoC还包含完全集成的DPD引擎,用于功率放大器(PA)线性化。DPD支持高效功率放大器,可减少基站无线电的功耗,以及与基带处理器接口所需的SERDES通道数量。DPD引擎包含一个长期专用的DPD (LT-DPD)模块,可为GaN PA提供支持。ADRV9040利用其LT-DPD模块解决了GaN PA的电荷捕获特性;因此改善了辐射和EVM性能。SoC包括一个ARM Cortex-A55四核处理器,可独立提供DPD、CLGC和VSWR监控功能。专用处理器与DPD引擎一起提供行业出色的DPD性能。

串行数据接口包括八个串行器通道和八个解串器通道。该接口支持JESD204B和JESD204C标准,支持固定和浮点数据格式。浮点格式使内部自动增益控制(AGC)对基带处理器可见。

ADRV9040可直接由0.8V、1.0V和1.8V稳压器供电,并通过一个标准SPI串行端口进行控制。全面的节电模式可尽量降低正常使用时的功耗。该器件采用27mm × 20mm、736引脚球栅阵列封装。

应用

- 3G/4G/5G TDD/FDD小型蜂窝、大规模MIMO和宏基站

参考资料

视频 2

产品亮点 1

模拟对话 2

非常见问题 1

思想领导力 1

ADI 始终高度重视提供符合最高质量和可靠性水平的产品。我们通过将质量和可靠性检查纳入产品和工艺设计的各个范围以及制造过程来实现这一目标。出货产品的“零缺陷”始终是我们的目标。查看我们的质量和可靠性计划和认证以了解更多信息。

| 产品型号 | 引脚/封装图-中文版 | 文档 | CAD 符号,脚注和 3D模型 |

|---|---|---|---|

| AD80560DLIC | NON PHYSICAL PRODUCT |

这是最新版本的数据手册

软件资源

API Device Drivers 1

Device Application Programming Interface (API) C code drivers provided as reference code allows the user to quickly configure the product using high-level function calls. The library acts as an abstraction layer between the application and the hardware. The API is developed in C99 to ensure agnostic processor and operating system integration. Customers can port this application layer code to their embedded systems/ Baseband Processor by integrating their platform-specific code base to the API HAL layer. To request this software package, go to the Software Request Form signed in with your MyAnalog account and under “Target Technology option - select “Wireless Communications" and choose processor/SOC as "ADRV9040 or ADRV9044" , select the check box as well and submit the form. You will receive an email notification with a link for software download.

Evaluation Software 1

ADRV904x Evaluation GUI SW Pkg.2.12.0.13

The ADRV904x Evaluation GUI package contains the ACE installation and the ADRV904x plugin required for evaluation with ADRv904x evaluation board. For Software package including API , firmware binary etc , please fill the software request form above.

找不到您所需的软件或驱动?

硬件生态系统

| 部分模型 | 产品周期 | 描述 |

|---|---|---|

| RF开关 1 | ||

| ADRF5250 | 推荐用于新设计 | 0.1 GHz至6 GHz硅SP5T开关 |

| 低噪声放大器(LNA)和功率放大器 2 | ||

| ADL5545 | 推荐用于新设计 | 30 MHz 至 6 GHz RF/IF 增益模块 |

| ADL5611 | 推荐用于新设计 | 30 MHz 至6 GHz RF/IF增益模块 |

| 基于放大器的前端 2 | ||

| ADRF5515A | 推荐用于新设计 | 双通道,3.3 GHz至4.0 GHz,20 W接收器前端 |

| ADRF5515 | 推荐用于新设计 |

双通道,3.3 GHz至4.0 GHz,20 W接收器前端 |

| 开关稳压器和控制器 5 | ||

| LT83205 | 推荐用于新设计 | 具有超低噪声基准电压源的 18V、5A 降压型 Silent Switcher 3 |

| MAX20840T | 量产 | 具有 PMBus 的 40A、2MHz、2.7V 至 16V 集成降压开关稳压器 |

|

LT8625SP/ LT8625SP-1 |

具有超低噪声基准电压源的18V/8A降压型Silent Switcher 3 | |

| ADP5056 | 推荐用于新设计 | 集成式三通道降压调节器电源解决方案 |

| LT8627SP | 推荐用于新设计 | 具有超低噪声的18V/16A降压型Silent Switcher 3 |

| 时钟IC 2 | ||

| AD9528 | 推荐用于新设计 | 提供14路LVDS/HSTL输出的JESD204B/JESD204C时钟发生器 |

| AD9545 | 推荐用于新设计 | IEEE1588 第 2 版以及 1 pps 同步器和自适应时钟转换器 |

工具及仿真模型

ADIsimRF

ADIsimRF是一款简单易用的RF信号链计算工具。可以计算和导出多达50级的信号链级联增益、噪声、失真和功耗并绘制其曲线。ADIsimRF还包括丰富的ADI射频和混合信号元件的器件模型数据库。

打开工具SDR Integrated Transceiver Design Resources

This site contains the device documentation packages for the SDR Integrated Transceivers including user guides, IBIS models, and PCB files.

打开工具评估套件

最新评论

需要发起讨论吗? 没有关于 ADRV9040的相关讨论?是否需要发起讨论?

在EngineerZone®上发起讨论