混合信号前端(MxFE)

ADI公司的混合信号前端(MxFE®)产品巧妙地集成了RF模数转换器(ADC)、RF数模转换器(DAC)、片内数字信号处理以及用于多芯片同步的时钟/PLL。这可以消除离散数据转换器和传统RF前端组件,从而缩小尺寸、减轻重量、降低功耗和成本。集成的数字信号处理功能支持向软件定义无线电平台转型,从而构建高度可配置的通用硬件/软件平台,该平台可在广泛的终端市场中用于多种应用场景。

查看产品选型表

Viewing:

分类产品

ADSY1100

预发布

4 Tx/4 Rx,0.1 GHz 至 20 GHz Apollo MxFE 3UVPX 调谐器 + 数字化仪 + 处理器

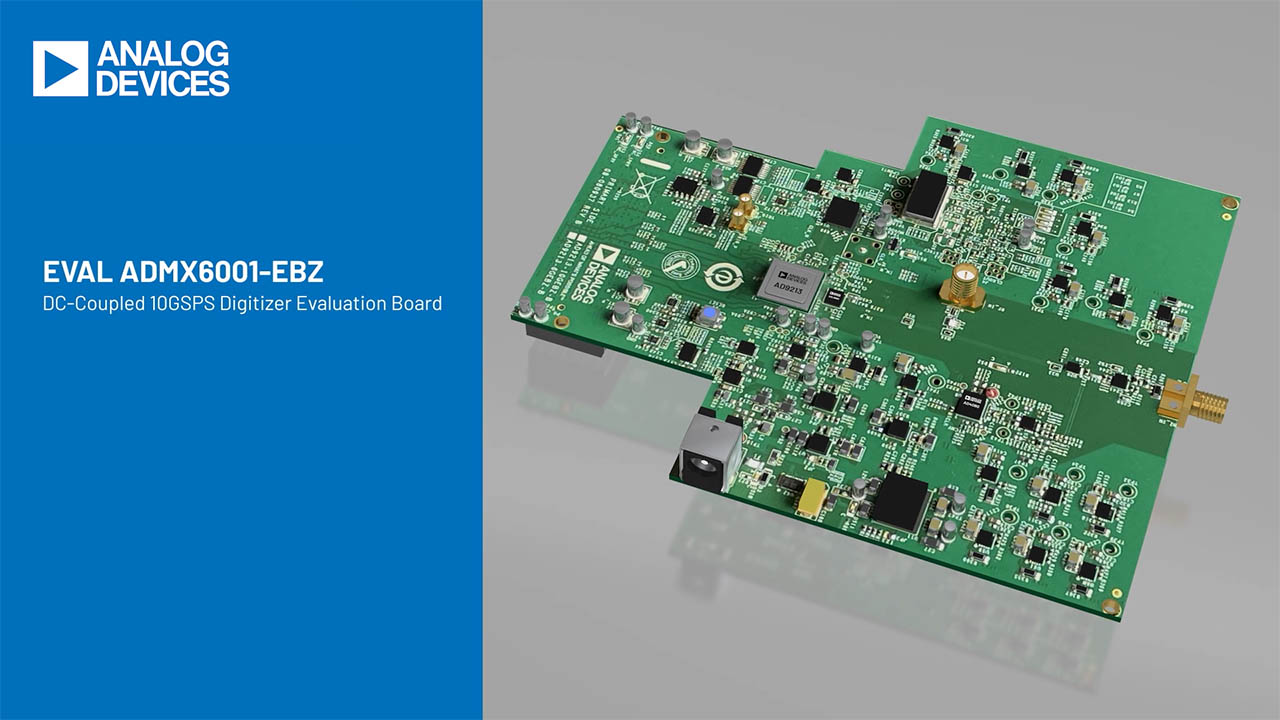

AD9088

推荐用于新设计

Apollo MxFE 八路、16 位、16 GSPS 射频 DAC 和八路、12 位、8 GSPS 射频 ADC

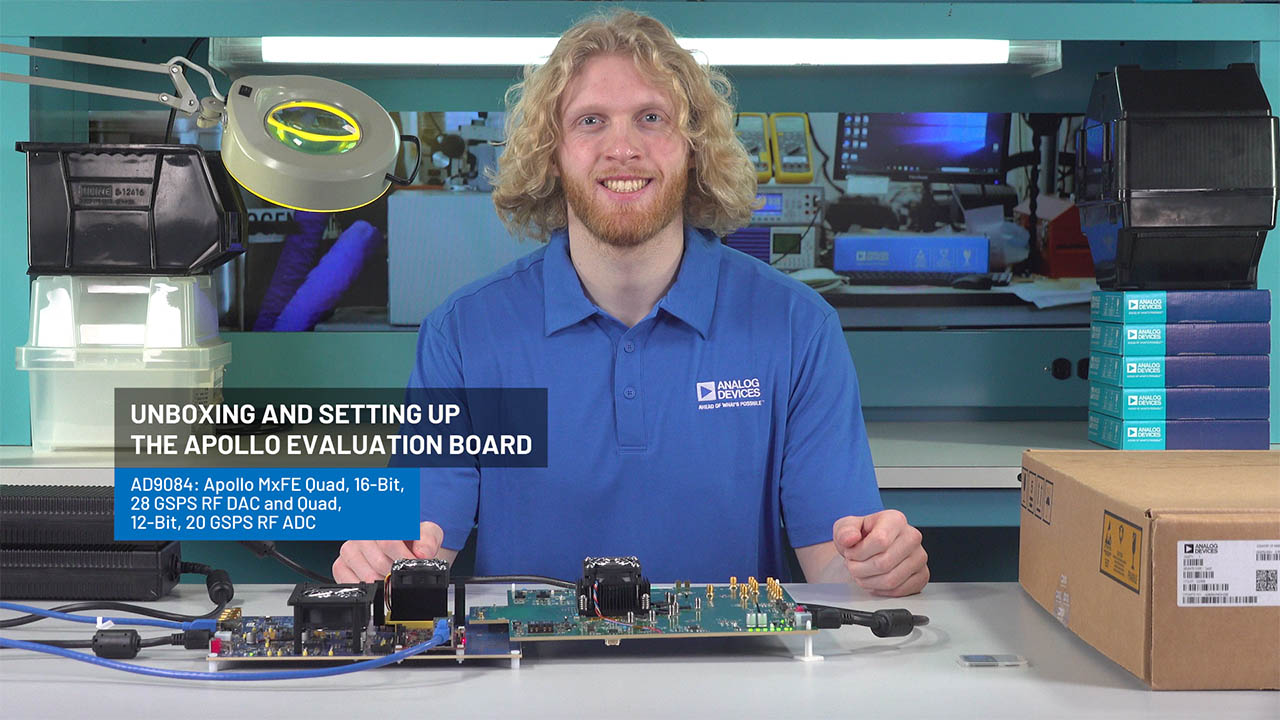

AD9084

推荐用于新设计

Apollo MxFE 四路 16 位 28GSPS 射频 DAC 和四路 12 位 20 GSPS 射频 ADC

AD9986

推荐用于新设计

4T2R直接RF发射器和观测接收机

AD9988

推荐用于新设计

4T4R 直接射频接收器和变送器

AD9081

推荐用于新设计

MxFE™ 四通道 16 位 12GSPS RFDAC 和四通道 12 位 4GSPS RFADC

AD9082

推荐用于新设计

MxFE™ 四通道 16 位 12GSPS RFDAC 和双通道 12 位 6GSPS RFADC

AD9963

推荐用于新设计

10/12位、低功耗、宽带MxFE

AD9961

推荐用于新设计

10/12位、低功耗、宽带MxFE

{{modalTitle}}

{{modalDescription}}

{{dropdownTitle}}

- {{defaultSelectedText}} {{#each projectNames}}

- {{name}} {{/each}} {{#if newProjectText}}

-

{{newProjectText}}

{{/if}}

{{newProjectTitle}}

{{projectNameErrorText}}