RF Signal and Vector Network Analyzers

Radio Frequency (RF) Signal and Vector Network Analyzer Solutions

Signal spectrum analyzers and vector network analyzers are critical test equipment found in the laboratory of electrical engineers for RF and high-speed measurements. As new wireless standards like 6G, Wi-Fi 7 and 8, and UWB emerge, the measurement and performance demands continue to increase, such as higher frequency ranges, wider bandwidths, and higher dynamic range. Analog Devices offers a broad and differentiated portfolio ranging from RF components and high-speed converters to integrated transceivers and power trees for spectrum/signal analyzers and network analyzers that optimize performance and cost.

Value and Benefits

We offer a broad RF and high-speed portfolio ranging from phase-locked loops (PLL) and VCO for LO signal generation to RF component solutions like amplifiers, gain blocks, mixers, filters, switches, and attenuators for signal path conditioning. We also offer state-of-the-art high-speed ADCs and integrated transceivers. These solutions address varying customer requirements from high-performance benchtop equipment to modular, low-cost handhelds

In addition, our best-in-class field and applications support can collaborate with customers on their complete signal chain.

Optimizes performance without compromising cost

Features best-in-class field and applications support

Allows for wider bandwidth, higher frequency, and dynamic range

Featured Products

AD9084

Apollo MxFE Quad, 16-Bit, 28GSPS RF DAC and Quad, 12-Bit, 20 GSPS RF ADC

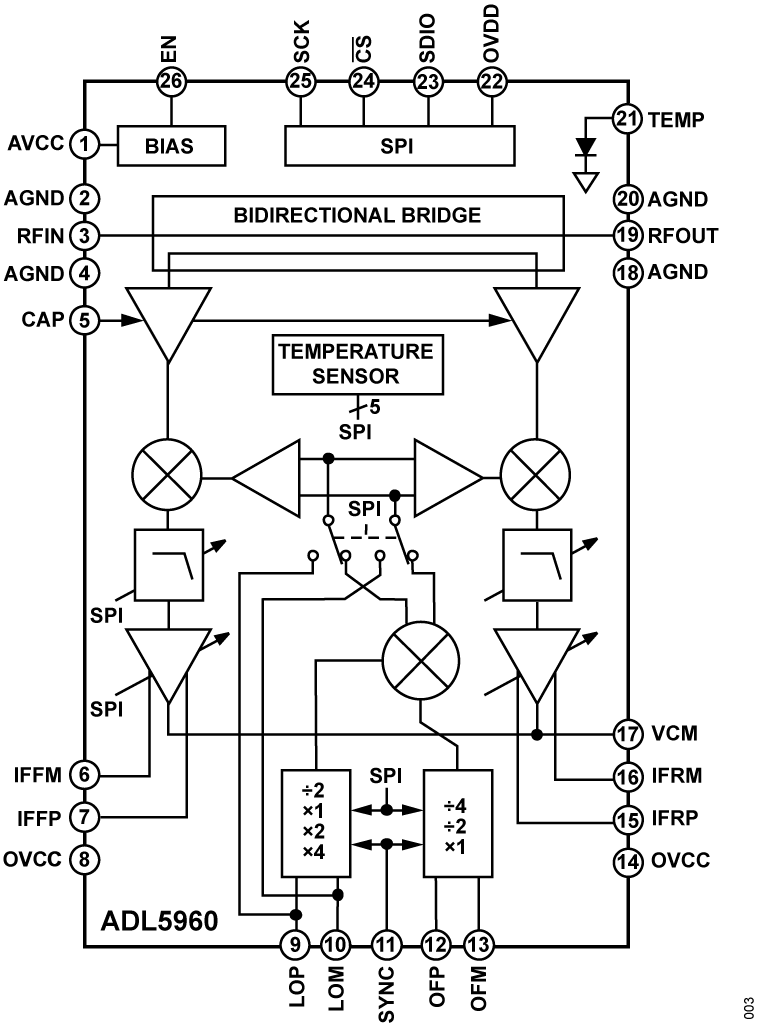

ADL5960

10 MHz to 20 GHz Integrated Vector Network Analyzer Front End

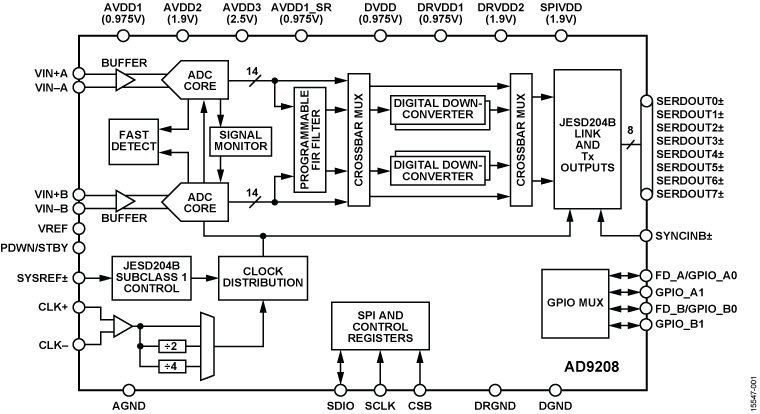

AD9208

14-Bit, 3GSPS, JESD204B, Dual Analog-to-Digital Converter

AD9689

14-Bit, 2.0 GSPS/2.6 GSPS, JESD204B, Dual Analog-to-Digital Converter

AD9691

14-Bit, 1.25 GSPS JESD204B, Dual Analog-to-Digital Converter

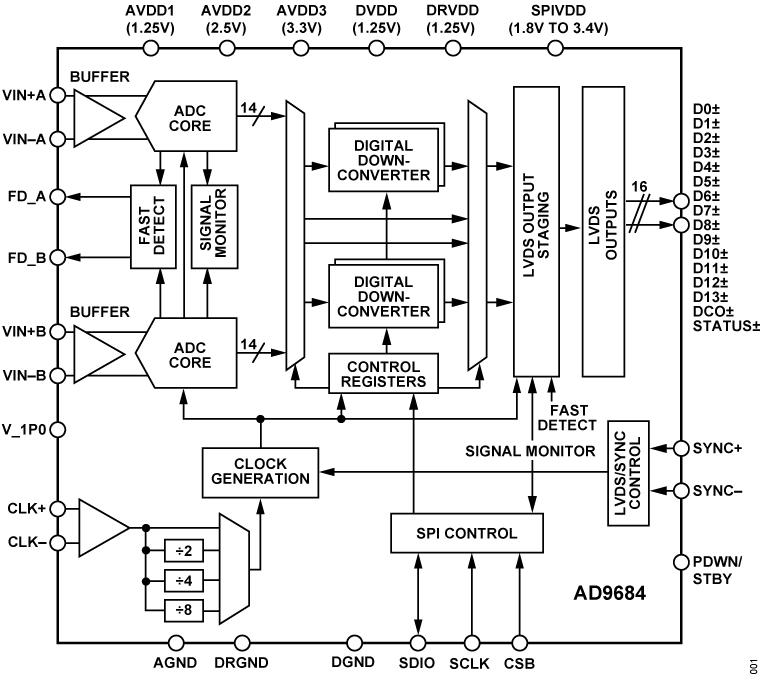

AD9684

14-Bit, 500 MSPS LVDS, Dual Analog-to-Digital Converter

AD9680

14-Bit, 1.25 GSPS/1 GSPS/820 MSPS/500 MSPS JESD204B, Dual Analog-to-Digital Converter

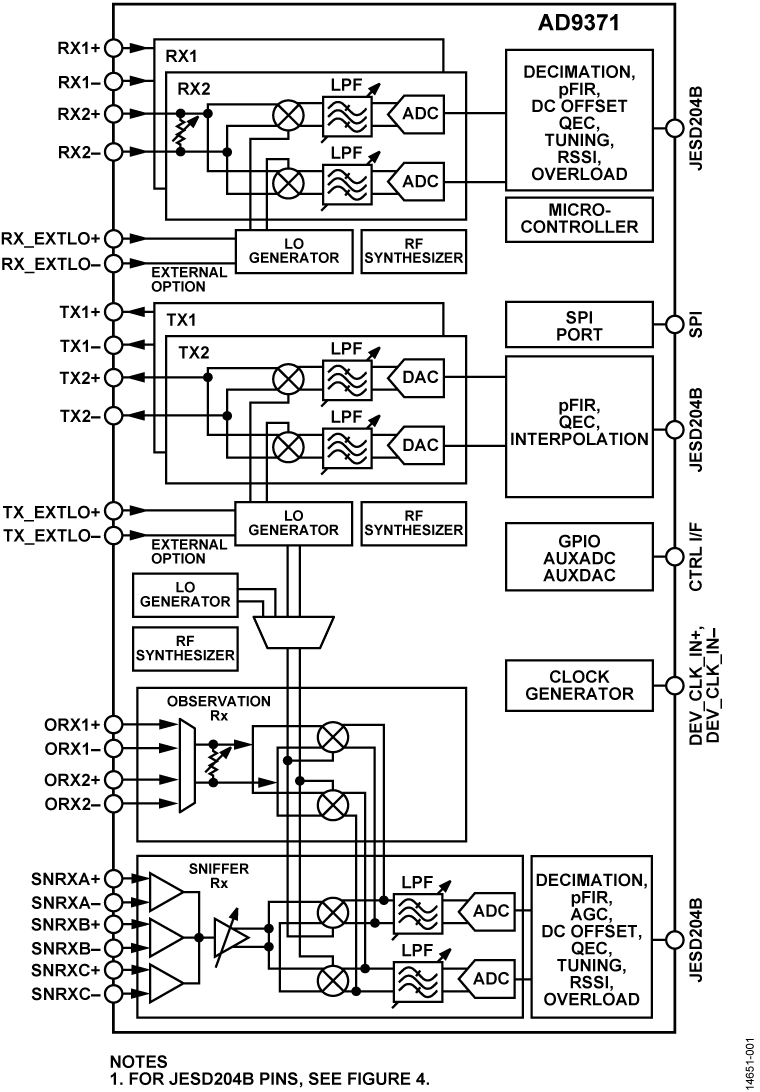

AD9371

Integrated, Dual RF Transceiver with Observation Path

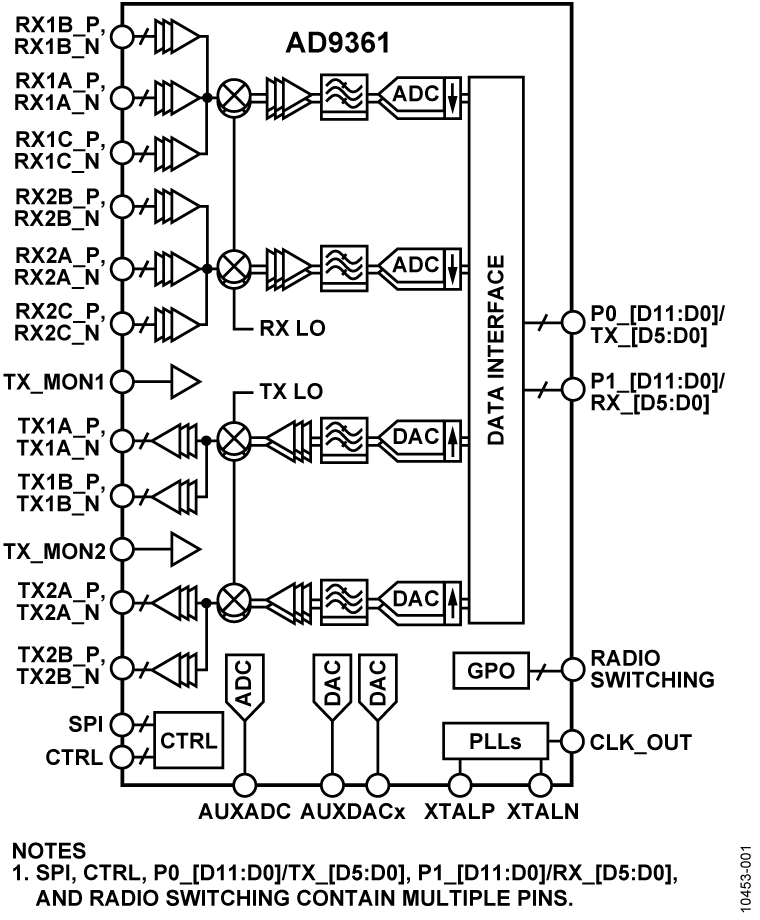

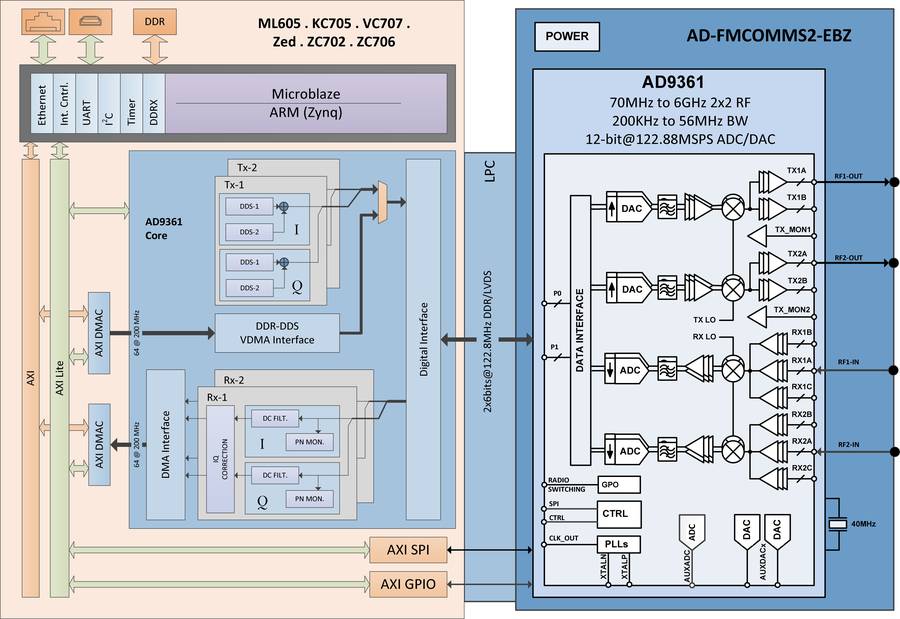

AD9361

RF Agile Transceiver

ADF4377

Microwave Wideband Synthesizer with Integrated VCO

HMC8192

20 GHz to 42 GHz, Wideband I/Q Mixer

HMC8191

6 GHz to 26.5 GHz, Wideband I/Q Mixer

< Prev

Next >

Click on a section in the diagram below to view available parts.

Interactive Signal Chains

Click on the part for more details

Reference Designs

CN0374

RF-to-Bits Solution Offers Precise Phase and Magnitude Data to 6 GHz

CN0232

Minimizing Spurious Outputs Using a Synthesizer with an Integrated VCO and an External PLL Circuit

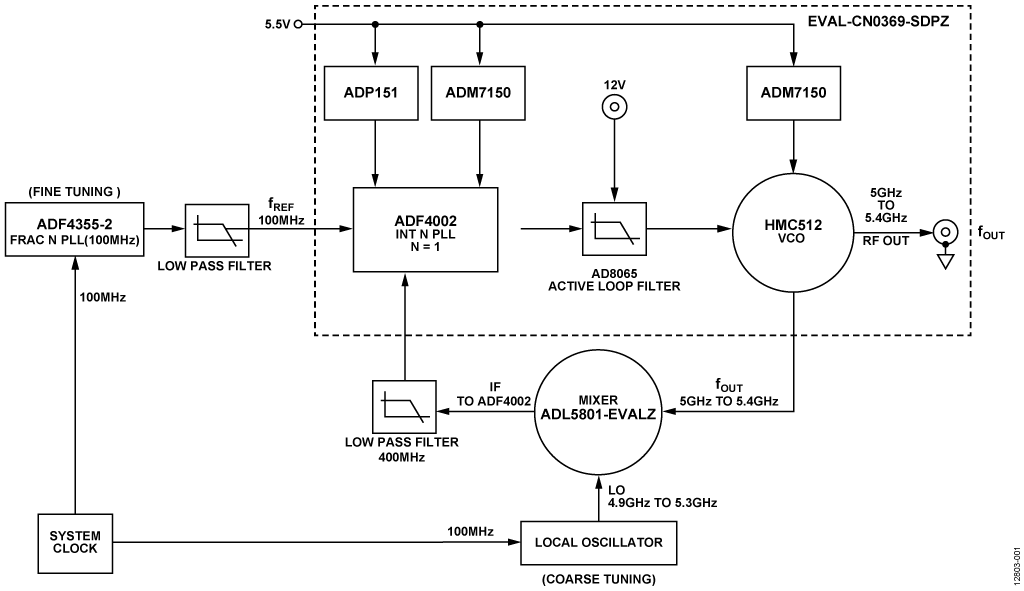

CN0369

Translation Phase Locked Loop Synthesizer with Low Phase Noise

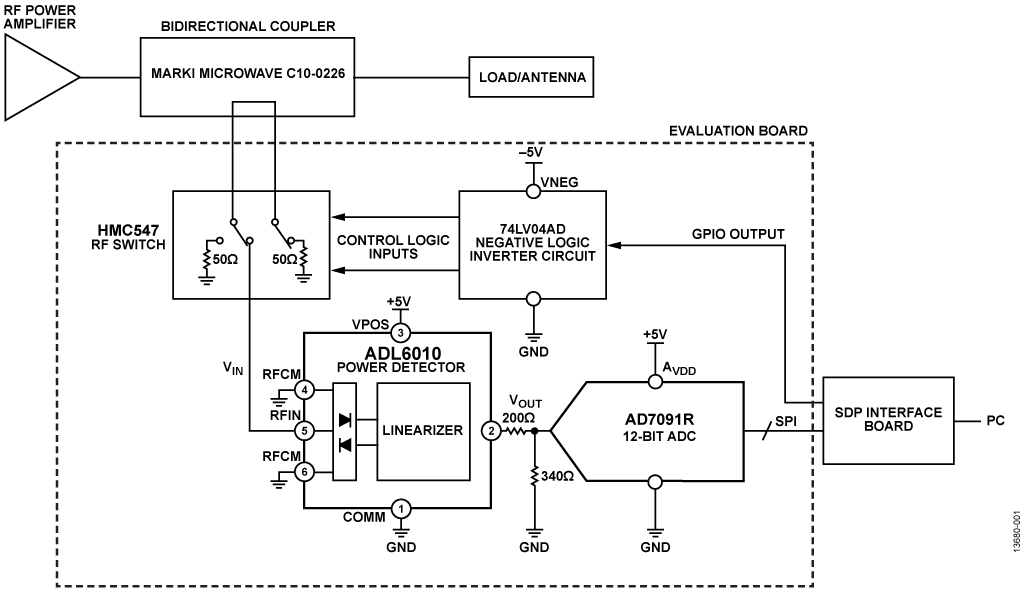

CN0387

Calibration-Free Return Loss Measurement System

CN0174

Low Noise, 12 GHz, Microwave Fractional-N Phase-Locked Loop (PLL) Using an Active Loop Filter and RF Prescaler

Evaluation Boards

AD9689 - 2600EBZ

AD9689 Evaluation Board

EVAL-AD9695

AD9695 Evaluation Board

EVAL-AD9208

Single AD9208 and Dual AD9208 Evaluation Boards

AD-FMCOMMS2-EBZ

AD9361 Software Defined Radio Board (2.4GHz Optimized)

AD-FMCOMMS3-EBZ

AD9361 Wideband Software Defined Radio Board

AD-FMCOMMS4-EBZ

AD9364 Wideband Software Defined Radio Board

AD-FMCOMMS5-EBZ

Dual AD9361 Evaluation Board

AD-FMCOMMS6-EBZ

AD-FMCOMMS6-EBZ Evaluation Board

Key Resources

User Guides

Design Tools

ADIsimRF

Virtual Eval - BETA

ADIsimPLL

LTpowerCAD® and LTpowerPlanner®

ADIsimFrequency Planner Tool

VisualAnalog™

ADIsimCLK

Files and Downloads

Application Note

AN-501: Aperture Uncertainty and ADC System Performance

227.66 K

AN-756: Sampled Systems and the Effects of Clock Phase Noise and Jitter

291.7 K

Book & eBook

Understanding Silent Switcher Technology: High Efficiency, Low EMI eBook

7.75 M

Circuit Note

Selected Reference Designs: Test and Measurement Solutions

5.88 M

Design & Integration File

ZIP

CN0369 Design & Integration Files

1.54 M

Solutions Bulletin & Brochure

Silent Switcher Technology

1.74 M

Tutorial

Fundamentals of Phase Locked Loops (PLLs)

407 kB

MT-003: Understand SINAD, ENOB, SNR, THD, THD + N, and SFDR so You Don't Get Lost in the Noise Floor

92 kB

MT-075: Differential Drivers for High Speed ADCs Overview

183 kB

MT-230: Noise Considerations in High Speed Converter Signal Chains

255 kB

MT-094: Microstrip and Stripline Design

97 kB

{{modalTitle}}

{{modalDescription}}

{{dropdownTitle}}

- {{defaultSelectedText}} {{#each projectNames}}

- {{name}} {{/each}} {{#if newProjectText}}

-

{{newProjectText}}

{{/if}}

{{newProjectTitle}}

{{projectNameErrorText}}