ほぼ純粋なDDSサイン波トーン・ジェネレータ

はじめに

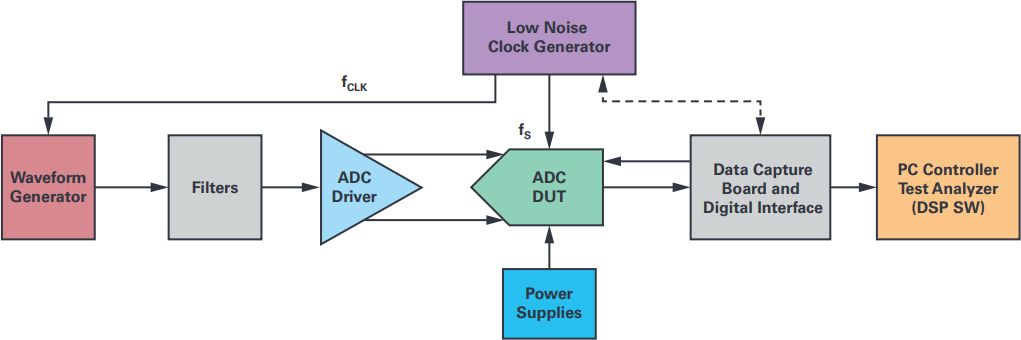

分解能が16ビットを超える高精度高速A/Dコンバータ(ADC)のAC性能のテストおよび検証には、少なくとも0kHz~20kHzのオーディオ帯域幅に対応できるほぼ完全なサイン波ジェネレータが必要です。通常、これらの検証や特性評価を実行するには、Audio PrecisionのAP27xxシリーズやAPx5xxシリーズのオーディオ・アナライザといった、高価な実験室用計測器が使用されます。大抵の場合、24ビット以上の最新の高速SARや広帯域シグマ・デルタ(Σ-Δ)ADCは、単電源入力および完全差動入力を特長としており、そのため、DUTに使用する信号源は、DCおよびAC共に正確でかつ、完全差動出力(180ºの位相差)を実現できることが必要となります。また、このACジェネレータのノイズおよび歪みのレベルは、これらのADCの仕様よりもはるかに優れていることが必要で、その結果、ノイズ・フロア・レベルは–140dBc未満、歪みは–120dBc未満となり、入力トーン周波数はほとんどのメーカー仕様によれば1kHzまたは2kHz~20kHzです。高分解能広帯域ADCに適した代表的なベンチ・テスト・セットアップの代表的な構成を図1に示します。最も重要な構成要素はサイン波ジェネレータ(シングル・トーンまたはマルチトーン)で、ここではソフトウェアベースのダイレクト・デジタル・シンセサイザ(DDS)が、極めて細かい周波数分解能による十分な柔軟性と、コヒーレントなサンプリングを実行するデータ・アクイジション・システムとのクロック同期を実現し、リークとFFTウィンドウ・フィルタリングを回避します。

図1. IEEE 1241規格に基づく代表的なADC(AC)テスト・セットアップの処理チェーン。DDFSは、完全な柔軟性やコヒーレントなサンプリング・アクイジションなど、多数の利点を活用して、測定システム全体を完全にデジタル化します。

高精度オーディオ・アナライザに比べてわずかなコストで、ダイレクト・デジタル周波数合成(DDFS)原理に基づく非常に高精度のサイン波ジェネレータを設計することは可能ですが、これは、ソフトウェアの形でSHARC®プロセッサなどの浮動小数点DSPプロセッサに実装されます。適度に高速な浮動小数点DSPは、実時間の期待に添い、また、全ての算術条件および処理条件を満たし、最先端のSAR ADCで設定されている歪みおよびノイズの性能レベルを実現します。32ビットまたは64ビットの固定小数点フォーマットでのSHARCコア・アーキテクチャのフルワードのデータ長を利用してNCOの位相累積を行い、独自の40ビット浮動小数点倍精度を利用してスペクトル形成に使用されるサイン波近似関数とデジタル・フィルタリングを実行することで、量子化の影響(丸め誤差および切り捨て誤差)は大幅に減少し、信号の再構成に用いるD/Aコンバータ(DAC)の不完全性と比較して無視できる程度になります。

ダイレクト・デジタル周波数合成

Joseph A. Webbによって1970年4月に申請されたデジタル・シグナル・ジェネレータ・シンセサイザの特許1は、単にいくつかのデジタル・ロジック・モジュールを使用するだけでサイン波を含む様々なタイプのアナログ波形を生成できる、DDS機構の基本とみなされるものが記述されています。その後、1971年初め、Tierneyら2が執筆し頻繁に引用される論文が発行されました。その論文には、直角位相生成が行えるようDDS動作を深耕することによる直接デジタル周波数生成とその限界(ワード切り捨ておよび周波数プランニング)がサンプリング・システム理論の観点で述べられています。実用化は、TTL 74xxファミリやECL 10Kファミリなどのディスクリートな標準的ロジックICに依存して行われるようになりました。その後10年足らずの間に、Stanford Telecom、Qualcomm、PlesseyそしてAD9950およびAD9955を開発したアナログ・デバイセズなどの企業によって、完全統合化ソリューションが市場に出回るようになりました。速度、消費電力、コストのトレードオフを最適化して設計されたこれらロジックICのアーキテクチャは、ルックアップ・テーブル(LUT)に基づき、位相、周波数、振幅の分解能が限定された形で位相とサイン波振幅の変換を行うものでした。現在、アナログ・デバイセズは、DDSスタンドアロン集積回路の最大のそして恐らくは最もユニークな製造元としてその地位を維持しており、現在の数値制御発振器(NCO)はAD9164やAD9174のようなRF DACに数多く集積される傾向にあります。複数のGHz帯域幅にわたって優れたノイズ性能と直線性を示すにもかかわらず、これらのデバイスのいずれも、LTC2378-20、AD4020、AD7768といった中程度の速度の高分解能ADCのテストには適していません。

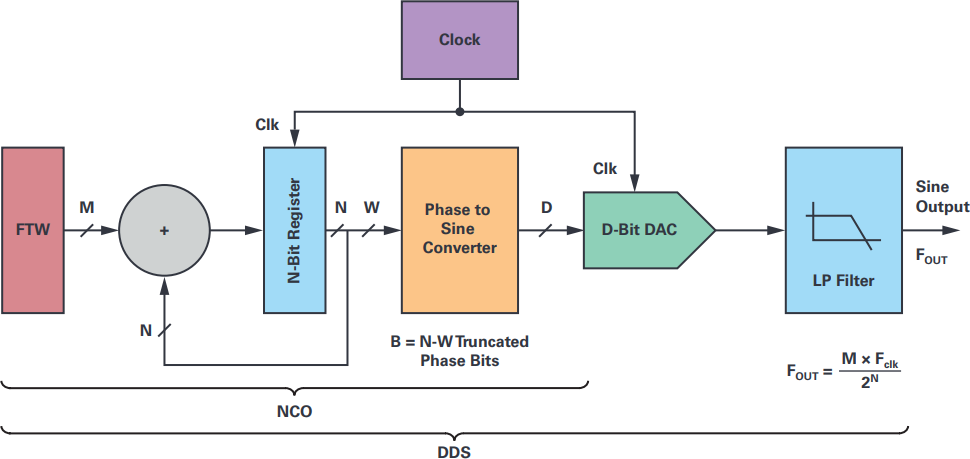

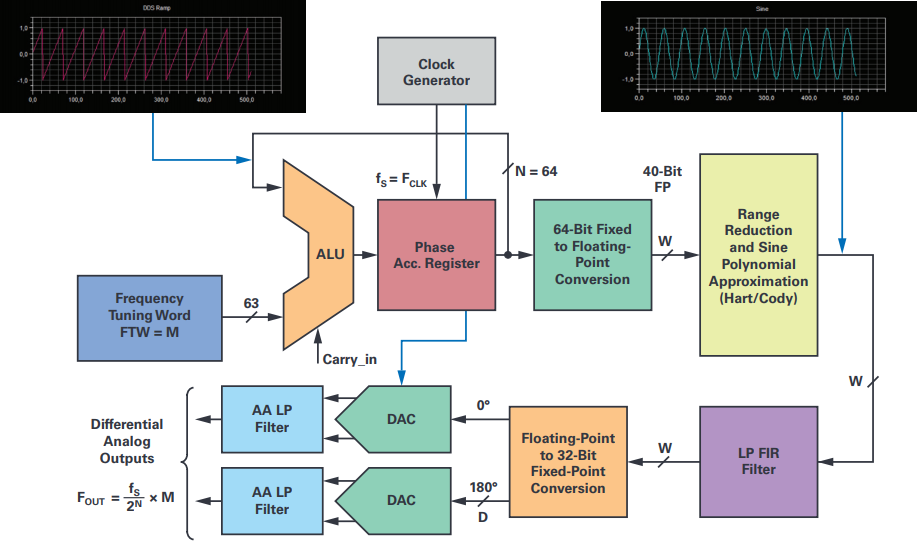

従来のPLLベースのシンセサイザに比べ、NCOやDDSは、非常に高精細の周波数分解能、高速応答性、完全に直交したサイン/コサイン波の生成のしやすさなどの特長を持つことで知られています。また、これらは広い帯域幅のカバレージとDC精度でも評価されています。その動作原理は、デジタル信号処理とサンプリング・システム理論に従っており、そのデジタル特性によって、出力信号の位相、周波数、振幅を完全にデジタル的に、また独立して、制御できます。図2のブロック図は、以下の3つの主要機能で構成される従来のDDSのアーキテクチャを示したものです。

- Nビットの位相アキュムレータ。

- Wビットの位相切り捨て入力ワードを特徴とする位相/サイン振幅コンバータ。

- DビットのDACおよび関連する再構成フィルタ。

図2. NCOの主要機能部およびフル機能ダイレクト・デジタル・シンセサイザとの差異。再構成DACおよび関連AAFが含まれます。NCOセクションはDACのテストや刺激に用いることができます。

位相アキュムレータは、レジスタと組み合わせた単純なNビット加算器を中心に構築されています。レジスタの内容は位相インクリメント(一般に周波数チューニング・ワード(FTW)とも呼ばれます)をΔθとしてサンプリング・クロックFCLKのレートで更新されます。アキュムレータは、周期的にオーバーフローする可能性があり、サンプリングまたはリファレンス・クロックFCLKとDDS出力周波数FOUTの間のフラクショナル分周器、あるいは分周比が以下の式で表されるギアボックスのように動作します。

オーバーフロー・レートは、以下のように、生成された波形の出力周波数を与えます。

ここで、0 ≤ FTW ≤ 2N–1。分周器の影響により、NCO出力でのリファレンスまたはサンプリングfSクロック位相ノイズは以下に示す分だけ減少します。

位相アキュムレータ・レジスタの出力は、生成された波形の現在の位相を示します。次に、アキュムレータのそれぞれの出力位相値は、位相/サインまたは位相/コサイン割り当てエンジンにより、サインまたはコサインのデータまたはサンプルの振幅に変換されます。この機能は、通常、LUT(ROM)に保存されている三角関数値を使用して実現されますが、場合によっては、サイン近似アルゴリズムを実行して、あるいはその両者を組み合わせて、実現されることもあります。位相/サイン振幅コンバータの出力はDACに供給され、DACが量子化されてサンプリングされた正弦曲線を生成してから、この曲線が信号を平滑化しスペクトルのエイリアシングを防止するためにフィルタ処理されます。この振幅の量子化は、DACの分解能が有限であることから、シンセサイザのノイズ・フロアとそれにより生じるS/N比(SNR)に理論的な限界をもたらします。更に、ミックスドシグナル・デバイスとして、DACは、それが持つINL、DNL、スルー・レート、グリッチ、セトリング時間特性により、DCおよびACの大きな非直線性を示します。これらの非直線性によりスプリアス・トーンが生じ、サイン波ジェネレータの全体のダイナミック・レンジが低下します。

図2のアーキテクチャに基づくサイン波ジェネレータの実際上の実装は、主として位相/振幅コンバータ・ブロックによって異なります。このブロックは、市場がデジタル無線アプリケーションを指向していることから、一般に、高い分解能よりもむしろ速度や消費電力について最適化されています。位相/サイン振幅コンバータを実現するための最も簡単な手法は、ROMを使用してサイン値を1対1のマッピングで保存することです。しかし、LUTの長さは位相アキュムレータの幅Nの指数関数(2N)として、また、波長テーブルのデータ・ワード精度Wに比例して増加します。ところが、アキュムレータの除去またはその出力の切り捨てを行うとそれに伴うトレードオフにより、周波数分解能の喪失とSFDRの著しい低下がもたらされます。位相や振幅の量子化によるスプリアスは–6dB/ビットの関係に従うことが示されています。通常、精細な周波数チューニングを行うためには大きなNが望ましいため、適度なスプリアス性能を維持しながらROMサイズを制限する手法がいくつか開発されています。一般に、サインまたはコサイン関数の4分の1波長の対称性を活用して位相の偏角範囲を4分の1にすることで、いくつかの簡単な圧縮方法が用いられています。範囲を更に狭めるためには、位相アキュムレータ出力を大幅に切り捨てることがデファクトの方法です。ただし、スプリアス高調波が発生します。それにもかかわらず、精細な周波数分解能条件、メモリ・サイズ、コスト上の制約などが理由で、この手法は常に採用されます。LUTベースの方法でメモリ条件を緩和するために、角度の様々な分解方法が提案されています。様々な種類の分割化、線形補間、あるいは多項式補間を用いて振幅圧縮を組み合わせるというこの考えの目的は、サイン関数の最初の4分の1周期、あるいは、サイン関数とコサイン関数の両方が必要とされるI/Q合成の場合には[0, π/4]の区間内を、正確に近似することです。同様に、ROM LUTを使用しない複素信号発生は、角度回転をベースとするアルゴリズムによって効率的にサポートされます。このアルゴリズムは、逐次比較のスキーム内でシフト動作と加算動作を呼び出すだけです。この方法は、広く用いられているCORDICに代表されるもので、ハードウェア乗算器が使用できない場合や、速度やコストを考慮して(FPGAやASICで)関数を実行するために必要なゲート数を減らす必要がある場合には、他の方法に比べて一般的に高速です。逆に、DSPマイクロプロセッサの場合など、ハードウェア乗算器を使用できるときは、補間法を併用したテーブルルックアップや、テイラー級数展開やチェビシェフ多項式などの完全多項式計算は、特に高精度が要求される場合に、CORDICよりも高速です。

ソフトウェアへの高精度NCOの実装

極めて名高いHewlett-Packardのアナライザやアプリケーション・ノートAN-1323に記載されているような、最高のアナログ発振器と同程度あるいはそれを上回る歪み性能を持つ高精度ACトーン・ジェネレータを構築することは、オーディオ周波数スペクトル(DC~20kHzの範囲)に特化したとしても容易なことではありません。しかしながら、先述のように、完全なソフトウェア実装を行い、組込みプロセッサの適切な演算精度を使用して位相計算(ωt)およびサイン関数(sin(ωt))近似を行えば、量子化に伴う各種副作用、ノイズ、およびそれに付随するスプリアスは確実に最小限に抑えることができます。つまり、図2のNCO機能ブロックは、何行かのコード(VHDLではありません)で変換され、実時間の制約を満足して最小のサンプリング・レートと目的の周波数帯域幅を可能にする、ソフトウェア・バージョンを実現します。

位相/サイン振幅変換エンジンに関しては、完全LUTスキームあるいはその何らかの変種は、サイン波に完全に準拠するために必要なメモリや補間動作が多すぎます。逆に、サイン近似を行う多項式法は、極めてロー・コストの汎用DSPを使用できるため、複雑さと精度に関して非常に良いトレードオフを提供できます。多項式による級数展開は、比較的単純であることと、所定の精度にアルゴリズムを調整する場合に、冪級数の種類の選択を極めて柔軟に行うことができることからも、非常に魅力的です。これは、大きなメモリ空間を必要とせず、100行未満のSHARC DSPアセンブリ行と、多項式の係数および変数を保存するためのRAM内のわずかな場所だけで済みます。サイン値はサンプリング時に計算されるだけだからです。

まず、サイン近似関数に対する明らかな選択肢は、テイラー/マクローリン冪級数を適切な次数で直接使用し、目標精度を満たすことです。ただし、冪級数はエンドポイントでの有効性を失いがちなので、多項式評価を実行する前に偏角の入力範囲を狭めることが必須です。偏角範囲を縮小しないと、[–π, +π]のような関数領域にわたって高い精度に対応できるのは非常に高次の多項式だけになってしまいます。従って、0 ≤ f < π/2として、sin(|x|) = sin(f + k × π/2)およびsin(f) = sin(x – k × π/2)というように、ある程度の変形を初等関数に施して、偏角を縮小する必要があります。そのため、減算による打消しが生じないよう、三角関数には特段の注意を払う必要があります。この打消しが生じると、特に計算精度が悪い場合、精度が著しく失われ重大な結果を招く可能性があります。ここで扱っている場合では、位相入力が大きいかπ/2の整数倍に近い場合にこれが発生する可能性があります。

周期性とモジュロ–2πの繰り返しの他、sin(x)関数の対称性を加えて、近似範囲を更に縮小できます。サイン関数が[0, 2π]の区間でx = πの点に関し反対称であるとすると、次式の関係を使用して、範囲を[0, π]に縮小できます。

同様に、sin(x)は、区間[0, π]でx = π/2で定義される線に関し対称であるため、[0, π/2]の範囲のxに対し、次式が成立します。

これにより、角度入力近似範囲が更に縮小されます。精度を向上しようと偏角を[0, π/4]など更に狭い区間に縮小することは効率的ではありません。sin(a+b) = sin(a) × cos(b) + cos(a) × sin(b)という一般的な三角関数の関係式で示されているように、サイン関数とコサイン関数の両方を同時に評価する必要があるためです。これは直交トーンを生成することに値します。

アナログ・デバイセズのADSP-21000 Family Application Handbook Volume 1には、(組込みシステムにとって)ほぼ理想的なサイン近似関数が記載されています。この関数は、基本的にはSHARCコアである、アナログ・デバイセズの最初のDSP浮動小数点プロセッサADSP-21020に最適化されて書き込まれた、冪級数に基づいています。sin(x)のこの実装は、ミニマックス多項式近似に依存しています。この近似は、丸め誤差を最小化して前述の打消しの発生を防止するための浮動小数点演算に関し、Hartら4によって発表され、CodyとWaite5によって改良されたものです。このミニマックス法は、チェビシェフの多項式とRemezの交換アルゴリズムに依存して目的の最大相対誤差の係数を定めます。図3にMATLAB®で示したように、セットの係数のわずかな相違は、7次のテイラー多項式に比べ、ミニマックスの精度の著しい向上をもたらしています6。最高精度と速度とのトレードオフのため、このサイン近似関数の角度入力範囲は[–π/2, +π/2]の区間に縮小され、ソフトウェア・ルーチンには効率的な範囲縮小フィルタ(「サイン」サブルーチンの合計実行時間の約30%に相当)が含まれています。

![図3 0を中心として定義されるテイラー・マクローリン法とは異なり、ミニマックス・サイン近似手法では、[–π/2, +π/2]の区間にわたって最大相対誤差が最小化かつ均等化されます。](https://www.analog.com/jp/_/media/analog/en/landing-pages/technical-articles/an-almost-pure-dds-sine-wave-tone-generator/figure3.png?la=en&rev=76777dfadc2d4f40b14e6a85e2db6378&sc_lang=ja)

図3 0を中心として定義されるテイラー・マクローリン法とは異なり、ミニマックス・サイン近似手法では、[–π/2, +π/2]の区間にわたって最大相対誤差が最小化かつ均等化されます。

全ての計算は32ビットの固定小数点演算で実行できますが、特に大きな数値を処理する場合に最も一般的で便利な数学計算方法は、長年にわたり、IEEE 754の浮動小数点規格でした。アナログ・デバイセズは、DSP VLSIチップ・メーカーとして、IEEE 754-1985規格の策定に当初から関わっていました。当時は、シングルチップの浮動小数点DSPプロセッサは全くなく、ADSP3212のような浮動小数点乗算器やADSP-3222のようなALU演算ICなどの簡単な素子があるだけでした。このフォーマットがコンピュータ業界の各種独自フォーマットのほとんどから置き換わり、単精度32ビット、拡張精度40ビット、そして最近では倍精度64ビットの形で、全てのSHARC DSPプロセッサのネイティブ・フォーマットとなって、ADSP-SC589やADSP-SC573が誕生しました。

32ビットの仮数部を持つSHARC 40ビット拡張単精度浮動小数点フォーマットは、このサイン波生成アプリケーションに十分な精度(u 2–32)を備えています。他の条件が同じ場合、CodyとWaiteは、[0, +π/2]の入力範囲で誤差が均等に分布している32ビットの全体精度には、15次の多項式が適していることを示しています。演算数と最小限に抑え、かつ、精度を維持するための最終微調整は、多項式計算にホーナー法を適用することです。これは、多項式をある一点で評価するための高速な累乗法の一種です。例えば、以下のとおりです。

R1~R7は多項式級数のCodyとWaiteの係数で、任意の入力偏角ε[0, π/2]に対しサイン関数を評価するのに必要なのは、8回の乗算と7回の加算だけです。アセンブリ・サブルーチンの形で書き込まれた完全なsin(x)の近似コードは、SHARCプロセッサの場合約22コア・サイクルで実行できます。元々のアセンブリ・サブルーチンは、40ビットの多項式浮動小数点係数を選択した場合に同時に2回のメモリ・アクセスができるよう変更されており、6サイクル分が節約できます。

NCOの64ビット位相アキュムレータ自体は、実行用に、倍精度の2の補数フラクショナル・フォーマットでSHARC 32ビットALUを使用しています。メモリ更新を行う完全な位相アキュムレータの実行には11のコア・サイクルが必要で、その結果、各NCO出力サンプルは、約33コア・サイクルで生成されます。

図4は、ソフトウェアDSPベースのNCOを、各段の算術フォーマットの精度に関するいくつかのリファレンスと共に、機能ブロックで表したものです。更に、1つまたは2つのDACおよびそれらのアナログ・アンチエイリアシング・フィルタ回路が、信号のアナログ再構成を行い完全なDDFSを実現するために必要です。この処理チェーンの重要な要素は次のとおりです。

- 64ビット位相アキュムレータ(SHARC ALU倍精度加算、オーバーフローあり)

- 64ビット・フラクショナル固定小数点/40ビットFP変換ブロック

- 範囲縮小ブロック[0, + π/2]および4分の1周期選択(CodyおよびWaite)

- 位相/振幅変換のためのサイン近似アルゴリズム(Hart)

- sin(x)再構成および–1.0~+1.0の範囲での正規化段

- LP FIRフィルタおよびsin(x)/x補償(必要な場合)

- 40ビットFP/Dビット固定小数点変換およびDACのデジタル入力に一致するスケーリング機能

図4. ソフトウェアDDSの簡略化したブロック図は、データの算術フォーマットと処理要素間の様々な量子化段の場所を示します。

デジタル・ローパス・フィルタをNCOの出力にオプションで配置し、目的の帯域に重なるスプリアスやノイズを除去することもできます。このフィルタは、アナログ再構成のために選択したDACに応じて、補間や反転sin(x)/x周波数応答補償も実行できます。そのようなローパスFIRフィルタは、MATLABフィルター ・デザイナー・ツールを使用して設計できます。例えば、サンプリング周波数が48kSPS、帯域幅がDC~20kHz、帯域内リップルが0.0001dB、帯域外減衰が–150dBとすると、40ビットの浮動小数点係数を使用して高品質の等リップル・フィルタを実装できます。単一命令、単一データ(SISD)、単一計算ユニット・モードにおいて、使用するフィルタ係数はわずか99個で、合計実行時間は約120 SHARCコア・サイクルです。デジタル・フィルタリングの後、計算されたサンプルのペアは、DSP早期シリアル・ポートの1つを使用してDMAによってDACに送られます。速度性能を向上するために、ブロック操作による処理をサポートする大きなピンポン・メモリ・バッファを使用して、DMA動作を連ねることも可能です。例えばブロックのデータ・サイズをFIRデータ遅延ラインの長さと等しくなるようにできます。

SFDR最大化に向けたNCOでの最終調整

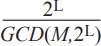

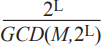

前述のとおり、NCOは、位相アキュムレータの出力が切り捨てられることが主な要因となって、スプリアスの影響を受けます。また、程度は小さくなりますが、計算またはテーブルから得られたサイン関数値について行われる振幅量子化の影響も受けます。位相切り捨てによる誤差は、位相変調(鋸波)によってキャリア周波数を中心とするスプリアスを発生し、一方、サイン振幅の量子化は高調波関連のスプリアスを発生します。ただし、これらは長い間、ランダム誤差およびノイズと考えられていました。現在では、位相アキュムレータの動作は数学的に完全に、Henry T. NicholasとH. Samueliの技術論文7に記載されているように理解されています。徹底的な解析の後1つのモデルが提示され、位相アキュムレータはディスクリートな位相サンプル順列生成器とみなされ、そこから周波数スプリアスが予測されています。位相アキュムレータのパラメータ(M、N、W)がどのようなものであれ、位相シーケンスの長さは次のようになります。

(ここで、GCDは最大公約数)この長さは、図5に示すように、周波数チューニング・ワードMの最も右のビット位置Lで決まります。そのため、Lの値によってシーケンス・クラスが定義され、それぞれが位相コンポーネントの固有セットを分担しますが、

の比に従って並べ替えられます。時間領域で生成される、切り捨てられた位相サンプルのこうしたシーケンスは、DFTによって、周波数領域における各スプリアス・ラインのそれぞれの場所と振幅を定めるために使用されます。また、これらのシーケンスは、M(FTW)の奇数の値が最小周波数のスプリアスの振幅を示すことを実証するものであり、また、単に1LSBをFTWに追加することで、位相アキュムレータの簡単な変更によってこれらの最小条件を満たすことができることを示唆しています。このように、位相アキュムレータの出力シーケンスは、Mの値と位相アキュムレータの初期内容とは無関係に、常に同じ2N個の位相要素を持つようにされています。最も厳しい条件のトーン振幅のレベルは、3.922dBだけ減少し、SFDR_min (dBc) = 6.02 × Wに等しくなります。Nicholasの変更した位相アキュムレータはいくつかの利点をNCOにもたらします。まず、FTWの最も右側のビットがMSBに近すぎるという状況をなくします(FMCWアプリケーションでの周波数掃引)。次に、スプリアスの振幅を周波数チューニング・ワードMとは無関係にします。この変更は、サンプリング・レートfSでALU LSBをトグルすることでソフトウェアで容易に実行でき、FTW LSBがロジック1に設定されている場合と同じ位相アキュムレータの動作がシミュレーションできます。位相アキュムレータのサイズNが64ビットの場合、½ LSBのオフセットは目的の周波数FOUTの精度に関して無視できる誤差とみなせます。

図5. FTWのゼロでない最も右側ビットの位置によって、理論上の最も厳しい条件でのSFDRレベルが設定されます。Nicholasの変更した位相アキュムレータは、任意のNの値でこの問題を解決し、NCOのSFDRを最大化します。

出力位相ワードWが32ビットの場合、位相切り捨てによる最大スプリアス振幅は、–192dBcという値に制限されます。サインのサンプル値の限定された量子化は、周波数スプリアスの別のセットの原因にもなり、また一般的にノイズとみなされて、SNRq(dB) = 6.02 × D + 1.76というよく知られた関係式で見積もられます。これは、位相/サイン振幅変換アルゴリズム段の近似誤差による寄生要素に加える必要があります。ただし、これは、位相/サイン近似アルゴリズムとその計算精度を非常に注意深く選択すれば、無視できると考えられています。

こうした結果は、用いているソフトウェアのサイン関数NCOの直線性とノイズはどちらも、市販されているほとんどの高精度ADCをテストするために必要な閾値をはるかに上回る理論的なレベルにあることを示しています。最後に、しかし最も重要なシグナル・チェーン要素を見出すことが残っています。その要素とは、再構成DACとその相補アナログ・アンチエイリアシング・フィルタおよび予定する性能レベルを満たすことが可能な関連ドライバ回路です。

再構成DAC:最大の弱点

優れた20ビット精度のDACであるAD5791のような、非直線性誤差(INLおよびDNL)に関して最高の仕様を備えた高精度DACを選択することが、最初の衝動でしょう。しかし、その分解能は、わずか20ビットで、そのR-2Rのアーキテクチャは信号再構成、特に非常に純粋なサイン波の生成には対応していません。入力コード遷移の間に大きなグリッチがあるためです。従来のDACアーキテクチャは、バイナリ重み付け電流ジェネレータまたは抵抗ネットワークを中心として構築されており、外部または内部のタイミング・スキューやその他のデジタル入力ビットのスイッチング非対称などの、デジタル・フィードスルーやデジタル・スイッチングの悪化の影響を受けがちです。これは特に、エネルギーの変化が生じるような大きな遷移の間に当てはまります。これにより、コード依存の遷移が生じ、大振幅の高調波スプリアスの原因となります。

20ビットを超える分解能の場合、DAC出力をデグリッチするために外部に超直線性の高速サンプル&ホールド・アンプを使用しても、大した効果は望めません。それ自体がLSBの何十倍ものトランジェントを生じ、また、サンプリングによる群遅延非直線性を招くためです。主として通信アプリケーションにおける信号再構成に対しては、グリッチ問題は、MSB用の完全にデコードされたセクションとLSB用のバイナリ重み付け要素を混合する、分割アーキテクチャを使用して解決されます。しかし、16ビットの精度を超えるそのような市販のDACは、現在のところ存在しません。NCOの動作は完全に予測できる代わりに、DACの誤差は、オーディオ・アプリケーション専用のDACまたはADCを除き、特にメーカーの動的仕様が詳細でなかったり存在しなかったりする場合は、正確な推定やシミュレーションが困難です。したがって、インターポレーション・フィルタを備えたオーバーサンプリング・マルチビット・シグマ・デルタDACが、この作業に十分応えられる唯一のソリューションのように思われます。最大32ビットの分解能、超低歪み、高SNRを備えたこれらの最新コンバータは、低~中帯域幅での信号再構成に最適なデバイスです。オーディオ・スペクトルやそれより若干広い帯域(20kHzまたは40kHzの帯域幅)での最高のノイズ性能および歪み性能を実現するための、アナログ・デバイスのポートフォリオ中最高のシグマ・デルタDACは、AD1955オーディオ・ステレオDACです。これは分解能が24ビットに制限されているにも関わらず市販のオーディオDACでは最高クラスの地位を保っています。

2004年に販売開始されたこのオーディオDACは、マルチビット・シグマ・デルタ・モジュレータとオーバーサンプリング手法に基づくもので、また、歪みやその他のこの変換原理固有の問題を緩和する様々な手法を補助として用いています8。

AD1955には、現在でもこの種のフィルタとしては最高レベルを維持している、インターポレーションLP FIRフィルタが採用されています。このフィルタは、極めて高いストップバンド減衰性能(約–120dB)と非常に低いインバンド・リップル(約±0.0001dB)を実現しています。内蔵された2個(左チャンネルおよび右チャンネル)のDACは、最大200kSPSで動作できますが、最高のAC性能は、48kSPSおよび96kSPSで発揮されます(ステレオ・モードでのダイナミック・レンジおよびSNRのどちらについても、120dB(代表的なEIAJ規格のA特性で重み付け))。モノラル・モードでは、2つのチャンネルが異なる位相で同時に組み合わさり、3dBの性能向上が見込まれます。ただし、広帯域アプリケーションでは、これらの仕様の実現性はある程度低下します。仕様は合成されたものであり、また、20Hz~20kHzの帯域幅に限定されているためです。帯域外のノイズとスプリアスは、EIAJ規格のA特性重み付けフィルタおよびオーディオ業界の仕様定義が理由の一部となって、20kHzは超えないとみなされています。オーディオ測定に特化されたこのバンドパス・フィルタは、人間の耳の周波数応答を模したもので、フィルタ処理を行わない測定に比べ、3dBだけ良好な結果をもたらします。

DDFSハードウェアのデモンストレーション・プラットフォーム:AD1955を使用したサイン波再構成

DSPプロセッサをサポートするボードとAD1955 DACを使用してアナログ信号再構成を行うボードの2つの評価用ボードを使用して、完全なDDFSを実行しました。入手のしやすさと、使いやすく任意のオーディオ・アプリケーションに適した構成となっていることから、第二世代SHARCのADSP-21161N評価用ボードを選択しました。現在も製造されていますが、ADSP-21161Nはしばらく前に設計されたもので、工業用、ハイエンドのコンスーマ向け、プロフェッショナル向けのオーディオ・アプリケーションに対応可能で、最大で110Mipsおよび660MFlopsまたは220MMACS/sの能力を持っています。最新世代のSHARCプロセッサに比べると、命令パイプラインが短く3段であること、オンチップRAMが1Mbでわずか3ポートであること、周辺機器セットが少ないことなどがADSP-21161Nの大きく異なる点です。高精度トーン・ジェネレータの最後の、そして最も重要な段はAD1955評価用ボードをベースとしています。このボードは、ソフトウェアNCOから送られたサンプルからアナログ信号を忠実に再構成しなくてはなりません。この評価用ボードは、ナイキスト基準を満たすようオーディオ帯域幅に最適化されたアンチエイリアシング・フィルタ(AAF)が実装されており、また、通常のS/PDIFまたはAES-EBUレシーバーの他、PCM/I2SおよびDSDのデジタル・ストリームに対応する一組のシリアル・オーディオ・インターフェースを備えています。PCM/I2Sシリアル・リンク・コネクタは、AD1955 DACボードをADSP-21161N EVBのシリアル・ポート1および3のコネクタ(J)に接続するために使用されます。どちらのボードも、サンプリング・レートが48kSPS、96kSPS、または192kSPSで、I2S PCMまたはDSPの動作モード向けに構成されています。DSPのシリアル・ポート1は、左および右のチャンネル・データ、ワード・セレクトまたはL/Rフレーム同期、および、デュアルチャンネルDACのデジタル入力インターフェースに必要なSCKビット・クロック信号を生成します。シリアル・ポート3は、DACのインターポレーション・フィルタの動作と、入力サンプリング周波数(48kSPS)より256倍(デフォルト)高速で実行するシグマ・デルタ・モジュレータの動作に必要な、DACのマスタ・クロック(MCLK)を生成するために使用されます。全てのDACクロック信号はDSPにより生成されるため、予めボードに備わっていたロー・コストのEpson製クロック発振器は、Crystek製超低ノイズ発振器CCHD-957に変更されています。その位相ノイズ仕様は、24.576MHzの出力周波数に対し、1kHzのオフセットで–148dB/Hzという低い値となっています。

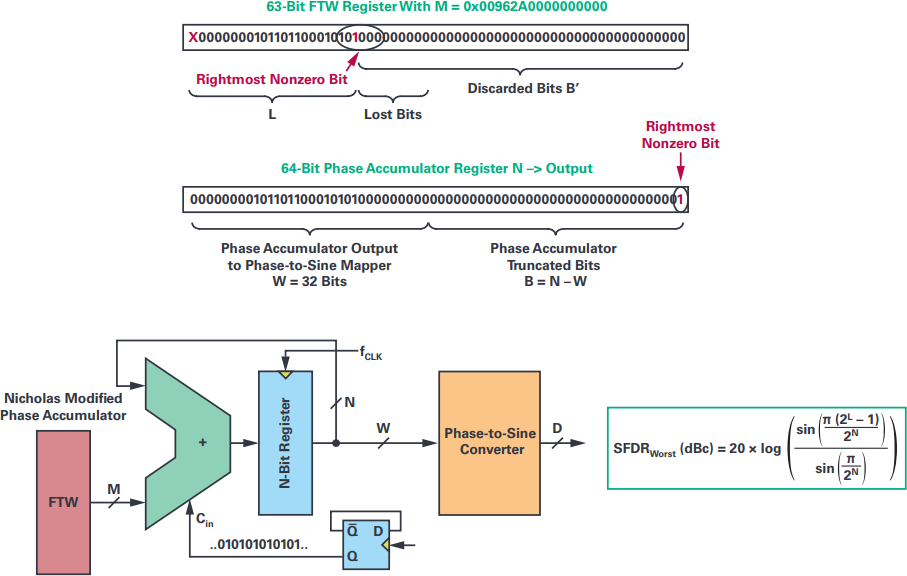

アナログ出力側では、アクティブなI/Vコンバータを使用してAD1955の電流差動出力を一定のコモンモード電圧(代表値2.8V)に維持し、歪みを最小限に抑えます。この目的のため、および、アナログ信号再構成を処理するために、AD797のような超低歪みおよび超低ノイズの高精度オペアンプを使用します。2つの差動出力はDSPによって個別に処理されるので、モノラル・モードではなく、AAFトポロジでのステレオ出力構成を選択しました。このAAFは、LTspice® XVIIでシミュレーションを行っており、その結果を図6に示します。フィルタの最終セクションはパッシブなので、新製品のADA4945のようなアクティブな差動バッファ段を追加する必要があります。この低ノイズ、超低歪み、高速セトリング時間の完全差動アンプは、高分解能SARおよびシグマ・デルタADCを駆動するためにDACに併用するデバイスとしてほぼ完璧な性能を持っています。比較的大きなコモンモード出力電圧範囲と優れたDC特性を備えるADA4945は、比類のない出力バランスを提供し、偶数次の高調波歪み積の抑制に寄与します。

図6 AD1955 EVBの3次アンチエイリアシング・フィルタの周波数応答をLTspiceでシミュレーションした結果(ステレオ構成)

EVBの3次フィルタの–3dBカットオフ周波数は76kHzですが、減衰量は、500kHzでわずか–31dBです。インバンドの平坦性は非常に優れていますが、このLPフィルタの帯域外の減衰量は、純粋な再構成オーディオ・アプリケーションに限定される場合でも、大幅に改善する必要があります。これは、DACで形成されたノイズやモジュレータのクロック周波数MCLKを除去するためには必須です。ソフトウェアDDSをシングル・トーン・ジェネレータに使用するか、任意波形ジェネレータ(複素波形のAWG)に使用するかによって、AAFは帯域外の減衰または群遅延歪みに対して最適化されます。実際の比較例をあげると、古いながらも定評のあるSRS製超低歪みファンクション・ジェネレータ、DS360は、同じサンプリング・レートに対し7次のCauer AAFで設計されています。信号再構成は、デジタル・オーディオ・アプリケーションを目的としたシリアル入力20ビット・セグメント化R-2R DACである、AD1862に依存しています。AD1862は、20ビット・ワードのサンプリング・レートを最大768kHz(×16 fS)に維持し、極めて優れたノイズ仕様と直線性仕様を備えています。そのシングルエンド電流出力レベルは、外部のI/V変換段に対する最適なアンプを使用するための選択の余地を残しています。

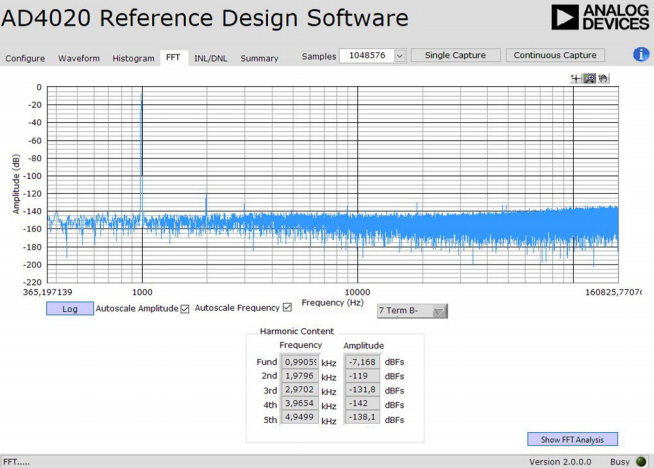

AD1955とSHARC DSPの組み合わせは、AD4020などのいくつかの高分解能SAR ADCに対し、間に外付けするパッシブ・フィルタを選択せずにテストを行いました。デフォルトでは、基本的なAD4020評価用ボードは、オンボードのADA4807ドライバ以外には選択できません。ADC入力に、V_REF/2のコモンモード電圧でバイアスする単純な回路によって、300Ωの比較的低い入力インピーダンスが生じるため、シグナル・アイソレーション、ACカップリング、またはEVAL-ADA4945-1のような外部差動アンプ・モジュールの使用が必要となります。回路ノートCN-0513で説明されているAD4020リファレンス設計ボードの方が、良い選択肢となります。これには、ディスクリートのプログラマブル・ゲイン計装アンプ(PGIA)が内蔵されており、高い入力インピーダンスを備えると共に、±5Vの差動入力信号(G = 1)を受け入れることができます。これらのAD4020ボードとそのSDP-H1コントローラには、コヒーレントなサンプリング・アクイジションに対応できる機能がありませんが、サンプルに対し最大1Mという適切な波形キャプチャ長が可能です。したがって、選択的なウィンドウ処理を行った長いFFTが可能で、高精度な周波数分解能と低ノイズ・フロアを両立できます。例えば、7項ブラックマン・ハリス・ウィンドウの場合、図7に示す1MポイントのFFTプロットは、990.059Hzで生成されたサイン波に対するAD1955の歪みのレベルを示しています。第2高調波が最大の歪み成分で、350kHzの帯域幅で–111.8dBcの最大スプリアスとなっています。ただし、806kHzという全ADCナイキスト帯域幅を考慮すると、SFDRは、DACシグマ・デルタ・モジュレータとインターポレーション・フィルタ周波数およびその第2高調波(384kHzおよび768kHz)に限定されます。

図7 1MポイントのFFT解析は、第2高調波が–111dBc未満という非常に優れた歪み特性を示しています。この場合、最大スプリアスは1kHzの入力周波数に対し10kH~200kHzの帯域で発生しています。ノイズ・フロアは約–146dBFSとなっています。

同じ条件で、スペクトル特性がわずかに異なる、旧式のAD1862についてテストを行いました。約500kSPSでクロックされる2個の20ビットDACを差動構成に配置したところ、1.130566kHz、12Vp-pのサイン出力レベルで、ノイズ・フロアは–151dBFS、THDは–104.5dBで し た。AD4020の ナ イ キ ス ト 帯 域 幅(806kHz)を超える範囲のSFDRは約106dBで、これは第3高調波によって制限されています。2個のAD743低ノイズFETアンプをベースとするDAC再構成フィルタは、AD1955評価用ボードのものと同様に、3次フィルタですが、–3dBのカットオフ周波数は35kHzです。

効力を生じるためには、DDSベースのジェネレータに、生成したDC~25kHzのCW信号周波数範囲に対し、約250kHzで100dBを超える減衰量を持つ適切なフィルタ機能が必要です。これは、6次のチェビシェフLPフィルタを用いて実現でき、更に6次のバターワースLPフィルタを使用すれば完全なインバンドの平坦性が実現できます。フィルタの次数を減らすと、アナログ段の数と、ノイズや歪みのような非理想的なパラメータに制限が生じます。

まとめ

標準的な評価用ボードについて行った予備的で簡単なテストにより、サイン波CW生成を最高性能で実現するプロセッサ・ベースのDDS手法が、手の届く範囲にあることが示されました。–120dBcという高調歪みの数値は、再構成フィルタとアナログ出力バッファ段を注意深く設計することで達成できます。DSPベースのNCO/DDSは、シングル・トーンのサイン波の生成に限定されるわけではありません。適切なカットオフ周波数を持つ最適化されたAAF(ベッセルまたはバターワース)を使用すれば、それ以外のハードウェアを変更することなく、同じDSPとDACの組み合わせを任意のタイプの波形を生成する高性能AWGに模すことができます。例えば、完全にパラメータ化可能なマルチトーン・サイン波を、IMDテスト用に各コンポーネントの位相と振幅を完全に制御した形で合成できます。

浮動小数点演算は、高精度や高ダイナミック・レンジが求められるアプリケーションには重要なものなので、現在では、低コストのADSP-21571やSoCのADSP-SC571(ARM®およびSHARC)などのSHARC + DSPプロセッサが、総サンプリング・レートが10MSPSにも達する実時間処理を実行する際の、デファクト・スタンダードとなっています。500MHzでクロックされるデュアルSHARCコアとそのハードウェア・アクセラレータは、5Gflopを超える計算性能を実現し、また、任意の波形生成や複素解析処理のタスクで必要となる基本的な構成要素である、多数の専用内蔵SRAMを提供できます。この種のアプリケーションは、ハードウェアのプログラマブルなソリューションをシステマティックに利用することが高精度デジタル信号処理を行う上で必須ではないことを示しています。浮動小数点プロセッサとその完備された開発環境によって、MATLABなどのシミュレータからコードを簡単に手早く移動することができ、更に、アナログ・デバイセズのCCESおよびVDSP++ CやC++のコンパイラと、シミュレータおよびリアルタイム・デバッガのフル・スイートにより、高速のデバッグが可能となっています。

著者について

この記事に関して

製品

Single-Chip Microcomputers: 16-Bit, 25 MIPS, 5v, 2 Serial Ports

16-bit, 10.2 MIPS, 3.3v, 2 serial ports

16-bit, 20 MIPS, 5v, 2 serial ports

16-bit Fixed-Point DSP For Multichannel Applications

16 ビット、40 MIPS、5 V、2 つのシリアル・ポート、ホスト・ポート、40 KB RAM

16-bit, 33 MIPS, 5 v, 2 serial ports, host port, 80 KB RAM

16-bit, 40 MIPS, 5v, 2 serial ports, host port, 20KB RAM

16 ビット、52 MIPS、3.3 V、2 つのシリアル・ポート、ホスト・ポート、80 KB RAM

16 ビット、40 MIPS、5 V、2 つのシリアル・ポート、ホスト・ポート、80 KB RAM

16-bit, 20 MIPS, 3.3v, 2 serial ports, host port

16-bit, 33 MIPS, 5v, 2 Serial Ports, Host Port

DSP Microcomputers With ROM

DSP Microcomputers With ROM

DSP Microcomputers With ROM

DSP Microcomputers With ROM

DSP Microcomputers With ROM

DSP Microcomputers With ROM

DSP Microcomputer

Single-Chip Microcomputers: 16-Bit, 20 MIPS, 5v, 1 Serial Port