概览

设计资源

评估硬件

产品型号带"Z"表示符合RoHS标准。评估此电路需要下列选中的电路板

- EVAL-CFTL-6V-PWRZ ($23.01) Universal Wall Power Supply

- EVAL-CN0269-SDPZ ($135.36) 18-Bit, 1.33 MSPS, 16-Channel Data Acquisition System

- EVAL-SDP-CB1Z ($134.00) Eval Control Board

优势和特点

- 18位、16通道数据采集

- 16路单端、8路差分输入

- 1.33MSPS采样速率

- 250kHz通道开关速率

产品类别

领域和技术

所用产品

参考资料

-

CN-0269 Software User Guide2018/10/22WIKI

-

MT-101:去耦技术2013/11/5PDF954 kB

-

MT-035:运算放大器输入、输出、单电源和轨到轨问题2013/11/5PDF115 kB

-

MT-031: Grounding Data Converters and Solving the Mystery of "AGND" and "DGND"2009/3/20PDF144 kB

-

MT-074: 精密ADC用差分驱动器2009/2/3PDF249 kB

-

MT-048:运算放大器噪声关系:1/f噪声、均方根(RMS)噪声与等效噪声带宽2008/12/11PDF81 kB

-

CN0269:18位、1.33 MSPS、16通道数据采集系统2013/11/20PDF1177 kB

-

了解PuISAR ADC支持电路2020/7/30

电路功能与优势

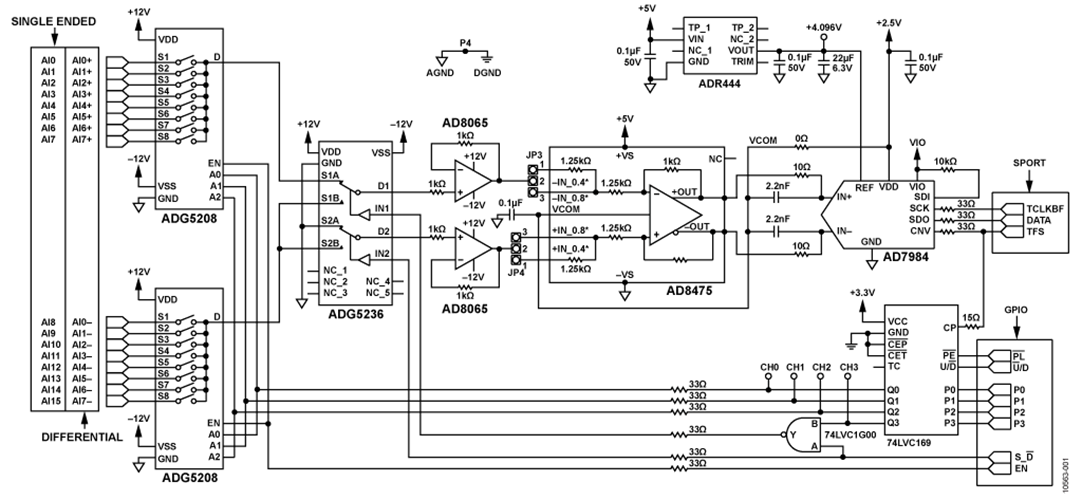

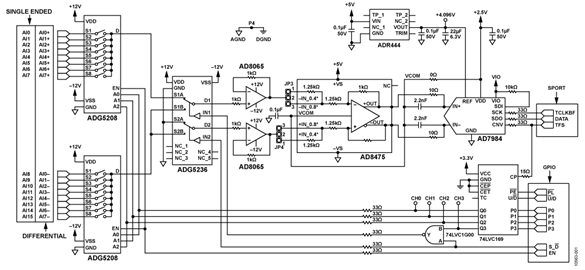

图1显示的是高性能工业信号电平多通道数据采集电路,已针对快速通道间切换进行了优化。该电路能以最高18位分辨率处理16通道单端输入或8通道差分输入。

单通道采样速率高达1.33 MSPS,分辨率为18位。所有输入通道的通道间切换速率为250 kHz,具有16位性能。

信号处理电路与简单的4位增/减二进制计数器结合,提供无需FPGA、CPLD或高速处理器即可实现通道间切换的简单、高性价比方案。可编程设置计数器,使其递增或递减计数,实现顺序采样多个通道;也可加载固定的二进制字,用于单通道采样。

本电路是多通道数据采集卡的理想解决方案,可用于多种工业应用,包括过程控制和电力线监控。

电路描述

图1中的电路是一款经典的多通道异步数据采集信号链,由多路复用器、放大器和ADC组成。

该架构允许使用单个ADC对多通道进行快速采样,具有低成本和出色的通道间匹配性能。

通道间切换速度受限于信号链上多路复用器之后的多个元件建立时间,因为多路复用器会对下游放大器和ADC产生满量程步进电压输出。该电路的元件经过精心挑选,较大程度降低建立时间,提升通道间切换速度。

器件选择

ADG5208 多路复用器根据3位二进制地址线所确定的地址,将8路输入之一切换至公共输出。ADG5236内置两个独立可选的单刀双掷(SPDT)开关。两个ADG5208开关与一个ADG5236结合,允许16路单端通道或8路真差分通道过4位数字控制信号连接信号链的其余部分。

4位数字信号由4位二进制增/减计数器产生,计数器的触发信号与18位、1.33 MSPS AD7984 ADC的转换(CNV)输入是同一个信号。

AD8065 JFET 输入运算放大器带宽为145 MHz,配置为单位增益缓冲器,可提供出色的建立时间性能和极高的输入阻抗。AD8065还提供极低的阻抗输出,驱动AD8475漏斗放大器的衰减级。

全差分信号链具有以下优势:良好的共模抑制性能和更少的二阶失真产物。为了利用现代低压差分输入ADC处理±10 V工业电平信号,有必要使用衰减和电平转换级。

AD8475是一款全差分衰减(漏斗)放大器,集成精密增益电阻,提供0.4倍或0.8倍的精密衰减、共模电平转换和单端至差分转换,以及输入过压保护等功能。快速建立时间(0.001%建立时间为50 ns)以及低噪声性能(10 nV/√Hz)使得AD8475非常适合用来驱动采样速率最高为4 MSPS的18位差分输入ADC。

本电路选取了AD7984——一款18位PulSAR® ADC,对单通道进行采样时,该器件能以1.33 MSPS的速率提供18位分辨率。但是,顺序切换通道时,信号链上各种元件的建立时间限制了整体精度。例如,以250 kHz速率进行通道间切换时,具有16位性能。

For a detailed timing and noise analysis of the circuit, please refer to the CN0269 PDF.

测试结果直方图

图16显示10,000个样本的测试结果直方图。测试时,将16路单端通道短接在一起,并与PCB的GND相连。注意,峰峰值噪声约为12 LSB,包括输入缓冲器。

交流测试结果

在系统级执行交流性能测试,AD7984采样速率为300 kSPS,由1051 B&K型正弦发生器提供2.5 V峰峰值、10.675 kHz的输入正弦波信号。电路在通道4上连续采样,不包括输入缓冲器的效应。FFT显示SNR = 91.33 dBFS。

开关速度和建立时间测试结果

下图显示建立时间性能。实验室测试设置如图18所示。

CN-0269评估板配置为16通道单端输入模式,8个奇数通道短接在一起,8个偶数通道短接在一起。

一组电池用于产生不同的直流输入电压,实现低噪声和低阻抗性能。

奇数和偶数通道连接至不同的电压。LabVIEWTM软件控制EVAL-SDP-CB1Z间参数,并在输入通道间连续切换。开关速率范围为100 Hz至1 MHz,以1 kHz为增量。每种开关速率下获取10个样本,并对结果求均值。开关速率最低的平均值用作参照点。对10个样本和参照值求差值,即可计算每种开关速率下的误差。测试结果如图19和图23所示。

图中,2 LSB误差对应于17位建立时间,而4 LSB误差对应于16位建立时间。

如上图所示,可以看出,在低于1 MHz的开关速率下,带有输入缓冲器的电路比不带前置缓冲器的电路具有更佳的建立时间性能。

图21、图22和图23显示连接输入缓冲器后,电路以高于250 kHz的通道间开关速率建立至16位的情况。

常见变化

18位AD7984采用10引脚MSOP或10引脚QFN (LFCSP)封装。有很多其他的PulSAR ADC产品也采用这种封,辨率为14/16/18位,并提供各种采样速率。

缓冲放大器的另一种选择是 ADG12xx 。如果需要可编程增益,则AD8250、AD8251和AD8253的0.001%建立时间为685 ns。如果要求具有更低的电容,则可以使用ADG12xx系列多路复用器。

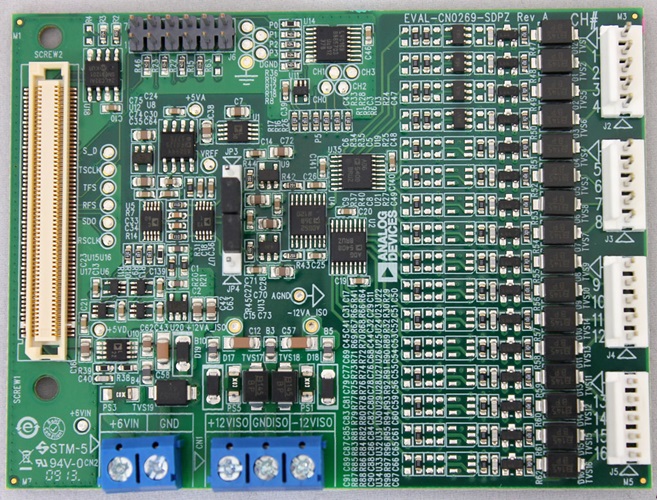

电路评估与测试

本电路使用 EVAL-CN0269-SDPZ 电路板和 EVAL-SDP-CB1Z SDP-B系统演示平台控制器板。这两片板具有120 引脚的对接连接器,可以快速完成设置并评估电路性能。EVA L-CN0269-SDPZ板包含要评估的电路,如本笔记所述。SDP-B控制器板与CN-0269评估软件一起使用,可从EVA L-CN0269-SDPZ电路板获取数据。

设备要求

需要以下设备:

- 带USB端口的Windows® XP(32位)、Windows Vista®或Windows 7 PC

- EVAL-CN0269-SDPZ 电路板

- EVAL-SDP-CB1Z SDP-B 控制器板

- E VA L-CN0269-SDPZ评估软件

- 6 V直流(500 mA)、±12 V(300 mA)电源

- 低失真信号发生器,提供±10 V输出,频率为直流至1 MHz

开始使用

将CN-0269评估软件光盘放进PC的光盘驱动器,加载评估软件。打开 我的电脑找到包含评估软件的驱动器。

功能框图

完整的电路原理图见EVAL-CN0269-SDPZ-SCH-RevX.pdf文件。此文件位于CN-0269设计支持包中:图24显示测试设置的功能框图。

设置

将EVAL-CN0269-SDPZ电路板上的120引脚连接器连接到EVAL-SDP-CB1Z控制器板(SDP-B)上的 CON A 连接。 在断电情况下,将一个6 V和±12 V直流电源连接到板上标有+6 V、±12 V和GND的引脚CN1、CN2。如果有6 V壁式电源适配器,可将其连接到板上的管式连接器,代替6 V电源。SDP-B板附带的USB电缆连接到PC上的USB端口。此时请勿将该USB电缆连接到SDP-B板上的微型USB连接器。同时接通6 V和±12 V电源,然后将USB电缆连接到微型USB连接器。

测试

开启6 V和±12 V电源后,启动评估软件程序。一旦建立USB通信,就可以使用SDP-B板来发送、接收、捕捉来自E VA L-CN0269-SDPZ板的串行数据,并在时域和频域下进行数据分析,以便评估整个电路的性能。

图25显示EVAL-CN0269-SDPZ评估板连接后的照片。有关SDP-B板的信息,请参阅 SDP-B用户指南。

有关测试设置、校准以及如何使用评估软件来捕捉数据的详细信息,请参阅CN-0269 软件用户指南。

针对原型开发的连接

EVAL-CN0269-SDPZ评估板设计为通过SPORT端口,与基于Black-Fin DSP的EVAL-SDP-CB1ZSDP-B板共同评估;但是,任何微处理器都可通过14引脚PMOD连接器连接AD7984的串行端口。为使另一个控制器能与EVAL-CN0269-SDPZ评估板一同使用,第三方必须开发相应的软件。

目前已有一些转接板能实现与Altera或Xilinx现场可编程门阵列(FPGAs)的接口。利用Nios驱动器,Altera的BeMicro SDK板能配合BeMicro SDK/SDP转接板一同使用。任何集成FMC连接器的Xilinx评估板均可与FMC-SDP转接板一同使用。