資料ライブラリ

AN-1478: 特定のシステム条件を対象とする絶縁型SPI バス

はじめに

シリアル・ペリフェラル・インターフェース(SPI)は、マイクロプロセッサとペリフェラル・デバイス間の短距離通信に多用される同期シリアル・バス・インターフェースです。SPI バスは、厳格に規定されたプロトコルではなく、様々な方法で実現することができます。多くの場合、ガルバニック絶縁を組み込む必要性があり、これを組み込むことによりメリットが得られます。このアプリケーション・ノートでは、高速な通信速度、プリント回路基板(PCB)の限られた実装面積、および低消費電力といったシステム・レベルの課題に直面している設計者向けに種々のSPI アイソレーション技術について説明します。また、このアプリケーション・ノートは、様々なSPI アイソレーション・ソリューションのセレクション・ガイドとしての役割も果たします。

SPI プロトコルは一般に、単方向の4 つのシングルエンド・チャンネルで構成されています。SPI マスタは、クロック、シリアル・データ、およびスレーブ・セレクトという3 種の信号を出力します。スレーブ・デバイスからは、マスタ・デバイスに戻る1 本のシリアル・データ・ラインがあります。kbps~数Mbpsのデータ・レートの場合、この物理層は比較的簡単なプロトコルでSPI を構成し、マスタ・デバイスとスレーブ・デバイス間のガルバニック絶縁を実現しています。標準的な4 チャンネルのデジタル・アイソレータは、多くの場合、全二重通信向けの妥当でトランスペアレントなドロップ・イン・ソリューションになります。データ・レートが高くなると、別の技術が必要になります。

クロックを極限まで高速化

より一般的で従来からある方式は、1 個のマスタ・デバイスが1個以上のスレーブ・デバイスと全二重通信を行う形をとります。マスタ・デバイスは、チップ・セレクト・ラインをローに設定し、クロック信号を送信することにより、スレーブ・デバイスとの通信を開始します。マスタと選択されたスレーブは両方とも、クロックの立上がりエッジでバスに書き込み、クロックの立下がりエッジでバスから読み込みます。この形態のSPI 通信は、図1と図3に例示するようなシステムで使用されています。

図1. 標準的なSPI の実装

3 つの順方向チャンネルと、1 つの逆方向チャンネルを備えた標準的な(3/1)デジタル・アイソレータ

方向性のあるチャンネルには、簡単なプロセスで絶縁を付加することができます。SPI を絶縁する場合に、デジタル・アイソレータは自然な選択肢です。なぜなら、短い伝搬遅延、良好なチャンネル間マッチング、小型の1 チップ・ソリューション、堅牢な通信、および簡易実装を実現できるためです。これらの特長から、デジタル・アイソレータはフォトカプラ・ソリューションと比べて優位性があります。

データ・アクイジション・システムにおいて、スループット・レートは上昇し続けています。伝搬遅延が短い場合でも、この伝搬遅延によって全二重通信の最大データ・レートは制限されます。この影響は図2 と図4 の差異に現れています。

図2. 標準的なSPI のタイミング図

クロック・レートの制限

全二重通信を簡単に実装するには、SPI の最大クロック速度を算出するために、デジタル・アイソレータの仕様をいくつか検討する必要があります。最小パルス幅、最大データ・レート、および伝搬遅延はすべて、制限要素になる可能性があります。

図3 は、汎用の3/1 クワッド・チャンネルを備えた標準的なデジタル・アイソレータをガルバニック絶縁向けのドロップ・イン・ソリューションとして使用した、SPI バス・ソリューションを示しています。SPI クロック信号は、状態が1 周期あたり2 回変化します。ただし、デジタル・アイソレータを通過するデジタル・データについては該当しません。標準的なデジタル・アイソレータは、クロック信号をサポートする最大データ・レートの仕様を備えている必要があります。例示しているこのデバイスでは、最大データ・レートの仕様は制限要素になりません。

図3. 標準的なデジタル・アイソレータのSPI アイソレーション

図4 の伝搬遅延の影響に注目してください。この例では、データはクロックの立上がりエッジで送信され、立下がりエッジで受信されます。

図4. 絶縁を施した標準的なSPI のタイミング図

マスタ・デバイスは、クロックとマスタ・アウト・スレーブ・イン(MOSI)信号の送信を同時に開始します。スレーブ・デバイスから送信されるマスタ・イン・スレーブ・アウト(MISO)信号は、クロックの立上がりエッジでトリガされますが、クロック・エッジが遅延するため、MISO 信号も遅延します。このとき、MISO 信号は、マスタに到達する前に標準的なデータ・アイソレータを通過する必要があります。この例では、スレーブとマスタは両方ともクロックの立下がりエッジでデータを読み込みます。

SPI 通信は、MISO信号に同期したクロック信号に依存します。図5 は、データ・レートが増加して通信が破綻したときの伝搬遅延の影響を示しています。伝搬遅延のために、クロックの立下がりエッジで読み込むポイントが、MISO 信号が安定しているときではなくMISO 信号の遷移点になっています。このシステムのデータ・レートは高すぎるため、通信の信頼性を確保できません。

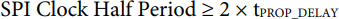

図5. マスタ側から見たタイミング図

図5 に示すように、スレーブに行ってマスタに戻るまでの伝搬遅延は、SPI クロック周期の半分未満でなければなりません。アプリケーションでは、PCB のパターン遅延、セットアップ・タイム、およびスレーブ応答時間によって最大クロック・レートが更に減少する可能性があります。このアプリケーション・ノートでは、簡素化のためにこれらの要因を無視し、全二重通信を簡単に実装するために以下の関係を保ちます。

データシートの最大伝搬遅延値を用いて、最大データ・レートを算出します。システムは、実験室ではより高い速度を達成できますが、堅牢な通信を確保するために、温度や電源電圧の変動、およびデバイスのばらつきに配慮する必要があります。表1は、アナログ・デバイセズの様々なデジタル・アイソレータについて、最大SPIデータ・レートの一覧を示しています。

| Part Number | Data Rate (Maximum) | Value | Value | Value |

| ADuM1401ARWZ | 1 Mbps | 100 ns | 500 kHz1 | Isolated SPI benchmark |

| ADuM1441 | 2 Mbps | 180 ns | 1 MHz1 | Ultralow power, intrinsic safe for IS-IS isolation under IEC60079-11 |

| ADuM7441 | 25 Mbps | 50 ns | 5 MHz | Ultralow power, intrinsic safe for IS-IS isolation under IEC60079-11 |

| ADuM141D/ADuM141E | 150 Mbps | 13 ns | 19.2 MHz | High robustness to radiated and conducted noise, 1.8 V operation, package options as small as QSOP available |

| ADuM241D/ADuM241E | 150 Mbps | 13 ns | 19.2 MHz | High robustness to radiated and conducted noise, 1.8 V operation, 5 kV withstand |

| ADuM3151/ADuM3152/ ADuM3153 |

34 Mbps | 14 ns | 17.8 MHz | High data rate, three additional 250 kbps control/signal channels, small SSOP footprint |

| ADuM4151/ADuM4152/ ADuM4153 |

34 Mbps | 14 ns | 17.8 MHz | High data rate, three additional 250 kbps control/signal channels, 5 kV withstand |

| 1 最小パルス幅の仕様によって制限されます。 | ||||

独立した遅延クロック(ラップされたクロック)

一部の全二重通信のアプリケーションでは、標準的なデータ・デジタル・アイソレータをSPI シグナル・チェーンに単純に挿入して得られるデータ・レートよりも高いSPI データ・レートが要求されます。図5 に示すような同期の難題は、クロック信号とマスタに向かうMISO 信号を一緒に戻せば、うまく処理することができます。高速のデータ・レートは達成可能ですが、この方法を使用する場合に考慮すべきことは、SPI のマスタの設計が複雑化することです。一般に、遅延したMISO 信号とクロック信号を読み込むにはシフト・レジスタを付加する必要があります。

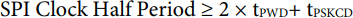

標準的なデータ・アイソレータを実装した状態で遅延クロックを独立させる技術を用いるには、マスタ・クロック信号を戻す(ラップ・バックする)ためにアイソレーション・チャンネルを追加する必要があります。ラップされたクロック信号は、追加されたアイソレーション・チャンネルを通ってマスタに戻ります。この遅延したクロック信号は、スレーブに行くMOSI 信号やスレーブから戻って来るMISO 信号が遅延するのと全く同様に、アイソレータの順方向と逆方向の伝搬遅延によって遅延します(図6 を参照)。この方法では、チャンネル間マッチング時間の仕様値が低いデジタル・アイソレータを使用することが重要です。(スレーブでの遅延とパターンによる遅延を無視した)最小SPI クロック周期は、最大パルス幅歪みと、同方向チャンネル間マッチングの仕様によって決まります。算出するSPI クロックの半周期の最小値は、デバイスの最小パルス幅の仕様よりも確実に大きくしてください。

例えば、ADuM152Nは、最大パルス幅歪みが4.5nsで、最大同方向チャンネル間マッチングが4.0ns であるため、理論的には38.4MHz の最大クロック速度を実現できますが、実際にはパターン長とスレーブ応答での遅延を考慮する必要があります。

図6. アイソレーション・チャンネル遅延を用いた高速SPI

SPI デジタル・アイソレータのADuM3150 とADuM4150 は、標準機能として遅延クロック信号を調整することができます。図7 に示すように、ADuM3150 は1 次側に遅延回路を実装しています。ADuM4150も、1次側に遅延回路を実装しています。各アイソレータの往復伝搬遅延をマッチングさせるため、遅延クロック(DCLK)信号はADuM3150 の出荷テストで調整されます。図6 とは異なり、ADuM3150 ではアイソレーション・チャンネルを追加する必要はありません。これらのSPI デジタル・アイソレータは、最大40MHz のクロック・レートに対応可能です。

図7. 高精度のクロック遅延を用いた高速SPI

| Part Number | Supply Voltage (V) | SPI Clock (Maximum) | Distinct Special Features |

| ADuM152N/ADuM162N | 1.7 to 5.5 | 38.4 MHz | High robustness to radiated and conducted noise, 1.8 V operation |

| ADuM252N/ADuM262N | 1.7 to 5.5 | 38.4 MHz | High robustness to radiated and conducted noise, 1.8V operation, 5 kV withstand |

| ADuM3150/ADuM4150 | 3.0 to 5.5 | 40 MHz | Delayed clock feature, two additional 250 kbps control/signal channels, small SSOP footprint |

遅延リードバック・アイソレータ

遅延したMISO データ信号を同期させる場合に、遅延したクロック信号を加える代わりに、遅延リードバック・アイソレータを使って、バス上で次に続くワードにクロックが与えられるまで、1 次側でMISOデータをバッファリングすることもできます。MISO データをバッファリングすることによって、マスタは遅延クロックをサポートする必要がなくなります。このプロセスでは、アプリケーションがMISO データ内で1 ワードの遅延を許容する必要があります。データが主にマスタからスレーブに書き込まれるアプリケーションでは、これは大きな問題にはなりません。3 つの双方向選択信号や低ジッタのLOAD信号も備えるLTM2895 は、遅延リードバック技術を実装しているため、D/A コンバータ(DAC)を絶縁するのに最適です。

LTM2895 では、キー信号の重要なエッジを絶縁障壁を越えて転送するだけで、クロックが100MHz のSPI バス動作をサポートします(図8 を参照)。内蔵されたステート・マシンとバッファの組み合わせを使用すると、LTM2895 はSPI 信号を完全に再生することができます。SPI クロック周波数やワード長などの必要な設定情報は、SPI インターフェースと2 次側のスレーブ・セレクト(SSB)を介して設定されます。LTM2895 の設定後は、この2 次側のスレーブ・セレクトを、絶縁された2 次側のSPI デバイスへの書込み用に転用できます。

図8. 超高速DAC ストリーミング・アイソレータ

LTM2895 の1 次側と2 次側は、順方向と逆方向に各1 本の高速非同期シリアル・リンクを使用することで、絶縁障壁を越えて内部通信を行います。割込み優先度制御方法により、タイミングの重要な信号は低レイテンシーと低ジッタで確実に更新されます。

図9 は、LTM2895 の通常動作シーケンスを示しています。このシーケンスは、1 次側の(SS)の立下がりエッジから始まり、対応する2 次側の(SS2)の立下がりエッジが生成され、前もってサンプリングされたMISO2 ワードのMSB がMISO から出力されます。1 次側のSCLK の最初の立上がりエッジによってLTM2895 がトリガされると、MOSI がサンプリングされ、障壁を越えて情報が送られます。2 次側のステート・マシンがこのデータを受信したとき、このマシンはMOSI2 を更新し、SCLK2を(SPI クロックの周波数設定によって決まる)一定時間だけローに保ちます。SCLK2 に対して仕様規定されたローの時間が経過した後、2 次側のステート・マシンはSCLK2 を起動させ、MISO をサンプリングして、データを1 次側のバッファに送ります。1 次側のSCLK が立ち下がると、バッファリングされたMISO データは更新されます。SCLK の次の立上がりエッジによって、SCLK2 は仕様規定された時間だけローになります。一方、他の信号は同じ状態を維持します。SSが立ち上がると、SPI の処理は終了し、MISO はハイ・インピーダンスに駆動され、2 次側のSCLK2 とMOSI2 はローになり、SS2はハイになります。LTM2895 が選択されていないとき、MISO はハイ・インピーダンスになっているため、MISO は他のスレーブ・デバイスと共に1 次側のSPI バスを共有できます。

図9. LTM2895 のSPI タイミング

MISO データ・バッファは循環バッファであり、ワード・サイズを設定することによって区分される読出しポインタと書込みポインタを使用します。

66MHz または100MHz のSPI クロック周波数が選択された場合、LTM2895 は伝搬時間とセットアップ・タイムを増やすために、SCLK の立上がりエッジで1 次側のMISO データを更新します。

SPI ページ・モードは、SSをローに保つと同時に、目的のワード長の倍数だけクロックを与えるとサポート可能です。

DAC 入力にLOADを備えるDAC を絶縁する場合、LTM2895 のLOAD信号は、立下がりエッジ間でジッタ(代表値が30ps rms)を伴う短いパルスになります。LTM2895 はLOAD2の立上がりエッジを生成しますが、このときのパルス幅は40ns または60ns になり、SCLK2 の周波数の設定値に依存します。

絶縁電源を内蔵

電源を独立させると、アプリケーションによっては不経済なことや、不可能なこともあります。これらの設計では、1次側から絶縁された電力を2次側のデバイスに供給する必要があります。絶縁の堅牢さと認定条件を満たそうとすると、従来の絶縁電源ソリューションでは、大型化し、困難を伴います。これらの課題は、いくつかのisoPower®またはμModule®デバイスを使って簡単に対処できます。ADuM5411はそのようなソリューションの1つです(図10参照)。このデバイスは、最大150mWの内蔵絶縁電源と共に4つの絶縁信号チャンネルを備えており、しかもサポート用のバイパス・コンデンサも含めて、わずか90mm2の実装面積しか占有しません。150mWの内蔵絶縁電源があれば、多くの場合、高精度のADCや低消費電力のマイクロコントローラ・ユニット(MCU)を十分にサポートすることができます。

図10. isoPowerを用いたSPIアイソレーション

更に高い絶縁電源条件における絶縁SPIアプリケーションについては、表3に示すような別のソリューションも提供しています。ADuM5401は、それ自身で最大500mWの絶縁電力を供給可能です。また、ADuM5401は、互換性のある別のisoPowerデバイスを制御する能力を考慮して設計されています。ADuM5401はマスタとして動作可能で、パルス幅変調(PWM)信号を1個以上のADuM5000デバイスに送り、自身とスレーブの各ADuM5000デバイスを調整することができます。

| Part Number | Isolated Supply Voltage | Isolated Power | Data Rate (Maximum) | Drop In, Full Duplex SPI Clock (Maximum) |

| ADuM5411 | Adjustable 3.3 V to 5 V | 150 mW | 150 Mbps | 19.2 MHz |

| ADuM5401 | Fixed 3.3 V or 5 V | 500 mW | 25 Mbps | 4.1 MHz |

| ADuM5401/ADuM5000 | Fixed 3.3 V, 5 V | 1 mW | 25 Mbps | 4.1 MHz |

| LTM2883-S | Fixed 5 Fixed +12.5 V Fixed −12.5 V |

100 mW 250 mW 187.5 mW |

20 Mbps | 4 MHz |

| LTM2886-S1 | Adjustable 3.0 V to 5 V Fixed +5 V Fixed −5 V |

500 mW 500 mW 500 mW |

20 Mbps | 4 MHz |

| LTM2887-S | Adjustable 3 V to 5 V Adjustable 0.6 V to 5 V |

500 mW 500 mW |

20 Mbps | 4 MHz |

| ADuM3471 | Adjustable 3.3 V to 24 V | 2 W | 25 Mbps | 4.1 MHz |

| 1 全出力電力は最大1Wです。 | ||||

LTM2883-S、LTM2886-S、およびLTM2887-Sは、6チャンネルのデジタルμModule(マイクロモジュール)アイソレータで、最大1Wの出力電力を供給する能力があり、様々な出力電圧範囲のオプションを備えています。ADuM3471は、スイッチング・レギュレータと共に、SPI用の4つの絶縁データ・チャンネルを内蔵しています。このデバイスは、外付けトランスを用いて、3.3V~24Vで最大2Wの安定化した絶縁電源を提供します。ADuM3471の出力機能は、アナログ出力モジュールなど、より高い電力とより広い電圧範囲が必要なシステムで絶縁電源を供給するのに適しています。

補助データ・チャンネル

複数のスレーブの選択に加え、低速チャンネルでは、図11に示すように、絶縁障壁を越えて別の制御信号も送信できます。この場合、ADuM3152の低速チャンネルでは、チャンネルの方向を混在させることが可能で、マスタからスレーブへのリセット信号を送信すると同時に、逆方向にパワー・グッド信号と割込み信号を送ることができます。SPIsolator®デバイス・ファミリのデバイスが異なると、補助データ・チャンネルの方向の組み合わせも異なります。

図11. 補助機能を備えたSPIアイソレーション

複数のスレーブ制御

複数のスレーブを1 つのSPIバスに接続する場合、デイジーチェーンと独立スレーブ構成という2 つの方法があります。デイジーチェーンでは、1 本のスレーブ・セレクション(SS)ラインだけを必要とし、チェーンの全内容は1 つの絶縁されたポートを通してシリアルに出力されます。データ・アクイジションのシーケンスが固定されていないときは、各SPI スレーブを個別にアドレス指定する必要があります。

簡単なソリューションとして、ADuM161N などのデジタル・アイソレーション・チャンネルを追加する方法があります。このソリューションは、正確なタイミングのSS 信号が要求されるシステムで推奨されます。例えば、スレーブがADCのとき、SS信号はデータ変換の起動も行います。

タイミングの制限が緩やかなアプリケーションでは、4 つの高速チャンネルと1 つの低速チャンネルが内蔵されたADuM3154アイソレータを用いると、図12 に示すような別のソリューションを実現できます。ADuM3154 は、17MHz の最大SPI クロック速度をサポートし、最大4 個の独立したスレーブを制御します。マルチプレクサを選択するラインの伝搬遅延は100ns~2.6μs であり、これは内部サンプリング・クロックを基準にして、入力データのエッジが変化する位置に依存します。3 つのアイソレーション・チャンネルをなくすことで、このソリューションは標準的なデジタル・アイソレータ・ソリューションと比べて小型化が図れ、費用対効果が高くなります。

図12. 複数のスレーブ制御を備えるSPI アイソレーション

図13 に示すように、マスタが別の絶縁プレーン上にある複数のスレーブと通信する場合、デジタル・アイソレータはマスタ側のMISO ラインをトライステートにする能力を備えている必要があります。MISO をトライステートにできないと、デジタル・アイソレータの出力ピン同士が競合するため、通信することができません。

図13. 絶縁されたスレーブ同士のMISO を選択するためのトライステート

アイソレータからのMISO 信号を選択するためのトライステート・バッファは、マスタ、非絶縁スレーブ、および絶縁スレーブでも必要です。

超低消費電力のアプリケーション

絶縁は安全な電子システムのために必要と考えられますが、一方で負荷と考えることもできます。なぜなら、絶縁によって通信速度が制限され、ボード・スペースが占有され、更にかなりの量の電力が消費されるためです。前の2 つの項目については、クロック速度を極限まで増加し、ボード・スペースを最小限に抑える技術革新によって対処しています。アプリケーションの中には、バッテリ駆動のデバイス、4mA~20mA のループ駆動の工業用トランスミッタなど、極めて低い消費電力が求められるものもあります。現在のところ、デジタル・アイソレータの消費電力はフォトカプラよりもかなり低いとはいえ、これらの新しいアプリケーション分野への参入を可能にするためには、2~3 桁低くする必要があります。

データ・レートが固定されると、デジタル・アイソレータの電力レベルは、主にデータ・エンコーディング方式によって決まります。これらの方式は、パルス・エンコーディング・アーキテクチャと、オン・オフ・キーイング(OOK)アーキテクチャに大別されます。パルス・エンコーディング方式では、低いデータ・レートで電源電流の消費が少ないという利点があるのに対して、OOK ではパルス・エンコーディング方式よりも高いデータ・レート(10Mbps 以上)で電流の消費が少なくなります。ほとんどの低消費電力アプリケーションでは、SPI クロック速度を1MHz 未満で動作させるため、パルス・エンコーディング方式のほうが優れています。

しかし、パルス・エンコーディング方式には、1 つの欠点があります。入力でロジックの変化がないと、データは出力に送信されません。このため、システム起動後に入出力間にミスマッチが起きたり、外来ノイズによって出力データが反転したりすることがあります。定期的にDC 状態を再送することで、この問題を解決できます。ほとんどのパルス・エンコーディング・デジタル・アイソレータは、DC 状態を1μs ごとにリフレッシュしますが、データ・レートが低下したときに消費電力の減少が止まるポイントをリフレッシュ・レートによって設定することもできます。

ADuM1441 は、リフレッシュ・レートを17kHz まで低減することによって超低消費電力を実現します。消費電力を最低にするために、リフレッシュ回路を完全にディスエーブルすることができます。図14 に示すように、ADuM1441 は、リフレッシュ回路がディスエーブルされている状態で、消費電力をμW の範囲まで低減できます。システム設計者は、消費電力とデータの完全性とのバランスを保つため、更にずっと低い周波数でDC の精度を確保するためのパルスを送信することもできます。

図14. ADuM1441 でのチャンネルあたりの合計電源電流(VDDX = 3.3V)

大多数のフィールド計測器は、ループ駆動のデバイスです。ループから得られる電力によって、センサーやすべての補助電子回路など、計測器内部のすべての回路を駆動させる必要があります。最小ループ電流が4mA であるため、このような設計で使用可能な3.5mA の最大許容システム・パワー・バジェットを増加することはできません。消費電力は、フィールド・トランスミッタを設計するための部品を選択するときに、最も重要な考慮事項です。最も標準的なデータ・デジタル・アイソレータが両側で数mA の電流を消費するのに対して、図15 に示すように、ADuM1441 とその超低消費電力性能は絶縁されたフィールド計測器内でこの機能性を可能なものとします。

図15. 4mA~20mA のループ駆動計測器内での超低消費電力SPI アイソレーション

まとめ

SPIバスの絶縁は、マスタとスレーブの間にクワッド・チャンネル・デジタル・アイソレータを挿入するだけにとどまらない複雑なものになることがあります。ノイズ耐性と安全性のためにガルバニック絶縁を行う必要があるデータ・アクイジション・システムで、スループットが犠牲になることはもはやありません。最近の技術革新によって、最大100MHzの絶縁クロック速度が実現されています。表に現れない(すなわちクロック速度を落とさない)アイソレータが、このような高速で実現されるのは初めてのことです。小型のパッケージに信号と電力の絶縁を内蔵することにより、SPIの絶縁と2次側の電源のための設計が極めて簡素化され、ディスクリート・ソリューションと比べて、ボード・スペースとコストが大幅に削減されます。低速アイソレーション・チャンネルも内蔵したことで、複数のスレーブ制御や補助チャンネル・アプリケーションにおいて、小型化と費用効果の高いオプションを実現できます。超低消費電力向けに最適化された高度なパルス・エンコーディング技術を適用することにより、電源の制限により以前は不可能であったSPIの絶縁が実現されています。

このアプリケーション・ノートで説明した製品の詳細については、www.analog.com/jp/icouplerを参照してください。

参考資料

Cantrell, Mark, “Ultralow Power Opening Applications to High Speed Isolation,” MS-2644, April 2014.