帯域幅の広いセンサー・アプリケーションに最適なSPIの絶縁方法

SPI(Serial Peripheral Interface)は、多くの設計者からの支持を得て、広範なアプリケーションで活用されています。もちろん、それには多くの理由があります。まず、SPIバスを使えば高速にデータをやり取りすることができます。1つのボード上に実装された複数のIC間といった短い距離であれば、最高60Mbpsのデータ転送速度が得られます。また、SPIのバスはシンプルなコンセプトに基づいて実現されます。必要なのは、クロック、2つのデータ信号、チップ・セレクト信号だけです。やり取りされるデータは、クロックの1つの位相に対応して供給され、その逆の位相に対応して読み出されます。そのため、遅延や速度のミスマッチに対してかなりのマージンを確保することができます。更に、単方向の信号ラインでバスを構成できるので、例えばマイクロプロセッサの内部にも簡単に実装することが可能です。加えて、制御の流れについて多くの配慮は必要ないため、フォトカプラやデジタル・アイソレータによって容易に絶縁することができます。つまり、本質的に単方向にしか対応しないアイソレータでも問題なく使用できるということです。

産業分野では、温度や圧力などを監視するシステムが広く使用されています。そうしたアプリケーションでは、センサー用のフロント・エンドに比較的サンプル・レートの低いA/Dコンバータ(ADC)が含まれていることが多いでしょう。SPIによって、そうしたADCと通信を行う場合、高いクロック・レートは必要ありません。また、絶縁用の回路も様々な技術を用いて簡単に実装できるはずです。しかし、要件というのは、時の流れと共に高度化するものです。実際、配線が長く、データ・レートが高く、絶縁の要件が厳しいアプリケーションが続々と登場しています。その結果、古くから使われてきたSPIも、性能の面でより限界に近いレベルで利用されるようになっています。本稿では、SPIを利用する上での制約事項や、絶縁システムにおける制約への対処法などについて説明します。

絶縁型のSPIについても、様々なアプリケーションによって性能の限界が押し上げられています。そうしたアプリケーションの例としては、広いダイナミック・レンジが求められるセンサー用のインターフェースが挙げられます。ダイナミック・レンジの広いシステムを構築するためには、まずS/N比の高いADCを選択することになります。通常、ADCのS/N比はA/D変換後のデジタル・データのビット数に依存します。そのため、分解能が16ビット程度のADCが選ばれます。更に広いダイナミック・レンジが必要な場合には、入力信号を可変ゲインで増幅する手法やオーバーサンプリングなどの手法が適用されます。オーバーサンプリングは、いわば帯域幅と引き換えにノイズを低減する手法です。一般に、サンプリング周波数を2倍にすると、ノイズ性能は3dB向上します。75倍のオーバーサンプリングを適用すると、ノイズ性能とダイナミック・レンジが約18dB向上するといった具合です。より具体的に言えば、75倍のオーバーサンプリングを適用し、ADCを900kSPSで動作させると、約6kHzの帯域幅にわたって18dB高いダイナミック・レンジが得られることになります。帯域幅とダイナミック・レンジはトレードオフすることが可能です。ただ、ADCをできるだけ高速に動作させれば、大きなメリットが得られることは間違いありません。その場合、SPIバスは大量のデータに対応しなければならないということになります。以下では、サンプル・レートの高いアプリケーションで使用されるADCを例にとり、SPIバスを介して通信を行う場合にシグナル・チェーンの性能にどのような影響が及ぶのかを明らかにします。なお、ADCとしては、最大2.5MSPSで動作するPulSAR®シリーズの「AD7985」のような製品を想定しています。

ADC用のインターフェース

多くのADCは、アナログ信号をデジタル・データに変換する際、図1に示すような時間配分で2つの基本的な動作を行います。図中のtCONVは、ADCの変換時間を表します。この時間中に、入力電圧に対応するデジタル・データ(ワード)を生成するための内部処理が実行されます。続くtACQはアクイジション時間と呼ばれます。この時間中に、取得したデジタル・データがデジタル・インターフェースを介してコントローラに転送されます。また、一般的なADCでは、次の変換を開始できるようになるまでの最小サイクル時間tCYCが定義されています。その長さは、ほぼtCONVとtACQの和に等しくなります。但し、ADCがデータのアクイジションと転送をオーバーラップさせる特殊な転送モードを備えている場合、tCYCはtCONVとtACQの和よりも短くすることができます。以下では、説明の内容を理解しやすくするために、変換とアクイジションは逐次的に行われると仮定して話を進めます。

図1. ADCの変換シーケンス(簡略図)

通常、tCONVとtCYCはデータの転送方法には依存しません。それに対し、tACQはデータ用のインターフェースの性質に依存します。つまり、多くの場合、SPIバスの動作に依存することになります。SPIのクロック・レートが原因でtACQが長くなると、ADCのサンプル・レートは著しく制限を受ける可能性があります。

SPIのクロック・レートによる制約

図2に示したのは、マイクロプロセッサやMCU、FPGAといったデジタル・プロセッサ(以下、MCU/FPGA)とADCを接続するSPIリンクの例です。マスタであるMCU/FPGA側とスレーブであるADC側には、それぞれシフト・レジスタが用意されています。SPIバスは、それらシフト・レジスタのペアの間の接続によって実現されています。データの転送に使用する同期クロックは、MCU/FPGAから供給されます。シフト・レジスタは一般的なシフト動作を行います。つまり、シフト・レジスタからは、クロックの1つの立上がりエッジによって1つのデータが出力されます。その立上がりに対応する立下がりエッジで、各シフト・レジスタの他端にデータが入力されます。つまり、リング形式で処理が行われるということです。ADCについては、おそらくMCU/FPGAからのデータをシフト・レジスタによって取得する必要はないでしょう。したがって、そのためのチャンネルとスレーブ・セレクトを省略して簡素化を図っています。ADCは、tCONVの間に内蔵するシフト・レジスタ向けのデータを用意し、tACQの間にシフト・レジスタのデータを出力します。

図2. MCU/FPGAとADCの間のSPIリンクとタイミング・チャート

SPIのトランザクションにおいて、マスタによって生成されたクロックには、スレーブに到達するまでの配線遅延が加わります。また、更にいくらかの内部遅延を経て、スレーブによるデータの出力がトリガされます。一方、クロックの立下がりエッジまでにマスタに返されなければならないデータの信号にも配線遅延が加わります。通常、マスタはこのラインに対するいくらかのセットアップ時間も必要とします。図2には、そうした遅延について説明したタイミング・チャートも示してあります。ご覧のように、上記の3つの遅延によって、マスタ・クロックの半周期の最小値が決まることがわかります。通常、非絶縁型のシステムでは、これらの時間は非常に短くなります。多くの場合、10ナノ秒未満なので、SPIのクロック周波数として50MHzを超える値を選択することができます。

図3に示したのは、SPIのデータ・パスに絶縁バリアを追加した例です。このようにすると、基板上のパターンによる遅延に似た遅延が更に追加されます。絶縁による信号伝搬遅延tpISOは、利用する技術によっては100ナノ秒以上に達する可能性があります。図3には、その遅延の影響も踏まえたタイミング・チャートも示してあります。絶縁の影響も加えた新たな遅延によって、データのトランザクションに必要な時間は長くなります。結果として、SPIのクロックの半周期が大幅に長くなることがわかります。絶縁による遅延は、システム内の他のどの遅延よりも長くなります。それによって、最高クロック周波数は数MHzにまで低下する可能性があります。

図3. 絶縁バリアを追加したSPIリンクとタイミング・チャート

クロック周期については、次のエッジまでに、マスタにデータを供給しなければならないということが最大の制約になります。この制約は、非絶縁型のシステムではさほど大きな問題ではありません。実際、タイミングのマージンはかなり大きいので、データ転送の面では堅牢性が高いと言えます。しかし、データ・パスにおける伝搬遅延が半周期の中で大きな割合を占めるようになると、バスの最大速度が著しく低下します。

上記の制約を回避するにはどうすればよいでしょうか。仮に、スレーブから返ってくるデータとの同期がとれた独立したクロックが存在したとします。その場合、MCU/FPGAの内部に、そのクロックに基づいてデータを受信する別のシフト・レジスタを用意することができます。そのようにすれば、SPIバスのスループットを制限するのは絶縁バリアの伝搬遅延ではなく、アイソレータのスループットになります。

上記の独立したクロックDCLKは、比較的容易に生成することができます。そのためには、まずアイソレータにマッチングのとれた高速データ・チャンネルを追加します。そして、マッチングのとれたデータ・パスを介し、絶縁型のSPIクロックのコピーをADCからのデータと共に送信すればよいのです(図4)。この遅延クロック方式を採用する場合、絶縁バリアの部分にハードウェアを追加しなければなりません。絶縁チャンネルを追加すると共に、DCLKで動作するシフト・レジスタをMCU/FPGAに用意する必要があります。なお、MCU/FPGAは、標準のSPIレジスタではなく、2つ目の受信レジスタからデータを読み出すことになります。

図4. 独立したクロックを加えた絶縁型のシステム

上述した遅延クロック方式は、様々な絶縁技術と組み合わせることができます。以下では、そうした例を3つ取り上げます。それぞれについて最高速度を定量的に評価すると共に、消費電力とボード上の実装面積について定性的に論じます。標準的な絶縁型のSPIでは、往復の伝搬遅延によって速度が制限されます。それに対し、遅延クロック方式では、アイソレータのタイミング・スキューと歪みによって限界が決まります。これらについて、以下で行う考察によって明らかにします。

フォトカプラによる実装

標準的な産業用アプリケーションでは、高速バスを絶縁するためにシングルチャンネルのデジタル・フォトカプラがよく使われます。標準的な4線式のSPIバスを絶縁するためには、4個のフォトカプラが必要です。CMOSベースの一般的な産業用フォトカプラを使用する場合、SPIクロックの最高レートを見積もる際には、以下のタイミング・パラメータが重要になります。

- 最高データ・レートは12.5Mbps(最小パルス幅が80ナノ秒)

- 最大伝搬遅延tpISOは40ナノ秒

- 最大パルス幅歪みPWDは8ナノ秒

- 部品間の最大伝搬遅延スキューtPSKは20ナノ秒。絶縁型のSPIバスは複数のフォトカプラを使用して構成されるため、このパラメータが重要になります。

SPIのスループットを見積もるために、図3に示した各コンポーネントの標準的な遅延の値を仮定します。各パターン(トレース)による遅延は0.25ナノ秒で、パターンのトータルの遅延tTRACEは1ナノ秒だと仮定します。同様に、スレーブ遅延tSLAVEは3ナノ秒、マスタのセットアップ遅延tMASTERは2ナノ秒であるとしましょう。

図3に示した絶縁型のSPIにおけるクロック・レートについては既に説明しました。それに従えば、上記のフォトカプラにより絶縁したSPIバスにおいて、SPIクロックの半周期に相当する時間は次のようにして求められます。

仮定した値に基づいてこの式の計算を行うと、86ナノ秒という値が得られます。実際のSPIクロックのレート(周波数)は、5.75MHzかそれ以下になるでしょう。明らかに、2×tpISOがSPIバスの速度を著しく低下させる要因であることが見てとれます。

次は、図4に示した遅延クロック方式について考えてみます。すなわち、絶縁されたクロック信号をマスタに返すために逆方向のアイソレータを追加し、遅延クロックを実装するということです。このような構成の回路によって、スレーブから返ってくるデータと同期がとれたクロック信号を生成することができます。その場合、アイソレータにおける往復の伝搬遅延(2×tpISO)は、クロック・レートを制限しません。システムの残りの遅延だけを考慮するので、絶縁型のSPIクロックの半周期は≧ [tTRACE + tSLAVE + tMASTER] nsで決まります。これを計算すると6ナノ秒になります。ということは、SPIクロックの最高レートは80MHzほどになるのでしょうか。残念ながら、話はそれほど単純ではありません。

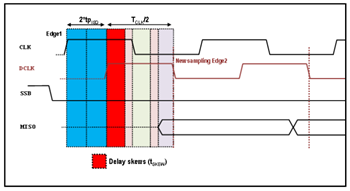

SPIクロックの半周期の最小値は、順方向と逆方向のチャンネルの非対称性を考慮して計算する必要があります。図5では、その非対称性をtSKEWとして示しています。部品間の伝搬遅延スキューと、パルス幅歪みによって、SPIクロックの半周期は次のような式で表されることになります。

これを計算すると62ナノ秒になります。つまり、実際の最高クロック・レートは約8MHzです。ただ、このフォトカプラの最小パルス幅は80ナノ秒なので、最高でも6.25MHzのSPIクロックにしか対応できません。フォトカプラに最小パルス幅の制約がなかったとしても、上記のとおり実際のアプリケーションにおける最高クロック・レートは8MHzです。つまり、tSKEWによって、SPIクロックの最高レートは、遅延が完璧にマッチングしていれば得られるはずの80MHzを大きく下回るということです。

図5. DCLKを含む現実的なタイミング・チャート

では、より最小パルス幅が短く、より高速なフォトカプラを使用すれば、状況は改善するのでしょうか。例えば、最小パルス幅が20ナノ秒の非常に高速なフォトカプラを使用すれば、上記のインターフェースをより高いレートで動作させられるはずです。しかし、そのような高速な製品でも、スキューと歪みが大きいことに変わりはありません。tPSKが16ナノ秒でPWDが2ナノ秒であるとすると、SPIクロックの半周期の最小値は42ナノ秒になります。つまり、最高クロック・レートは11.75MHzほどになります。加えて、フォトカプラのタイミング性能は時間の経過と共に低下していきます。そのため、遅延クロックとスレーブ・データの間のミスマッチは更に大きくなります。そうした変化に対応できるように大きなタイミング・マージンを確保するには、SPIクロックのレートを更に引き下げなければなりません。

加えて、SPIを絶縁するために高速フォトカプラを追加すると、コストが大きく増加します。それだけでなく、基板上の実装面積も増大します。通常、その種の製品の場合、シングルチャンネル品はSO8パッケージで提供されています。上記の構成では5つのチャンネルが必要なので、コストと実装面積が大きく増えるということです。また、絶縁インターフェースの消費電流は、チャンネルあたり最大20mAに達する可能性があります。

デジタル・アイソレータによる実装

ここ十数年の間に、新しい世代のデジタル・アイソレータが提供されるようになりました。そうした製品は、集積度が高く、高速で、伝搬遅延/スキュー/歪みが低く抑えられています。ここでは、4チャンネルのデジタル・アイソレータ製品を例にとって考察することにします。3つの順方向のチャンネルと1つの逆方向のチャンネルを使えば、4線式のSPIバスをコンパクトに絶縁できるからです。フォトカプラの例と同様に、まずはその製品のデータシートでタイミングに関するパラメータの値を調べました。その結果、最小パルス幅は11.1ナノ秒(90Mbps)、最大伝搬遅延tpISOは32ナノ秒、最大パルス幅歪みPWDは2ナノ秒、部品間の最大伝搬遅延スキューtPSKは10ナノ秒であることがわかりました。ただ、シングルチャンネルのフォトカプラとは異なり、4チャンネルのデジタル・アイソレータでは、逆方向のチャンネルのペアの間のマッチングについて考慮しなければなりません。ここで例にとっているデジタル・アイソレータの場合、チャンネル間マッチングtPSKODの値は5ナノ秒でした。

各種の遅延は図3の標準的な値と同じであるとすると、デジタル・アイソレータを用いた絶縁型SPIバスのクロックの半周期は、次の式で表されます。

これを計算すると70ナノ秒になります。つまり、クロックの最高レートは7MHz程度です。フォトカプラの場合と同様に、アイソレータの伝搬遅延によってSPIクロックのレートが大きく制限されることがわかります。ただ、標準的なCMOS技術で製造されたデジタル・アイソレータは、製品の使用期間を通して非常に安定したタイミング性能を示します。したがって、同性能の変化に対応するために大きなマージンを確保することなく、SPIクロックのレートを設定することが可能です。

次に、図4のようにして遅延クロック方式を実現するケースについて考えます。その場合、アイソレータを使用して、少なくとも1つの高速チャンネルを追加する必要があります。その場合も、SPIのスループットはクロックのチャンネルとデータのチャンネルの間のミスマッチと歪みに依存します。タイミングはすべてのチャンネルでほぼ同じであることから、SPIクロックの半周期は次の式で表されます。

これを計算すると25ナノ秒になります。つまり、クロックの最高レートは20MHzです。

多くのアプリケーションにおいて、MCU/FPGAはADCのシフト・レジスタから出力されたデータを受け取るだけで、シフト・レジスタから外部にデータを受け渡すことはありません。このような3線式のSPIバスについては、逆方向のチャンネルを2つ備えた4チャンネルのデジタル・アイソレータを1個使用するだけで、バスと遅延クロックの両方に対応することができます。それだけでなく、副次的なメリットも得られます。まず、SPIクロックの半周期分は以下のような式で表されます。

これを計算すると20ナノ秒になります。つまり、クロックの最高レートは25MHzです。

デジタル・アイソレータは、速度とスキューの面ではフォトカプラよりもはるかに優れています。しかし、チャンネル間のタイミング・スキューと歪みによって、やはりSPIクロックの最高レートは制限されてしまいます。しかも、遅延クロック方式を実現するために追加したアイソレータによって、消費電力は約20~25%増加します。したがって、既存のアイソレータを使用する場合には、消費電力と実装面積が増加するというデメリットを被るのにも関わらず、理論上の最高性能は得られないということです。

遅延クロック方式向けに最適化を図ったデジタル・アイソレータ

アナログ・デバイセズは、遅延クロック方式によって最高の性能が得られるように最適化されたデジタル・アイソレータを開発しました。図6で使用している「ADuM3150」がそうした製品の1つです。これは、SPIsolator™シリーズの高速デジタル・アイソレータであり、SPIバスの最適な絶縁を実現するために設計されました。同製品を採用すれば、アイソレータのチャンネルを追加することなく、遅延クロックDCLKを生成することができます。DCLKは、標準のSPIクロックに、アイソレータにおける往復伝搬遅延(2×tpISO)と同じ分だけの遅延を加えることによって生成されます。図6に示したADuM3150のブロック図を見ると、遅延セルが集積されていることがわかります。この遅延セルは、アイソレータの往復伝搬遅延に応じ、製造時に慎重にトリミングされます。それにより、遅延クロックとスレーブからのデータのタイミング的なミスマッチが最小限に抑えられます。しかも、遅延のミスマッチについては、広範な動作条件にわたって非常に明確に定義されています。データシートでは、DCLKERRというパラメータによって保証値が示されています。

図6. ADuM3150による遅延クロック方式の実装。同ICはSPIsolatorシリーズの製品です。

DCLKERRは、遅延クロックとスレーブ・データの同期がどれだけずれているのかを表す指標です。DCLKERRの符号は、遅延クロックがデータよりも進んでいるのか、それとも遅れているのかを表します。遅延クロックは、マスタ側でスレーブ・データをサンプリングするために使用されます。したがって、遅延クロックはデータよりも進んでいるべきではありません。データに対する遅れは、データを完全に見落としてサンプリングを実施できないという事態にならないレベルであれば、許容することが可能です。ADuM3150のデータシートを見ると、DCLKERRの値は-3ナノ秒~8ナノ秒、PWDは3ナノ秒と記載されています。遅延クロックがデータに対して最も進んでいる場合のDCLKERRとPWDを考慮すると、SPIクロックのレートは次のようになります。

これを計算すると12ナノ秒になります。つまり、約40MHzの最高クロック・レートが得られます。ADuM3150を使用すれば、アイソレータのチャンネルを追加してサイズ、コスト、消費電力を増大させることなく、SPIクロックのレートをここまで高められるということです。

| クロック遅延方式 | tSKEWに影響を及ぼす主要な要因 | SPIの最高速度〔MHz〕 | 備考/コメント |

| シングルチャンネルのフォトカプラ(その1)、tpISOは 40ナノ秒 | PWD:8ナノ秒 tPSK:20ナノ秒 |

6.25 | • 実装面積が大きい • 消費電力が多い • 使用期間を通してタイミング性能が変化 • コストが高い |

| シングルチャンネルのフォトカプラ(その2)、tpISOは 20ナノ秒 | PWD:2ナノ秒 tPSK:16ナノ秒 |

11.75 | • 実装面積が大きい • 消費電力が多い • 高速なフォトカプラは非常に高価 • 使用期間を通して タイミング性能が変化 • コストが非常に高い |

| デジタル・アイソレータ、tpISOは 32ナノ秒 | PWD:2ナノ秒 tPSK:10ナノ秒 tPSKOD:5ナノ秒 |

25 | • 4線式のSPIの場合、 実装面積が中~大 • 消費電力が多い • コストは中程度 |

| 遅延クロックの生成機能を備えるデジタル・アイソレータ、ADuM3150のtpISOは 14ナノ秒 | PWD:3ナノ秒 DCLKERR:3ナノ秒 |

40 | • 実装面積は増加しない • 消費電力は最も少ない • トリミングにより、 tSKEWを最小化 • DCLKERRは明確に 定義されている • コストは最も低い |

まとめ

オーバーサンプリングによってセンサー・アプリケーションにおけるダイナミック・レンジを高めるには、対象とする周波数と比べてサンプリング周波数を十分に高い倍数に設定し、ノイズを強く抑制しなければなりません。本稿で示した遅延クロック方式は、絶縁型のSPIのスループットを高め、サンプル・レートを向上させるための有効な手段です。この手法を適用することにより、あらゆる絶縁技術においてSPIクロックの最高レートを高めることができます。デジタル絶縁技術を採用すれば、シグナル・チェーン内のチャンネル間スキューのような歪みを厳密に制御することが可能になります。それにより、旧来のフォトカプラ技術を使用する場合と比べてはるかに多くのメリットが得られます。アナログ・デバイセズは、SPI専用のアイソレータ製品としてADuM3150を提供しています。この製品では、トリミングなどの最適化手法を導入することにより、遅延クロック方式を更に進化させました。同ICの最大の特徴は、スキューの小さい遅延クロックを生成する機能を備えていることです。それにより、旧来の技術/方式を利用する場合のように消費電力を増加させることなく、遅延クロック方式のメリットを享受できます。具体的には、絶縁型のSPIポートを介して最高40MHzのデータ転送速度を実現することが可能です。そのため、高速なADCと組み合わせれば、最大1MSPSのサンプル・レートを実現できます。アナログ・デバイセズは、SPI専用のデジタル・アイソレータとしてADuM3150のシリーズ製品も開発済みです。例えば、集積度を高めてチャンネル数を増やした「ADuM3151/ADuM3152/ADuM3153」や、複数のスレーブをサポートする「ADuM3154」などを提供しています。