概要

CMOSスイッチの評価指標の1つに、CDS(OFF)というものがあります。これは、スイッチがオフしている際のソース‐ドレイン間の容量値のことです。CMOSスイッチでは、ソース側の信号がドレインにカップリングすることを防がなければなりません。そのような、スイッチをオフする能力を表すのがCDS(OFF)です。この指標は、ソリッドステート・リレー(PhotoMOS®、OptoMOS®、フォトリレー、MOSFETリレーなど)において一般的に使われています。ただ、多くの場合、そうした製品のデータシートでは、出力容量、COUTといった名称が使われています。一方、通常のCMOSスイッチ製品では、この指標が仕様として明記されることはありません。ただ、同様の性能を表すものとして、オフ・アイソレーションという指標が使われています。オフ・アイソレーションでは、オフしているスイッチにおいて、ソース信号の成分がどの程度ドレインに現れるのかを数値化して表します。本稿では、CMOSスイッチのオフ・アイソレーションの値から、CDS(OFF)の値を導き出す方法を紹介します。その上で、この指標を利用して、ソリッドステート・リレーとCMOSスイッチの性能をより的確に比較する方法を示します。ソリッドステート・リレーは多くのアプリケーションにおいて、DC信号や高速AC信号のスイッチングに使用されます。ただ、実際には、CMOSスイッチでそうした機能を実現できるケースも少なくありません。したがって、ソリッドステート・リレーとCMOSスイッチの性能を的確に比較できれば、システムの設計や製品の選択をより適切に行えるようになります。

オフ・アイソレーションとCDS(OFF)の関係

図1に示したのは、CMOSスイッチIC「ADG5412」のオフ・アイソレーション性能です。ご覧のように、ソース側の信号の周波数が高くなるにつれ、オフ・アイソレーション性能は低下していきます。

この特性については、信号の周波数が高くなるにつれ、オフしているスイッチのドレイン側にソース側の信号がより多く現れるようになると表現できます。図2に示したのは、CMOSスイッチのオフ・アイソレーション性能の測定に使用する回路です。スイッチがオフの状態にある場合の等価回路について検討すると、上記のような特性を示す理由を理解できます。スイッチがオープン(オフ)のとき、ソース‐ドレイン間には、図中のCDS(OFF)で示される寄生容量が存在していることになります。この寄生容量を介して高い周波数の信号が通過することから、オフ・アイソレーションの特性は図1のようになるということです。

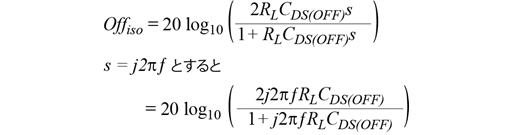

オフ・アイソレーションを測定するには、図2の回路においてVSとVOUTの値を取得します。それらの値を次式に代入することで、同性能を算出できます。

オフ・アイソレーションのプロットとスイッチがオフの際の等価回路を組み合わせれば、CMOSスイッチのCDS(OFF)の値を求められます。まず、スイッチがオフになっている場合のチャンネルと負荷は、図3に示したようなハイパス・フィルタと等価です。

図3に示した回路の伝達関数は、次式のようになります。

次に、図2の回路のソース電圧VSとインピーダンスについて考えてみます。図中に示したとおり、ソース・インピーダンスRSの値は50Ωです。これは50Ωの負荷インピーダンスRLとマッチングしています。理想的なケースとしてCDS(OFF)が短絡している回路を想定すると、両インピーダンスの値が等しいことから、VSはVINの2倍になることがわかります。つまり、VSに関する伝達関数は、上記の伝達関数の2倍になります。

したがって、システム全体の伝達関数は次式のように表されます。

これをオフ・アイソレーションを表す式に代入すると、次式が得られます。

これを整理すると、CDS(OFF)を表す式は以下のようになります。

この式のとおり、CDS(OFF)の値は、RL、入力信号の周波数f、オフ・アイソレーションの値(dB単位)がわかれば求められます。そして、アナログ・デバイセズのスイッチIC/マルチプレクサIC製品の場合、これらの値はデータシートに記載されています。

CDS(OFF)の計算例

ここでは、SPI(Serial Peripheral Interface)による制御が可能なクワッドSPST(単極単投)スイッチ「ADGS1612」を例にとります。同製品のデータシート(の表1)を見ると、オフ・アイソレーション性能は-65dBとなっています。評価条件は、RLが50Ω、信号周波数fが100kHzです。これらの値を使えば、CDS(OFF)の値を以下のようにして求めることができます。

なお、スイッチIC/マルチプレクサICのオフ・アイソレーションの測定に使用する回路については1つ注意が必要です。というのは、図4のようにスイッチのチャンネルのソース・ピンに50Ωの終端抵抗が加えられていることがあるのです。ただ、上に示したCDS(OFF)の式は、オフ・アイソレーションが図4の方法で測定されている場合にも利用できます。その場合、データシートに記載されたオフ・アイソレーションの値に6dBを加えて式に適用します。ソースに付加した50Ωの終端抵抗によって電圧が1/2になる(つまり、-6dB)ので、それを補償するということです。

CMOSスイッチとソリッドステート・リレーの比較

表1は、 ア ナ ロ グ・ デ バ イ セ ズ の 代 表 的 な ス イ ッ チICのC DS(OFF)についてまとめたものです。「ADG54xxファミリ」と「ADG52xxファミリ」は、最大振幅が44Vの信号電圧に対応できます。また、「ADG14xxファミリ」と「ADG12xxファミリ」は、最大振幅が33Vの信号電圧に対応可能です。つまり、これらの製品は、信号範囲が30V/40Vのソリッドステート・リレーに相当するものだと言えます。この表の最後の列に示しているのは、CDS(OFF)とスイッチのオン抵抗RONの積(以下、R×Cと表記します)です。この値も、ソリッドステート・リレーの性能を表すものとして使用されています。R×Cは、スイッチがオンのときの信号の減衰量と、スイッチがオフのときに高速信号を阻止する能力を合わせて示します。表1から、「ADG1412」のR×Cは5未満であることがわかります。この数値は、同ICがソリッドステート・リレーの強力な競合製品になり得ることを示しています。

| 最大電源電圧 | オフ・アイソレーション | CDS(OFF) | オン抵抗 | R × C | |

| ADG5412 | ±22 V, +40 V | −78 dB @ 100 kHz | 4 pF | 9.8 Ω | 39.2 |

| ADG5212 | ±22 V, +40 V | −80 dB @ 1 MHz | 0.32 pF | 160 Ω | 51.2 |

| ADG1412 | ±16.5 V, +16.5 V | −80 dB @ 100 kHz | 3.2 pF | 1.5 Ω | 4.8 |

| ADG1212 | ±16.5 V, +16.5 V | −80 dB @ 1 MHz | 0.32 pF | 120 Ω | 38.4 |

また、ソリッドステート・リレーと比較して、CMOSスイッチには以下のような多くの長所があります。

- スイッチを容易に駆動できる

ソリッドステート・リレーのダイオードを駆動するためには、5mA(推奨値)の順方向電流が必要になります。一方、アナログ・デバイセズが提供する多くのCMOSスイッチの場合、デジタル入力電流は1nA(代表値)です。つまり、CMOSスイッチはマイクロコントローラのGPIO(汎用I/O)によって、直接かつ容易に制御できるということです。

- スイッチング速度が速い

ソリッドステート・リレーのターンオン時間は数百ミリ秒に達します。一方、CMOSスイッチのターンオン時間はわずか100ナノ秒です(ADG1412の代表値)。

- パッケージあたりのスイッチの数が多い

例えば「ADGS1414D」の場合、5mm×4mmのパッケージに8チャンネルのスイッチを搭載しています。つまり、パッケージの面積で換算すると、2.5mm2あたり1個のスイッチを搭載しているということです。各スイッチのオン抵抗は1.5Ω、CDS(OFF)は5pFです。

まとめ

スイッチについては、オフの状態にあるとき、どれだけ信号を阻止できるのかという能力が重要な指標になります。ソリッドステート・リレーでは、スイッチにおける容量の評価基準としてCOFFが用いられます。この容量により、オフの状態にあるスイッチの入力と出力の間に信号のカップリングが生じます。CMOSスイッチでは、これに相当する容量の値が直接測定されることはありません。しかし、オフ・アイソレーションの値を利用すれば、その容量の値を把握することができます。本稿では、オフ・アイソレーションの値、入力信号の周波数、負荷抵抗の値を使用して、オフにした状態のスイッチの伝達関数を示しました。また、その伝達関数を使用することにより、CDS(OFF)の値を算出できることも明らかにしました。CMOSスイッチのCDS(OFF)の値は、ソリッドステート・リレーのCOUTとの比較に使用できます。加えて、CDS(OFF)はR×Cの算出にも使用可能です。R×Cの値は、スイッチ全体のオフ・アイソレーション性能と信号損失性能を示すための指標として使われます。この指標により、アプリケーションで使用するスイッチを選択する際、CMOSスイッチとソリッドステート・リレーを直接比較することが可能になります。更に、CMOSスイッチはソリッドステート・リレーに勝るいくつもの長所を備えています。例えば、スイッチを容易に駆動できる、スイッチング速度が速い、パッケージあたりのスイッチの数が多いといった具合です。