Mixed-Signal Front End (MxFE) Products

高度な設定が可能な広帯域RFサンプリング・トランシーバー

第1世代のミックスド・シグナル・フロントエンド(MxFE™)製品は、RFデータ・コンバータを備えており、通信インフラ、計装、航空宇宙・防衛の業界に従事する現代のシステム設計者に、スケーラブルなソフトウェア定義型無線ソリューションを供与し、最大2.4GHzのチャンネル帯域幅と、最大7.5GHzのダイレクトRFサンプリングおよびRF合成機能を提供します。これにより、システム動作のスペクトル領域がRFからミリ波に移行する際に、また必要な帯域幅がメガヘルツからギガヘルツに移行する際に、必要な帯域幅とシグナル・チェーンの複雑さの増大など、いくつかの複雑な課題を解決できます。

ミックスド・シグナル・フロントエンド:シンプル、スケーラブル、効率的

ミックスド・シグナル・フロントエンドのプラットフォーム製品は、直接RFサンプリング、超広帯域のチャンネル、完全なソフトウェア定義によって課題を解決し、シンプルかつスケーラブルで効率的な、将来を見据えたソリューションを実現します。

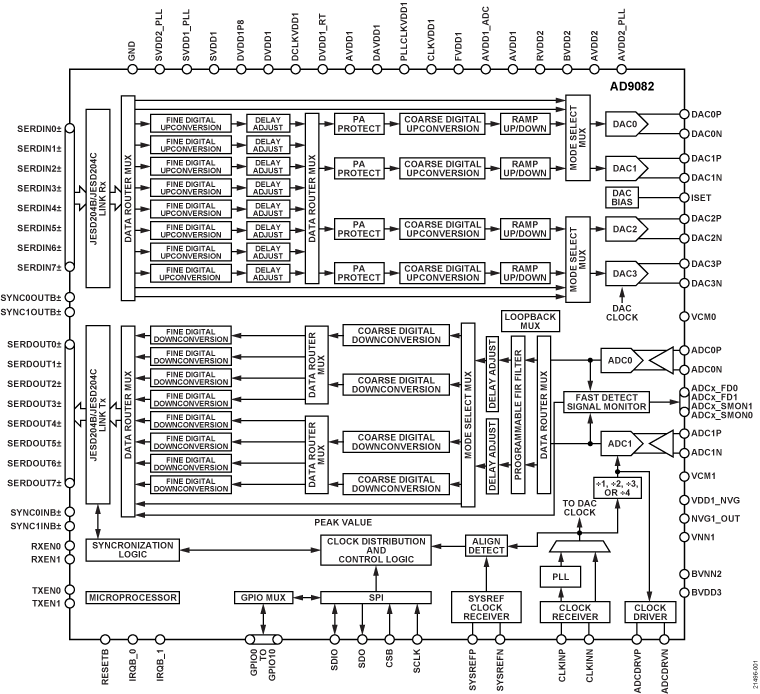

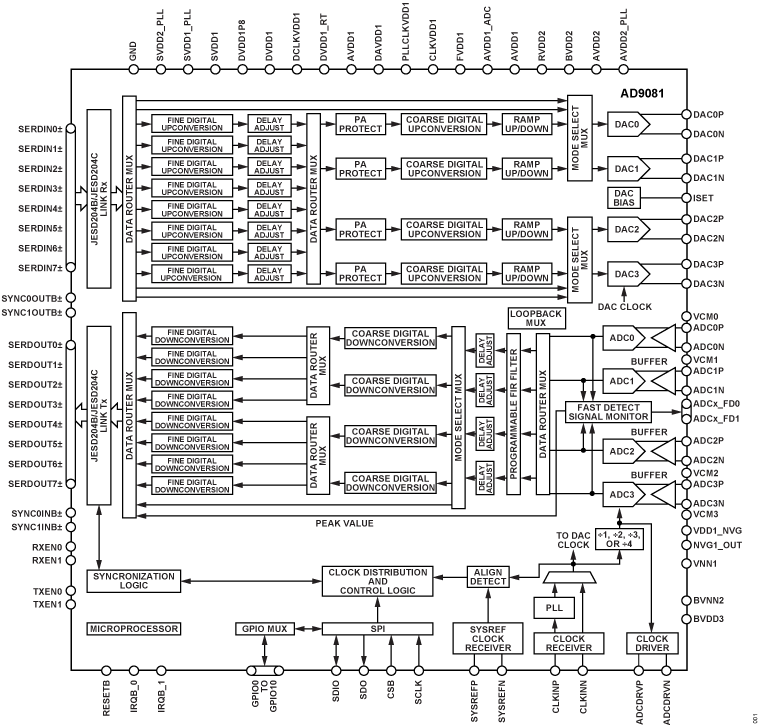

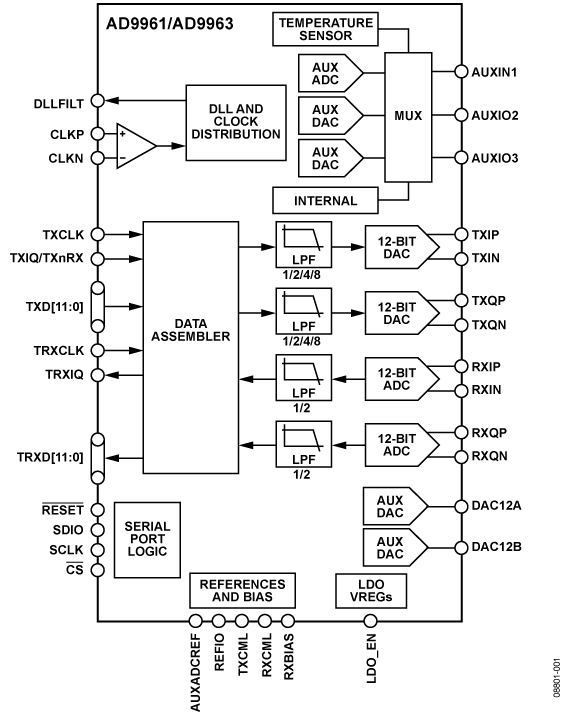

AD9081のブロック図

緑色のブロック:受信パスのプログラマブルFIR(有限インパルス応答)フィルタと粗/細デシメーション・フィルタ、送信パスの粗/細インターポレーション・フィルタを含む、オンチップDSPを示しています。

オレンジ色のブロック:4 GSPSの4つのADCチャンネルと12 GSPSの4つのDACチャンネルを提供するAD9081を示しています。

ミックスド・シグナル・フロントエンドの主な特長と利点

RFサンプリング・コンバータとDSPブロックの統合化

ミックスド・シグナル・フロントエンドは、複数のGSPS ADCおよびDACとオンチップDSPとの組み合わせを統合化し、RFフロント・エンドの簡素化とFPGAの小規模化を可能にして、システム全体のサイズ、複雑さ、重量、消費電力、コストを抑えます。

広帯域幅および高ダイナミック・レンジ

ミックスド・シグナル・フロントエンドは、7.5 GHzのアナログ入力帯域幅、最大4.8 GHzの瞬時帯域幅、-70 dBcのスプリアスフリー・ダイナミック・レンジにより、真の超広帯域性能を実現します。

フル機能のソフトウェア無線ソリューション

ミックスド・シグナル・フロントエンドは、ハードウェア/ソフトウェア共通プラットフォームによって複数の製品開発プログラムに対応する、高度に設定可能なソフトウェア無線プラットフォームです。製品を市場に投入するまでの時間を短縮し、将来を見据えた設計を可能にします。

主な製品

デジタル・シミュレーション・モデル

アナログ・デバイセズのデジタル・シミュレーション・モデルを使用して、設計を迅速にスタートしましょう。これらのシミュレーション・モデルは、DSP性能や周波数の計画、RFフロント・エンドのシグナル ・チェーンの最適化などによって、開発時間を短縮し、より短期間で収益を上げることを可能にします。

MATLABモデル

オンチップDSPの性能、高調波、外部フィルタ処理の必要性をモデル化して、周波数計画案を作成します。

IBIS/AMIモデル

IBISアルゴリズム・モデリング・インターフェース(IBIS-AMI)は、マルチギガビットのシリアル・リンクの高速かつ正確で統計的に有意なシミュレーションを可能にする、SERDES PHYのモデリング標準です。

サーマル・モデル

Delphiモデルは、接合部、ケース、ピンなど、いくつかの重要なポイントでのパッケージの温度を正確に予測します。

Sパラメータ・モデル

散乱(S)パラメータは、ミックスド・シグナル・フロントエンドへのADC入力、DAC出力、クロック・インターフェース入力のマッチング回路のモデル化に使用されます。これにより、目的とする周波数範囲に合わせてRFフロントエンド・シグナル・チェーンを最適化できます。

製品評価

アナログ・デバイセズの評価用キットは、ミックスド・シグナル・フロントエンドの優れた設定機能と性能を簡単に評価するために必要な、すべてのハードウェアおよびソフトウェアを提供します。

評価用ボードの開梱とセットアップ

MxFE®の評価用ボードにヒートシンクを取り付ける方法

MxFE評価用プラットフォームのデモンストレーション・ビデオ・シリーズ

このシリーズは、ACE、DPG Lite、およびアナログ・デバイセズのAPIを使ってMxFEを評価する方法を示す、ステップバイステップのチュートリアルで構成されています。最初のビデオでは、ACEまたはDPG Liteを使ってハードウェアを初期化する方法の概要を説明します。ビデオ2では、ACEを使ってユースケース例を示します。このシリーズの最後の2本のビデオではユースケース例を1つ示し、アナログ・デバイセズのAPIを使ってカスタム・ユースケースを作成しています。

必要なハードウェア

ミックスド・シグナル・フロントエンドを評価するには、ミックスド・シグナル・フロントエンド評価用ボード(製品固有)、およびADS8-V3EBZまたはADS9-V2EBZ FPGAコントローラ・ボードが必要です。これらのボードはFMCを介して簡単に接続し、API/ACEソフトウェア・ツールセットを使用して迅速かつ簡単に起動できます。

ミックスド・シグナル・フロントエンド評価用ボード

FPGAコントローラ・ボード

APIデバイス・ドライバ

アプリケーション・プログラミング・インターフェース(API)のCコード・デバイス・ドライバは、高レベルの関数呼び出しを使用してミックスド・シグナル・フロントエンド評価用ボードを迅速に設定することを可能にします。

JESD204B/JESD204C IPフレームワーク

アナログ・デバイセズのJESD204インターフェース・フレームワークは、システムレベルのソフトウェアです。このHDLパッケージは、様々なFPGAプラットフォームで高速コンバータ、トランシーバー、クロックなどの複雑なハードウェアを統合化する、最適化した性能のIPフレームワークの提供によってシステム開発を簡素化することを目的としています。

プロトタイピング

アナログ・デバイセズとそのアライアンス・メンバーは、迅速な評価とシステムレベルのプロトタイピングを可能にして、より短期間で収益を上げられるように、ミックスド・シグナル・フロントエンドのリファレンス設計を提供しています。

アナログ・デバイセズのシングルMxFE HDLリファレンス設計

AD9081-FMCA-EBZリファレンス設計は、プロセッサベース(例えばMicroBlaze)の組み込みシステムです。この設計は、受信チェーンと送信チェーンで構成されており、Xilinx® FPGAキャリアであるZCU102、ZC706、VCU118に対応します。

クワッドMxFE HDLリファレンス設計

AD-QUADMXFE1-EBZリファレンス設計は、プロセッサベース(例えばMicroBlaze)の組み込みシステムです。この設計は、受信チェーンと送信チェーンで構成されています。

Delphi EngineeringのシングルMxFE FMCモジュール、ADF-QMx44

ADF-QMX44は、VITA 57.1-2019準拠のFPGAメザニン・カード(FMC)です。ADIのAD9081 4T/4R MxFEを利用し、Xilinx UltraScaleおよびUltraScale+ FPGAキャリア・ボードによって業界全体でのプラットフォーム互換性を実現します。これらのキャリア・ボードには、業界をリードする性能を持つDEGのPCI Expressや3U Open VPXなどのキャリア製品が含まれます。

Annapolis MicrowaveのデュアルMxFE WWQM60

この高性能WILD FMC+ QM60 ADCおよびDACでは、4種類の入力帯域幅、内部サンプル・クロック、内部10 MHzリファレンス・クロックを使用できます。このカードをWILDSTAR OpenVPX FPGAメインボードに差し込むと、1個の6U OpenVPXスロットで8個のADCチャンネルと12個のDACチャンネル(3Uの場合は4個のADCチャンネルと6個のDACチャンネル)を使用できます。更にQM60は、12ビット(ADC)および16ビット(DAC)の分解能で、最大6 GSPS(ADC)および12 GSPS(DAC)の速度グレードを実現します。

注目の技術記事

DAC/ADC IC上の統合化された強化DSPによる広帯域マルチチャンネル・システムの改善

システムのFPGAによるリソース消費量を比較すると、マルチチャンネル・プラットフォームの設計者が抱える重要な課題を強化DSPブロックによって解決できることが明らかになります。

マルチオクターブ広帯域デジタル・レシーバーのSFDRに関する考慮事項

今後数年の間に、高サンプル・レートADCおよびDACテクノロジにより、広帯域デジタル・レシーバー・アーキテクチャが進歩すると考えられます。

統合化された広帯域DACおよびADCへのマルチチップ同期の使用

シングル・モノリシック・チップ内での複数のDSPブロック、広帯域DAC、広帯域ADCの統合化によって、消費電力の大きいFPGAリソースのオフロードが可能になっています。