Mixed-Signal Front End (MxFE) Products

Highly Configurable Wideband RF-Sampling Transceivers

The first-gen mixed-signal front end (MxFE™) products, with RF data converters, provide today’s system designers working in communication infrastructure, instrumentation, and aerospace and defense with a scalable software-designed radio solution supporting channel bandwidth as high as 2.4 GHz and direct sampling/synthesis up to 7.5 GHz. This solves several complex challenges including increasing bandwidth demands and signal chain complexity as system operation moves from the RF to the mmWave spectrum domain and as bandwidth demands move from megahertz to gigahertz.

To learn more, check out our press release and the AD9081/AD9082 product pages.

现有MxFE产品组合简单、可扩展、高效

MxFE产品平台通过直接RF采样和非常宽的通道带宽(全部由软件定义)解决各种难题,提供了一个简单、可扩展、高效且经得起未来考验的解决方案。

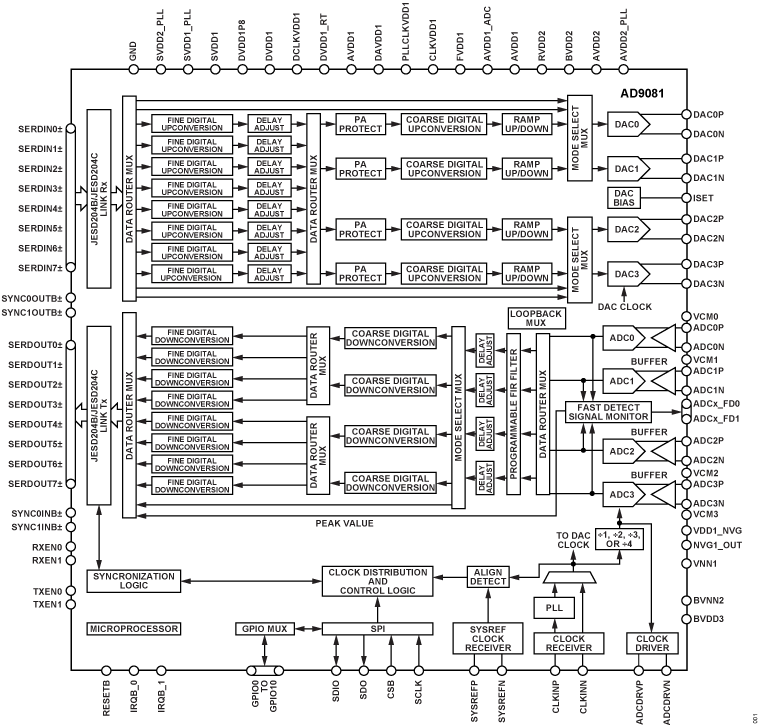

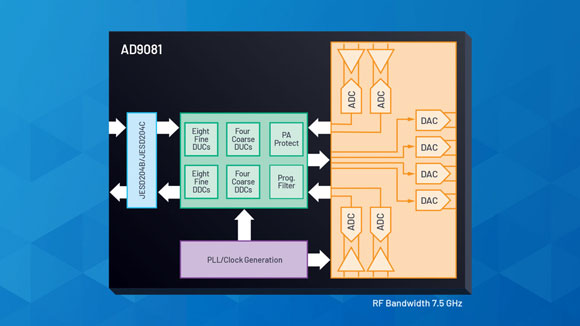

AD9081的方框图

绿色方块:重点介绍片内 DSP,包括接收路径上的可编程 FIR 滤波器和粗/精抽取滤波器,以及发送路径上的粗/精插值滤波器。

橙色方块:显示 AD9081 提供四个 4 GSPS 的 ADC 通道和四个 12 GSPS 的 DAC 通道。

MxFE 的主要特性和优势

RF 采样转换器和 DSP 模块的集成

MxFE 将多个 GSPS ADC 和 DAC 与片内 DSP 相结合,以实现更简单的 RF 前端和更小的 FPGA,从而降低整体系统尺寸、复杂性、重量、功耗和成本。

宽带宽和高动态范围

凭借 7.5 GHz 的模拟输入带宽、高达 4.8 GHz 的瞬时带宽和 -70 dBc 的无杂散动态范围,MxFE 提供了真正的超宽带宽性能。

完整的软件定义射频解决方案

MxFE 是高度可配置的软件定义射频平台,能够通过通用 HW/SW 平台支持多种产品开发计划,缩短上市时间,并使您的设计面向未来。

特色产品

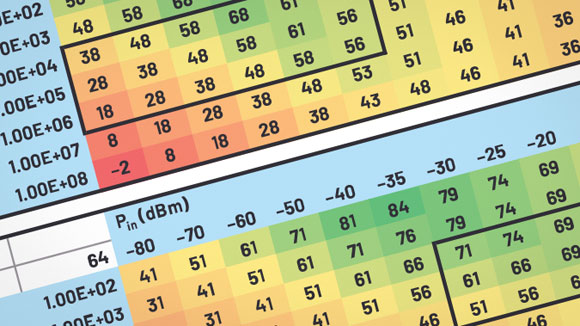

数字仿真模型

使用 ADI 数字仿真模型快速开始您的开发。从 DSP 性能到频率规划,再到优化您的 RF 前端信号链,这些仿真模型将缩短您的开发时间,并加速创收时间。

MATLAB 模式

通过对片内 DSP 的性能、谐波和外部滤波需求进行建模,制定频率计划草案。

IBIS/AMI 模型

IBIS 算法建模接口 (IBIS-AMI) 是 SERDES PHY 的建模标准,可对多千兆位串行链路进行快速、准确、具有统计意义的仿真。

热模型

Delphi 模型可以在多个关键点准确预测封装的温度:连接点、外壳和引线。

S 参数模型

散射 (S) 参数用于为 ADC 输入、DAC 输出和 MxFE 的时钟接口输入的匹配网络建模。这有助于用户优化其射频前端信号链,以适应感兴趣的频率范围。

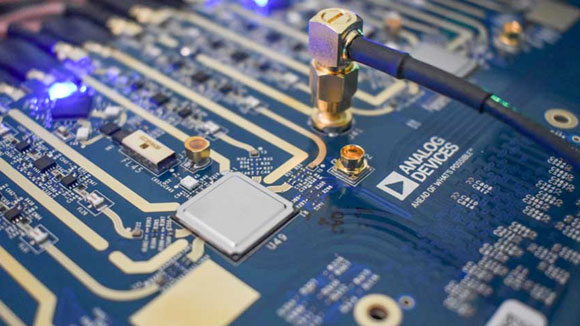

产品评估

ADI 评估套件提供轻松评估 MxFE 令人难以置信的可配置性和性能所需的所有硬件和软件。

拆箱和评估设置

在 MxFE 评估板上安装风扇散热器

MxFE评估平台演示视频系列

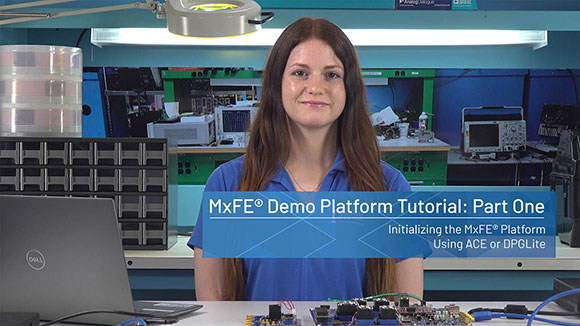

观看本系列视频教程,了解如何使用ACE、DPG Lite和ADI公司的API逐步评估MxFE。四个视频分别为使用ACE或DPG Lite初始化硬件的方法介绍、ACE用例展示、使用场景示例以及使用ADI公司的API创建自定义用例。

硬件要求

要评估 MxFE,您需要 MxFE 评估板(针对特定部件)和 ADS8-V3EBZ 或 ADS9-V2EBZ FPGA 控制器板。这些板可以通过 FMC 轻松连接,并且可以使用我们的 API/ACE 软件工具集快速简单地启动。

MxFE 评估板

FPGA 控制器板

JESD204B/JESD204C IP 框架

ADI 公司的 JESD204 接口框架是一款系统级软件和 HDL 软件包,旨在通过提供性能优化的 IP 框架来简化系统开发,该框架将高速转换器、收发器和时钟等复杂硬件与各种 FPGA 平台集成在一起。

原型

ADI 公司和我们的联盟成员提供 MxFE 参考设计,以实现快速评估和系统级原型设计,从而显着缩短创收时间。

ADI 公司的单 MxFE HDL 参考设计

AD9081-FMCA-EBZ 参考设计是基于处理器(例如 MicroBlaze)的嵌入式系统。该设计由一个接收链和一个发送链组成,并支持以下 Xilinx® FPGA 载体:ZCU102、UVM 和 VCU118。

德尔福工程单 MxFE FMC 模块 ADF-QMx44

ADF-QMX44 是符合 VITA 57.1-2019 的 FPGA 夹层卡 (FMC),它利用 ADI 的 AD9081 4T/4R MxFE 并提供与 Xilinx UltraScale 和 UltraScale+ FPGA 载板的全行业平台兼容性,包括 DEG 性能领先的 PCI Express 和 3U Open VPX 载体产品。

安纳波利斯微波双 MxFE WWQM60

这种高性能 WILD FMC+ QM60 ADC 和 DAC 具有四个输入带宽选项、内部采样时钟选项和内部 10 MHz 参考时钟选项。当插入 WILDSTAR OpenVPX FPGA 主板时,该卡允许在一个 6U OpenVPX 插槽(或 3U 插槽中有 4 个 ADC 和 6 个 DAC 通道)中使用 8 个 ADC 和 12 个 DAC 通道。QM60 还具有高达 6 GSPS (ADC) 和 12 GSPS (DAC) 的速度等级,分辨率为 12 位 (ADC) 和 16 位 (DAC)。

特色技术文章

DAC/ADC IC 上的集成强化 DSP 改进了宽带多通道系统

在比较系统 FPGA 的资源利用率时,很明显,硬化的 DSP 模块解决了多通道平台设计人员面临的重大挑战。

多倍频程宽带数字接收器中的 SFDR 考虑

未来几年,高采样率模数转换器 (ADC) 和数模转换器 (DAC) 技术将引领宽带数字接收器架构的演进。

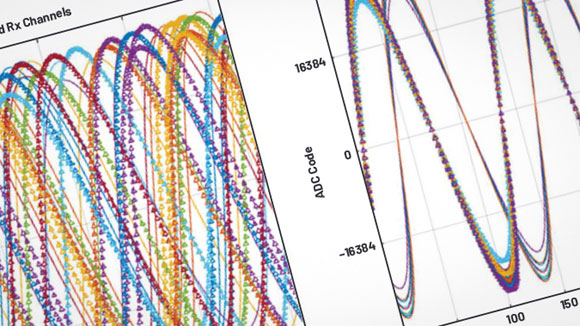

在集成宽带 DAC 和 ADC 中使用多芯片同步

在单个单片芯片中集成多个 DSP 模块、宽带 DAC 和宽带 ADC,现在可以卸载耗电的 FPGA 资源。