AD9645

推荐用于新设计双通道、14位、80 MSPS/125 MSPS串行LVDS 1.8 V模数转换器

- 产品模型

- 6

概述

- 1.8 V电源供电

- 低功耗:每通道122 mW(125 MSPS),功率选项可调整

- SNR = 74 dBFS(至Nyquist频率);无杂散动态范围(SFDR):91 dBc (70 MHz)

- 微分非线性(DNL)= ±0.65 LSB(典型值);积分非线性(INL):±1.5 LSB(典型值)

- 串行LVDS(ANSI-644,默认)、低功耗,缩小范围选项(类似于IEEE 1596.3)

- 650 MHz全功率模拟带宽

- 2 V p-p输入电压范围

- 串行端口控制

- 全芯片及单一通道省电模式

- 灵活的位定向

- 生成内置及用户自定义数字测试码

- 时钟分频器

- 可编程输出时钟与数据对准

- 可编程输出分辨率

- 待机模式

- 通过AEC-Q100汽车应用认证

AD9645是一款双通道、14位、80 MSPS/125 MSPS模数转换器(ADC),内置片内采样保持电路,专门针对低成本、低功耗、小尺寸和易用性而设计。该产品的转换速率最高可达125 MSPS,具有杰出的动态性能与低功耗特性,对小封装尺寸的应用很有意义。

该ADC要求采用1.8 V单电源供电以及LVPECL/CMOS/LVDS兼容型采样速率时钟信号,以便充分发挥其工作性能。对于大多数应用来说,无需外部基准电压源或驱动器件。

为获得合适的LVDS串行数据速率,该ADC会自动倍乘采样速率时钟。它提供一个数据时钟输出(DCO)用于在输出端捕获数据,以及一个帧时钟输出(FCO)用于发送新输出字节信号。它还支持各通道单独进入省电状态,完全掉电模式下的典型功耗低于2 mW。该ADC提供多种功能特性,可使器件的灵活性达到最佳、系统成本最低,例如可编程输出时钟与数据对准、生成数字测试码等。可获得的数字测试码包括内置固定码和伪随机码,以及通过串行端口接口(SPI)输入的用户自定义测试码。

AD9645采用符合RoHS标准的32引脚LFCSP封装,额定温度范围为−40°C至+85°C工业温度范围。该产品受美国专利保护。

产品特色

- 小尺寸。一个节省空间的小型封装中集成两个ADC。

- 低功耗。每通道122 mW(125 MSPS,功率选项可调整)。

- 与AD9635(双通道12位ADC)引脚兼容。

- 易于使用。数据时钟输出(DCO)的工作频率高达500 MHz,支持双倍数据速率(DDR)操作。

- 使用灵活。SPI控制提供丰富灵活的特性,可满足各种特定系统的需求。

应用

- 通信

- 分集无线电系统

- 多模式数字接收器

- GSM、EDGE、W-CDMA、LTE、CDMA2000、WiMAX、TD-SCDMA

- I/Q解调系统

- 智能天线系统

- 宽带数据应用

- 电池供电仪表

- 手持式示波器

- 便携式医疗成像和超声设备

- 雷达/LIDAR

参考资料

数据手册 1

用户手册 1

应用笔记 10

技术文章 1

ADI 始终高度重视提供符合最高质量和可靠性水平的产品。我们通过将质量和可靠性检查纳入产品和工艺设计的各个范围以及制造过程来实现这一目标。出货产品的“零缺陷”始终是我们的目标。查看我们的质量和可靠性计划和认证以了解更多信息。

| 产品型号 | 引脚/封装图-中文版 | 文档 | CAD 符号,脚注和 3D模型 |

|---|---|---|---|

| AD9645BCPZ-125 | 32-Lead LFCSP (5mm x 5mm x 0.75mm w/ EP) | ||

| AD9645BCPZ-80 | 32-Lead LFCSP (5mm x 5mm x 0.75mm w/ EP) | ||

| AD9645BCPZRL7-125 | 32-Lead LFCSP (5mm x 5mm x 0.75mm w/ EP) | ||

| AD9645BCPZRL7-80 | 32-Lead LFCSP (5mm x 5mm x 0.75mm w/ EP) | ||

| AD9645WBCPZ-80 | 32-Lead LFCSP (5mm x 5mm x 0.75mm w/ EP) | ||

| AD9645WBCPZRL7-80 | 32-Lead LFCSP (5mm x 5mm x 0.75mm w/ EP) |

| 产品型号 | 产品生命周期 | PCN |

|---|---|---|

|

2月 1, 2024 - 24_0009 Qualification of alternative Wafer Fab for TSMC 0.18um Mixed Signal CMOS Process |

||

| AD9645BCPZ-125 | 量产 | |

| AD9645BCPZ-80 | 量产 | |

| AD9645BCPZRL7-125 | 量产 | |

| AD9645BCPZRL7-80 | 量产 | |

|

5月 11, 2014 - 13_0231 Assembly Transfer of Select 4x4 and 5x5mm LFCSP Products to STATS ChipPAC China. |

||

| AD9645BCPZ-125 | 量产 | |

| AD9645BCPZ-80 | 量产 | |

| AD9645BCPZRL7-125 | 量产 | |

| AD9645BCPZRL7-80 | 量产 | |

|

9月 15, 2025 - 24_0009 Qualification of Alternative Wafer Fab for TSMC 0.18um Mixed Signal CMOS Process |

||

| AD9645WBCPZ-80 | 量产 | |

| AD9645WBCPZRL7-80 | 量产 | |

这是最新版本的数据手册

软件资源

找不到您所需的软件或驱动?

申请驱动/软件硬件生态系统

| 部分模型 | 产品周期 | 描述 |

|---|---|---|

| 差分放大器 3 | ||

| ADA4927-2 | 推荐用于新设计 | 超低失真电流反馈型ADC驱动器 |

| ADA4938-2 | 推荐用于新设计 | 超低失真差分ADC驱动器(双通道) |

| ADL5562 | 推荐用于新设计 | 2.6GHz 超低失真RF/IF差分放大器 |

| 可变增益放大器(VGA) 2 | ||

| ADL5202 | 过期 | 宽动态范围、高速、数字控制VGA |

| AD8376 | 推荐用于新设计 | 超低失真IF双通道VGA |

| 时钟IC 9 | ||

| AD9510 | 推荐用于新设计 | 1.2 GHz时钟分配IC,PLL内核,分频器,延迟调整,8路输出 |

| AD9511 | 推荐用于新设计 | 1.2 GHz时钟分配IC,PLL内核,分频器,延迟调整,5路输出 |

| AD9512 | 推荐用于新设计 | 1.2 GHz时钟分配IC、2路1.6 GHz输入、分频器、延迟调整、5路输出 |

| AD9513 | 推荐用于新设计 | 800 MHz时钟分配IC,分频器,延迟调整,三路输出 |

| AD9514 | 推荐用于新设计 | 1.6 GHz时钟分配IC、分频器、延迟调整、3路输出 |

| AD9515 | 推荐用于新设计 | 1.6 GHz时钟分配IC,分频器,延迟调整,两路输出 |

| AD9523 | 不推荐用于新设计 | 14路输出、低抖动时钟发生器 |

| AD9523-1 | 推荐用于新设计 | 低抖动时钟发生器,提供14路LVPECL/LVDS/HSTL输出或29路LVCMOS输出 |

| AD9524 | 不推荐用于新设计 | 6路输出、双环路时钟发生器 |

工具及仿真模型

Virtual Eval - BETA

Virtual Eval是一款网络应用程序,可帮助设计人员评估ADC和DAC产品。 利用ADI公司服务器上的详细模型,Virtual Eval在几秒内可仿真关键部件的性能特征。 对工作条件(如输入音和外部抖动)以及器件特性(如增益或数字下变频)进行配置。 性能特征包括噪声、失真和分辨率、FFT、时序图、频率响应图等。

打开工具AD9645 IBIS Model 1

Visual Analog

对于正在选择或评估高速ADC的设计工程师,VisualAnalog™是一个将一组功能强大的仿真和数据分析工具与一个用户友好的图形界面集成在一起的软件包。

打开工具S-参数 1

AD9645 Simulink ADIsimADC Model

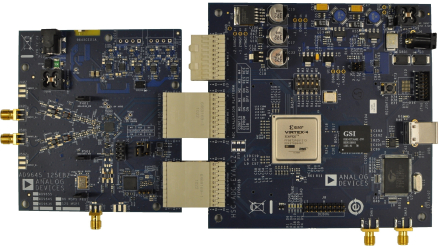

打开工具评估套件

最新评论

需要发起讨论吗? 没有关于 AD9645的相关讨论?是否需要发起讨论?

在EngineerZone®上发起讨论