概要

設計リソース

設計/統合ファイル

- Schematic

- Bill of materials

- Gerber files

- Allegro layout files

- Assembly drawing

評価用ボード

型番に"Z"が付いているものは、RoHS対応製品です。 本回路の評価には以下の評価用ボードが必要です。

- EVAL-CN0393-FMCZ ($269.35) EVAL-CN0393-FMCZ

- EVAL-SDP-CH1Z ($458.85) Eval Control Board

デバイス・ドライバ

コンポーネントのデジタル・インターフェースとを介して通信するために使用されるCコードやFPGAコードなどのソフトウェアです。

機能と利点

- 2 チャンネル、16 ビット 500 kSPS 同時サンプリング

- バンク絶縁型

- フル機能のデータ・アクイジション・システム

製品カテゴリ

マーケット & テクノロジー

使用されている製品

参考資料

回路機能とその特長

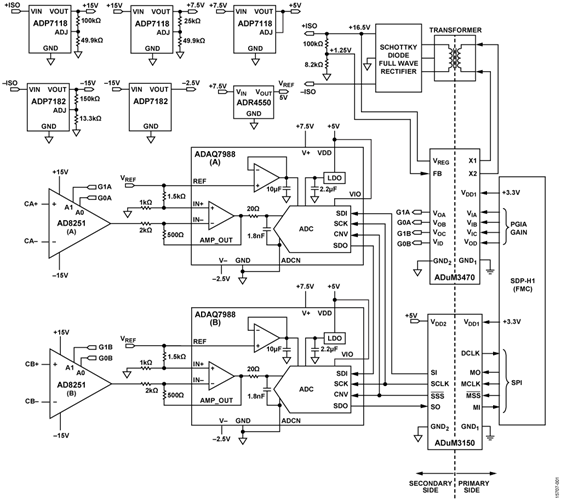

図 1 に示す回路は、2 チャンネル、バンク絶縁型の広帯域データ・アクイジション(DAQ)システムで、各チャンネルに A/Dコンバータ(ADC)を使用する同時サンプリング・アーキテクチャを採用しています。このシステムは、バンクとデジタル・バックプレーンとの間に絶縁を施し、高いチャンネル密度を実現し、比類のない性能を提供します。さらに、この設計ではADC をデイジーチェーン・モードで構成し、調整済みの遅延クロック機能を持つアイソレータ製品を使用することで、絶縁チャンネルを有効に活用しています。電源部も簡素化され、パルス幅変調(PWM)コントローラとトランス・ドライバを内蔵したアイソレータを使用して、絶縁障壁間での DC/DC 変換を行います。さらに、システムには入力回路保護、プログラマブル・ゲイン・チャンネル、高精度、高性能といった、代表的な DAQシグナル・チェーンが標準で有する多くの特長を備えています。

同時サンプリングによって、マルチプレクス DAQ シグナル・チェーン固有のサンプリング・レートの制限を受けずに、多チャンネルを実現できます。システムのセトリング性能条件がそれほど厳しくないため、アナログ・フロント・エンド(AFE)の設計もマルチプレクス・オプションよりも簡素化されます。シーケンシャルなサンプリングシステムではチャンネル間で遅延があるのに対し、このシステムではサンプリングは各チャンネルで同時に行われます。

デジタル・バンク絶縁型の DAQ 設計により、デジタル・バック・エンド回路が保護され、バンク間のグラウンド・ループおよびコモンモード干渉が低減されます。これらの機能によって、グラウンド・プレーンあたりのマルチプレクス DAQ シグナル・チェーンが可能となり、チャンネルごとに絶縁化するシステムに比べ、デジタルの絶縁デバイスの数を少なくすることができます。

回路説明

図 1 に示すシステムには、バンク絶縁型で同時サンプリングのデータ・アクイジション・チャンネルが 2 チャンネルあり、各チャンネルでは 16 ビット、500 kSPS の A/D 変換サブシステムである ADAQ7988 が使用されています。ADAQ7988 は、比類のない性能を持つとともに、ボード面積を縮小し、データ・アクイジション・シグナル・チェーンに関する多くの設計課題を平易化します。

ADuM3470 および ADuM3150 のデジタル・アイソレータにより、図 1 に示す回路の 2 つの電源プレーンが分離されます。この 2 つの電源プレーンは 一次(デジタル)側、二次(データ・アクイジション)側と呼ばれます。デジタル・ホスト(マスター)は FMC コネクタを介して一次側に接続されます。一次側にはデジタル・ホストとの間で行き来するデジタル信号が含まれます。二次側では、データ・アクイジション・シグナル・チェーン、パワー・レギュレータ、リファレンス回路、ADAQ7988 のデジタル・インターフェース信号などを実装しています。

ADAQ7988 に内蔵の ADC 用ドライバは、外付けの整合抵抗ネットワークを使用して最大 ±10 V の工業用レベルの信号に適応するように構成されています。チャンネルごとに AD8251 プログラマブル・ゲイン計装アンプ(PGIA)を備えており、高インピーダンス入力が可能で、±10 V、±5 V、±2.5 V、±1.25 V の入力範囲に対応するチャンネル・ゲイン・オプションがあります。

AD8251 デバイスのゲイン設定と ADAQ7988 デバイスのデジタル・インターフェースは、それぞれ ADuM3470 アイソレータと ADuM3150 アイソレータに接続しています。ADuM3470 は統合化された PWM コントローラとトランス・ドライバを介してデータ・アクイジション・チャンネル・コンポーネントに電力を供給します。ADuM3150 では遅延クロック機能が使用され、高速の絶縁チャンネルが高データレートで効率的に使用できます。ADAQ7988 のデイジーチェーン・モードを併用した場合、ADuM3150 の遅延クロック出力は、わずか 3 つのデジタル・絶縁チャンネルを使用するだけで、最大 40 MHz のシリアル・クロック・レートが可能となります。

図 1 に示す回路とのインターフェースを簡素化する評価用ソフトウェアが提供されています。このソフトウェアには様々な回路パラメータや設定を制御するグラフィカル・ユーザー・インターフェース(GUI)が含まれており、SDP-H1 基板上の FPGA と通信を行います。ソフトウェアの入手に関する詳細は、回路の評価とテストのセクションを参照してください。

部品の選択

ADAQ7988 は、様々なアプリケーションに対応するシステム・イン・パッケージ(SiP)のデザインに、4 つの共通信号処理および調整ブロックを統合した、16 ビット、500 kSPS の ADC サブシステムです。また ADAQ7988 は非常に重要な受動部品を内蔵し、逐次比較レジスタ(SAR)ADC を用いる従来のシグナル・チェーンに伴う多くの設計課題に対処します。内蔵の受動部品は、仕様規定されているデバイスの性能を実現するのに不可欠なものです。

ADAQ7988 はアナログ・デバイセズの能動部品ソリューションの一部で、高精度低消費電力の 16 ビット SAR ADC、低消費電力広帯域の ADC ドライバ、広帯域ノイズ RC フィルタ、低消費電力で安定なリファレンス・バッファ、10 μF のリファレンス・デカップリング・キャパシタ、効率的なパワー・マネージメント・ブロックなどで構成されており、全体が微細な 5 mm × 4 mm の LGA パッケージに実装されています。この統合によって、設計の複雑さが緩和され、同様のものを個別の部品で設計した場合に比べ、PCB 面積を最大 50 % 節約できます。また ADAQ7988 は、広範なアプリケーションに適用できる高度な柔軟性を備えており、例えば、内蔵の ADC 用ドライバは様々な設定やゲインの下で動作可能で、複数の入力範囲に対応することができます。

ADAQ7988 の SPI 互換シリアル・インターフェースは、複数のデバイスを単一の 3 線式バスでデイジーチェーン接続する機能を備えています。これは、絶縁アプリケーションには理想的です。デバイスとデジタル・ホスト間の通信に必要なアイソレータ・チャンネルの数を抑制できるためです。

AD8251 はゲインをデジタル的にプログラムできる計装アンプです。ギガ・オーム(GΩ)の入力インピーダンス、低出力ノイズ、広帯域(10 MHz)、低歪みが特長です。これらの特長により、AD8251 は広帯域データ・アクイジション・アプリケーションの有力候補の 1 つとなっています。AD8251 の高い入力インピーダンスにより、様々なセンサーとインターフェース接続が可能となり、また、入力源と ADAQ7988 内蔵のADC ドライバ間でインピーダンスの変換を行うことができます。アドレス・ピンを経由してゲインを 1、2、4、8 に設定でき、それらをADuM3470 のデジタル・アイソレータ・チャンネルを介してデジタル・ホストで制御可能です。

ADR4550 は高精度、低消費電力、低ノイズの 5 V の電圧リファレンスで、±0.02 % の最大初期誤差、優れた温度安定性、低ノイズ出力が特長です。ADR4550 は、2 つの ADAQ7988 の内蔵リファレンス・バッファに 5 V のリファレンス電圧を供給します。このリファレンス電圧は高精度抵抗ネットワークによって分圧され、ADAQ7988 の ADC ドライバに DC バイアス(レベル・シフト)を供給します。

ADuM3470 は、クワッド・チャンネル・デジタル・アイソレータで、絶縁型 DC/DC コンバータのための PWM コントローラとトランス・ドライバを内蔵しています。アナログ・デバイセズの iCoupler® 技術に基づくこの DC/DC コンバータは、3.3 V ~ 5.0 V の入力電源を使用して、最大電力 2 W、出力電圧 3.3 V ~ 24 V の安定化絶縁型電源を提供します。このデバイスを使用することにより、2 W の絶縁設計では、絶縁型 DC/DC コンバータを個別に用意する必要がなくなります。ロジック信号は iCoupler チップスケール・トランス技術を使って絶縁されています。また、内蔵トランス・ドライバと、絶縁した 2 次側制御回路により、さらに高効率の絶縁型 DC/DC コンバータが実現します。ADuM3470 の定格絶縁電圧は 2500 V rms で、小型のトータル絶縁ソリューションとなっています。

ADuM3150 は 6 チャンネルの SPIsolator™ デジタル・アイソレータで、絶縁型シリアル・ペリフェラル・インターフェース(SPI)用に最適化されています。アナログ・デバイセズの iCoupler® チップスケール・トランス技術に基づき、CLK、MO/SI、MI/SO および SS の伝搬遅延が小さく、SPI バス・シグナルは 14 ns 伝搬遅延、1 ns のジッターで動作し、SPI のタイミングに最適なものとなっています。また ADuM3150 はデバイスのマスター側への遅延クロック出力機能も備えています。この出力は、マスター側の追加のクロックポートで用いられ、40 MHz のクロック性能を導くことが可能です。ADuM3150 の定格絶縁電圧は 3750 V rms です。

システムの二次側のパワー・マネージメントは、ADP7118 および ADP7182 の低ドロップアウト(LDO)リニア電圧レギュレータで行われます。システムの正側レールにおいて、ADP7118 デバイスを直列接続することで、ADuM3470 が供給する正側レールを安定化しています。ボードの ADP7182 デバイスは負側レールについて同じ働きをします。詳細については、配電のセクションを参照してください。

アナログ・フロント・エンド

システムのアナログ・フロント・エンド(AFE)は入力保護ダイオード、AD8251 PGIA、ADAQ7988 DAQ サブシステム、および ADAQ7988 の ADC ドライバを設定するために用いる高精度の抵抗ネットワークから成っています。両チャンネルの AFE の設計は同一ですが、入力範囲はそれぞれの AD8251 のゲイン設定によって独立して定めることができます。図 2 に、AFE の簡略化した回路図を示します。

図 1 に示した回路の各チャンネルについてのフル・システムの理想的な伝達関数(入力電圧から出力コードまで)は、次式で表せます。

ここで

vIN はチャンネルの入力電圧。

GAD8251 は AD8251 のゲイン設定値。

VREF は ADR4550 が供給するリファレンス電圧。

NOUT は ADAQ7988 の結果として得られる出力コード。

RG, RF, R1, R2 は、図 2 に示す受動部品。

AD8251 のゲインは、プログラムによって 1、2、4、8 のいずれかに設定できます。このゲインの幅と ADAQ7988 の ADC 用ドライバの設定により、各チャンネルの入力範囲を ±10 V、±5V、±2.5 V、±1.25 V に構成できます。

ADAQ7988 に内蔵の SAR ADC の入力範囲は 0 V ~ VREF(リファレンス・ソースにより設定)です。図 1 に示す回路では、単一の ADR4550 が両方の ADAQ7988 デバイスの内蔵リファレンス・バッファに 5 V(図 2 では VREF と表示)を供給します。このため、内蔵 ADC 用ドライバの許容出力範囲は 0 V ~ 5 V となります。

ADC 用ドライバは、レベル・シフト構成を持つ反転回路で、最大 ±10 V のバイポーラ入力信号に適合するよう設計されています。この構成によって、ADC の入力端でバイポーラの入力信号をユニポーラ信号に変換できるようになります。この構成でのADC 用ドライバの伝達関数は次式で表せます。

ここで

vAMP_OUT は ADAQ7988 に内蔵された ADC 用ドライバの出力。

vAD8251 は AD8251 の出力信号。

VREF は ADR4550 が供給するリファレンス電圧。

RF は 500 Ω(図 2 参照)。

RG は 2 kΩ(図 2 参照)。

R1 は 1.5 kΩ(図 2 参照)。

R2 は 1 kΩ(図 2 参照)。

レベル・シフト構成を持つ反転回路とすることで、ADAQ7988のユニポーラ ADC を大きなバイポーラ入力信号のアプリケーションで使用できるようになります。シグナル・ゲインは RF とRG で設定され、VREF を超える入力範囲が可能となります。レベル・シフト回路は、ADC 用ドライバの出力端で VREF/2 に等しいDC バイアスを生成し、これによって、バイポーラ入力信号がユニポーラの出力信号に変換され ADC の入力に適合させることができます。レベル・シフト電圧は ADC 用ドライバの非反転ノードに供給され、このためアンプの非反転ゲイン分だけ増幅されます。

RG と RF の比率は 4 : 1 で、これにより ADAQ7988 に 20 V p-pの振幅が入力可能となります。ADC 用ドライバの出力の DC バイアスを VREF/2(2.5 V)に設定するために、R1 と R2 の比を 3 :2 にしています。これら 4 つの抵抗全てが高精度整合抵抗ネットワークを用いて形成されており、システムの不正確さと温度ドリフトを低減します(システム精度解析のセクション参照)。これらの抵抗値は、シグナル・チェーンに影響を及ぼすノイズを最小化するとともに、AD8251 と ADC 用ドライバに必要な出力電流を制限するよう選択されています(システム精度解析のセクション参照)。この部品選択によって、システムの伝達関数は次式のようになります。

したがって、システムのゲイン範囲は、−0.25、−0.5、−1、−2 となります(GAD8251 が 1、2、4、8 の値をとり得るため)。

ADC 用ドライバは反転構成であるため、ADAQ7988 の出力コードは入力電圧に対して反転することに注意が必要です。正のフルスケール入力電圧に対して、理想的な出力コードは ADC のゼロ・スケールとなり、出力コードは入力電圧とは逆方向に向かいます。

リファレンス・ソースを用いて ADAQ7988 の ADC 用ドライバの非反転入力へのレベル・シフト電圧を生成しているので、システムは VREF の偏差の影響を受けません。vIN が 0 V の場合、システムの 1 チャンネルの伝達関数は次式のようになります。

この式から ADAQ7988 の出力コードは VREF の値とは無関係でしかし、この一般化では ADAQ7988 に内蔵のリファレンス・バッファのオフセット誤差は無視できると仮定されていることに注意が必要です。リファレンス・バッファのオフセットがADAQ7988 に仕様規定されている最大値であった場合でも、出力コードの偏差は 1 LSB(コード値)未満にすぎないため、この仮定は適切です。あることが分かります。

システムのノイズ解析

データ・アクイジション・システムの設計上で鍵となる考慮事項の 1 つは、システムのノイズの影響を抑制することです。AFEのノイズによって、システムの実効分解能(ノイズ・フリーのビット)と、S/N 比(SNR)などの AC 性能指標が制限されます。このセクションでは図 1 に示す回路で使用したノイズ解析法を説明します。

システムに存在する全ノイズ・パワーは、ADAQ7988 に内蔵のADC の入力を基準として、個々の部品が関与するノイズ・パワーの二乗和平方根(rss)をとることで予測することができます。

ここで

vn,TOTAL は全システム・ノイズ。

vn,R は抵抗に起因するノイズ。

vn,AD8251 は AD8251 に起因するノイズ。

vn,ADC DRIVER は ADAQ7988 に内蔵された ADC 用ドライバが関与するノイズ。

vn,ADC は ADAQ7988 に内蔵された ADC が関与するノイズ。

これより、システムの 予想される SNR は次式を用いて計算できます。

ADAQ7988 には、ADC 用ドライバと ADC 入力との間にローパス RC フィルタが設けられています。この RC フィルタは、ADC の入力部での帯域外のノイズの量を抑制するように作用し、同時に、ADC のスイッチド・キャパシタ入力に伴う電圧ステップを減衰させるのに役立ちます。このフィルタの帯域幅は、周辺部品からの広帯域ノイズをできるだけ除去しながらも、変換の間の ADC 入力信号を十分に安定化できるように選択されています(詳細については、アナログ・ダイアログの記事、SiP を採用したデータ・アクイジション用 IC、高精度のシグナル・チェーンの実装密度を向上、を参照してください)。

RC フィルタの構成部品は、20 Ω の抵抗と 1.8 nF のキャパシタで、4.42 MHz の帯域幅(BWRC)を生成しています。実効的なノイズ帯域幅(ENBWRC)は次式で計算でき、約 2635 √Hz となります。

この ENBWRC は、ADC の入力を基準として、個々の部品が関与する rms ノイズを計算するために使用されています。

このシステムの主要な各ノイズ源について、ノイズ解析した計算結果を表 1 に示します。

| Gain3 (V/V) | AD8251 | ADAQ7988 | Resistors | System Total | ||||

| en,AD8251 (nV/√Hz) |

vn,AD8251 (μV rms) |

en,ADC DRIVER (nV/√Hz) |

vn,ADC DRIVER (μV rms) |

vn,ADC (μV rms) |

vn,R (μV rms) |

vn,TOTAL (μV rms) |

SNR Expected (dB) |

|

| −0.25 | 40 | 26.53 | 5.2 | 17.13 | 47.0 | 13.43 | 58.19 | 89.65 |

| −0.5 | 27 | 35.82 | 5.2 | 17.13 | 47.0 | 13.43 | 62.98 | 88.96 |

| −1 | 22 | 58.37 | 5.2 | 17.13 | 47.0 | 13.43 | 78.04 | 87.10 |

| −2 | 18 | 95.52 | 5.2 | 17.13 | 47.0 | 13.43 | 108.66 | 84.23 |

| 1 rms ノイズの計算値は全て、ADAQ7988 内蔵の ADC の入力を基準としています。 2 2T = 300 K で計算。 3 このゲインは全システムのゲインを示します。AD8251 のゲインの 1、2、4、8 に対応します。 |

||||||||

AD8251 が関与するノイズ

AD8251 が関与する rms ノイズは、入力換算の電圧ノイズ(eAD8251)、ゲイン設定値(GAD8251)、ADAQ7988 の ADC 用ドライバのシグナル・ゲイン(図 2 の RF と RG で設定)、およびENBWRC の関数です。

eAD8251 には最大仕様値が与えられ、4 つのゲイン設定値のいずれとも異なることに注意が必要です。実際、AD8251 が関与するノイズは、通常は AD8251 のデータシートの電圧ノイズ値を使用した予測値より小さくなります。これは、AD8251 のノイズ仕様が統計的にガードバンドを考慮しているためです。

受動部品が関与するノイズ

図 1 に示す回路で用いられている整合抵抗ネットワークと等価なノイズ源を、図 3 に示します。RF および RG は ADC 用ドライバのシグナル・ゲインを設定する抵抗、R1 および R2 はレベル・シフト電圧を設定する抵抗です(図 2 も参照)。R1 およびR2 は、R1 と R2 の並列抵抗と等しい単一の抵抗(R1||R2)で表しています。これらの抵抗はそれぞれが、システム全体のノイズに含まれる熱ノイズを発生します。

各抵抗が関与するノイズは、回路内の配置によって決まる様々なゲイン要因の影響を受けます。

RF が関与するノイズは次式で表せます。

ここで

kB はボルツマン定数。

T はケルビン単位での絶対温度(300 K と仮定)。

RG が関与するノイズは、RF と RG で設定される ADC 用ドライバのシグナル・ゲインで増幅されます。

R1 および R2 はノイズの観点では並列関係にあるように作用し、そのため、両者の熱ノイズを合わせたものは、R1||R2 の値を持つ単一抵抗の熱ノイズと等価なものになります。この結合した熱ノイズはさらに、ADC 用ドライバのノイズ・ゲインで増幅されます。

抵抗が関与する全ノイズは、これら個々のノイズの関与についての二乗和平方根をとって、次式で表せます。

これらの計算について詳細は、MT-049 および MT-050 のチュートリアルを参照してください。

ADAQ7988 に内蔵の ADC 用ドライバおよび ADC が関与するノイズ

ADAQ7988 の ADC 用ドライバは、内蔵の SAR ADC の駆動用として理想的です。入力電圧ノイズが低いため、システム性能の劣化を最小限にとどめます。

この ADC 用ドライバが関与するノイズ(vn,ADC DRIVER)は、次式で求めることができます。

ここで、eADC DRIVER は ADC 用ドライバの入力電圧ノイズです。

このノイズは、非反転ノードでのノイズ源として使用規定されているため、ADC 用ドライバのノイズ・ゲインによって増幅されます。この場合、ADC 用ドライバの電流ノイズは電圧ノイズに比べ小さいため、無視できます。

ユニポーラ SAR ADC の入力 rms 電圧ノイズ(vn,ADC)は、所定のリファレンス電圧で仕様規定された S/N 比から、次式を用いて求めることができます。

ここで

VREF は使用するリファレンス電圧(図 1 の回路の場合 5 V)。

SNR は、ADAQ7988 のデータシートにおけるリファレンス電圧に対して仕様規定された S/N 比(91.5 dB)。

システムの精度解析

データ・アクイジション・システムは通常、高い正確さと精度を実現するように設計されています。しかし、システムを構成する部品にはある程度の誤差と不確定性があり、このためにシステム全体の正確さと精度に制限を受けます。一般に仕様規定されているシステム誤差に、オフセット誤差とゲイン誤差の 2 つがあります。これらの誤差は温度ドリフトによっても影響を受け、通常ある特定の温度で補正されていますが、動作温度範囲全体にわたって補正されているわけではありません。次のセクションでは、個々の部品の誤差仕様値を用いて、図 1 に示すシステムについて周囲周囲温度とそれを超える温度でのシステムの不正確さの最大予測値を見積もる方法を示します。

オフセット誤差解析

オフセット誤差は、入力信号とは無関係なシステムの不正確さの一種です。このシステムのオフセット誤差の原因には、AD8251 のオフセット(VOS,AD8251)、ADAQ7988 のゼロ誤差(VOS,ADAQ7988)、ADC 用ドライバの入力バイアス電流に起因するオフセット(VOS,IB)、ADC 用ドライバの非反転ノードでのレベル・シフト電圧発生の不正確さ(VOS,LS)などがあります。システムのオフセット誤差の最大予測値(入力換算)はこれらを全て足し合わせて、次式で表せます。

表 2 に、システムのオフセット誤差について入力換算(RTI)した最大予測値の計算結果を示します。部品のオフセットをシステムのオフセットに変換するため、関連するゲイン・ファクター、すなわち ADC 用ドライバの非反転ゲインと反転ゲイン、および、AD8251 のゲイン設定値を、部品のオフセットに乗じたり除したりする必要があります。ADC 用ドライバの非反転ゲインと反転ゲインの公称値はそれぞれ 1.25 および 0.25 です。これらの数値を用いてシステムの RTI オフセットを計算します。

AD8251 の最大入力換算オフセットは、そのゲイン設定値の関数として規定されています。表 2 に、AD8251 の RTI オフセット誤差を、その 4 通りのゲイン設定値全てに対して示します。詳細については、AD8251 データシートを参照してください。

ADAQ7988 のゼロ誤差によって、全サブシステムの入力換算オフセット誤差が仕様規定され、この誤差は従来のオペアンプのオフセット電圧と同様の方法で扱うことができます。ADAQ7988 の最大ゼロ誤差は、±0.5 mV と仕様規定されます。この誤差は、ADC 用ドライバの非反転ゲイン(1.25)を掛け、ADC 用ドライバの反転ゲイン(-0.25)と AD8251 のゲインで割ることで、システムの RTI オフセット誤差に変換できます。

または

ここで、GAD8251 は AD8251 のゲイン設定値。

ADC 用ドライバの入力バイアス電流が、ドライバの入力部で整合抵抗ネットワークと相互作用する際にオフセット誤差が生じます。これによって生じる出力換算オフセットは次式で表せます。

または

ここで、IB は ADAQ7988 内蔵の ADC 用ドライバに仕様規定された入力バイアス電流(最大 800 nA)。

この場合、2 つのバイアス電流は等しいと仮定しています。これは、デバイスの入力オフセット電流がその入力バイアス電流に比べて非常に小さいためです(入力バイアス電流誤差についての詳細は、MT-038 チュートリアルを参照)。

入力バイアス電流に起因する出力換算オフセット(VOS,IB(RTO))をシステムの入力換算オフセット誤差に変換するには、ADC 用ドライバの反転ゲインと AD8251 のゲインでこの値を割ります。

このオフセット誤差は入力に対して常に正側になります。このため、正の最大オフセット誤差の計算にはこれを使用しますが、負の最大オフセット誤差の計算では無視されます。

ADC 用ドライバのレベル・シフト電圧の発生時の不正確さも、システムのオフセット誤差をもたらします。しかし、レベル・シフト電圧は ADC のリファレンス・ソースで供給されるため、システム・オフセットはリファレンス電圧の変位にはあまり影響されません(アナログ・フロント・エンドのセクションを参照)。つまり、レベル・シフト電圧の唯一の誤差原因は、R1 and R2 で構成される分圧回路の抵抗の許容誤差ということになります。ADAQ7988 内蔵の ADC 用ドライバの非反転入力での理想的なレベル・シフト電圧は次式で表せます。

抵抗分圧器は整合抵抗ネットワークで構成されており、図 2 でR1 および R2 と示されています。ネットワークには 1 kΩ の抵抗が 4 つ備わり、減衰ファクターが 0.4(R1 = 1.5 kΩ、R2 = 1 kΩ)となるよう設定されています。ネットワークの抵抗の相対許容値は ±0.05 % と仕様規定され、減衰ファクターの 0.4 からの偏差を抑制する効果があります。分圧器回路の誤差は、整合抵抗ネットワークの設定値および相対許容誤差値を用いて計算すると、ワーストケースで ±0.03 % となります(レベル・シフト電圧を生成するために使用する抵抗ネットワークについての詳細は、CN-0393 設計サポートファイルの CN-0393 schematic を参照してください)。

したがって、ADAQ7988 内蔵の ADC 用ドライバの非反転入力のレベル・シフト電圧の範囲は、次のようになります。

システムの入力に換算すると、レベル・シフトの不正確さによるオフセット誤差は、次式のとおりです。

図 1 に示すシステムの入力換算オフセット誤差の最大予測値は、これらの誤差の和となります。その計算値を、4 通りのチャンネル・ゲイン設定値全てについて、表 2 に示します。これらの値は周囲温度(25 °C)での最大予測誤差であることに注意してください。

| Channel Gain | VOS,AD8251 (mV) | VOS,LS (mV) | VOS,ADAQ7988 (mV) | VOS,IB (mV) | VOS,SYSTEM (mV) | |

| Min | Max | |||||

| −0.25 | ±0.8 | ±3 | ±2.5 | +0.8 | −6.3 | +7.1 |

| −0.5 | ±0.5 | ±1.5 | ±1.25 | +0.4 | −3.25 | +3.65 |

| −1 | ±0.35 | ±0.75 | ±0.625 | +0.2 | −1.725 | +1.925 |

| −2 | ±0.275 | ±0.375 | ±0.3125 | +0.1 | −0.9715 | +1.0715 |

オフセット誤差の温度ドリフト

システムの補正手順ではシステムの周囲温度でのオフセット誤差は補正できますが、温度ドリフトによる誤差変動を補正することは通常はできません。オフセットが温度変動とともにどのように変化するかを定量化することは、システムが仕様規定された温度範囲の中でどのように動作するかを評価するうえで有用なことです。シグナル・チェーンの能動部品にはそれぞれ、オフセットに関して仕様規定された温度ドリフトがあります。抵抗ネットワークにも相対的な温度係数の仕様値があり、これによって動作温度範囲の中で各抵抗の変動の相対的な整合が確保されています。

オフセット誤差の温度ドリフトは、各部品の温度ドリフトの影響を組み合わせることで、システムの仕様値として扱うことができます。その際、シグナル・チェーンの部品間での温度の相違はないと仮定します。全てのデバイスの温度が等しく、そのドリフト方向が全て同じであると仮定すると、システムのオフセット温度ドリフトの最大予測値は次式で表せます。

ここで

TCVOS,AD8251 は仕様規定された温度範囲での AD8251 の入力換算オフセット・ドリフト(単位は μV/°C)。

TCVOS,LS は ADAQ7988 に内蔵の ADC 用ドライバに供給されるレベル・シフト電圧の温度ドリフト(AD8251 の入力換算値、単位は μV/°C)。

TCVOS,ADAQ7988 は ADAQ7988 のオフセット・ドリフト(AD8251の入力換算値、単位は μV/°C)。

TCVOS,SYSTEM は、図 1 に示す回路の各チャンネルの等価入力換算オフセットの温度ドリフト。

AD8251 の入力換算オフセット・ドリフト(TCVOS,AD8251)は、4通りのゲイン設定値全てについてデータシートに記されており、これらの値を表 3 に示します。

ADAQ7988 のゼロ誤差温度ドリフトもデータシートに示され、最大 1.3 μV/°C と仕様規定されています。このドリフトは、周囲温度でのオフセット誤差を変換した際と同じ方法で、次式のようにシステムの RTI 温度ドリフトに変換できます(オフセット誤差解析のセクションを参照)。

または

ここで、GAD8251 は AD8251 のゲイン設定値。

レベル・シフト電圧の温度ドリフトは、R1 および R2 から成る抵抗分圧器の温度ドリフトに起因します。リファレンス・ソースのオフセット・ドリフトは、レファレンス・ソースがレベル・シフト電圧と ADAQ7988 内蔵の ADC とで共用されているため、システムで打ち消されます(アナログ・フロント・エンドのセクションを参照)。したがって、レベル・シフト電圧の温度ドリフトは R1 および R2 のドリフトで決まり、次式のようになります。

ここで

VLS はレベル・シフト電圧の公称値(2 V)。

TCVLS はレベル・シフト電圧の等価温度ドリフト(単位はμV/°C)。

VREF は ADR4550 が供給するリファレンス電圧(公称 5 V)。

TCR1 および TCR2 はそれぞれ R1 and R2 の温度係数(単位はppm/°C)。

TCRDIV は抵抗分圧器の等価温度ドリフト(単位は ppm/°C)。

TCRDIV は分圧比(公称値 0.4)の偏差(アナログ・フロント・エンドのセクション参照)。

整合抵抗ネットワークの抵抗には、相対的な抵抗温度係数(TCR)の最大値が仕様規定されており、±15 ppm です。レベル・シフト電圧の実効的な温度ドリフトを決めるため、R2 には温度ドリフトがないと仮定し、R1 から成る部品には±15 ppm の絶対 TCR があると仮定します(TCR1 = 15 ppm/°C、TCR2 = 0ppm/°C)。このシナリオでは抵抗分圧器のワーストケースの誤差が示されます。したがって、抵抗分圧器の温度ドリフトの最大予測値は次のようになります。

TCRDIV,MAX は ±9 ppm/°C に等しくなります。

したがって、レベル・シフト電圧の温度ドリフトは次のようになります。

TCVLS の単位は ppm/°C なので、AD8251 の入力に直接適用できます。TCVOS,LS は AD8251 の入力端で ±9 ppm/°C、すなわち次式のとおりです。

図 1 に示すシステムについてオフセットの温度ドリフトの最大予測値は、各部品の温度ドリフトの和です。その計算値を、4通りのチャンネル・ゲイン設定値全てについて、表 3 に示します。

| Channel Gain | TCVOS,AD8251 (μV/°C) | TCVOS,LS (μV/°C) | TCVOS,ADAQ7988 (μV/°C) | TCVOS,SYSTEM (μV/°C) |

| −0.25 | ±6.2 | ±90 | ±6.5 | ±102.7 |

| −0.5 | ±3.7 | ±45 | ±3.25 | ±51.95 |

| −1 | ±2.45 | ±22.5 | ±1.63 | ±26.58 |

| −2 | ±1.83 | ±11.25 | ±0.82 | ±13.9 |

ゲイン誤差解析

ゲイン誤差は、入力信号に比例するシステムの不正確さの一種です。ゲイン誤差の原因には、AD8251 および ADAQ7988 のゲイン誤差、ゲイン設定用抵抗の許容誤差に起因する ADC 用ドライバのシグナル・ゲインの誤差、リファレンス電圧源(ADR4550)の誤差などがあります。図 1 に示す回路のチャンネルの公称ゲインは次式のとおりです。

ここで

GAD8251 は AD8251 のゲイン設定値。

VREF は ADR4550 が供給するリファレンス電圧。

RF および RG は ADAQ7988 内蔵の ADC 用ドライバのゲインを設定するために使用する抵抗(図 2 参照)。

システムのワーストケースの範囲は、個々の部品のゲイン誤差を足し合わせて求めることができ、次式のようになります。

ここで

GSYSTEM はシステム全体のゲイン(各チャンネルのゲイン)。

eAD8251 は AD8251 のゲイン誤差(ゲイン設定値のそれぞれに対応)。

eG は RF と RG の比の誤差。

eREF はリファレンス電圧の誤差。

eADAQ7988 は ADAQ7988 のゲイン誤差。

システムのゲイン誤差の最大予測値(eSYSTEM)は、シグナル・チェーン内における各部品のゲイン誤差の最大予測値の和で、次式のとおりです。

表 4 に、システムのゲイン誤差の最大予測値の計算結果を、4通りのチャンネル・ゲイン設定値に対して示します。

AD8251 の最大ゲイン誤差は、4 通りのゲイン設定値に対して仕様規定されています。これらのゲイン誤差は表 4 の eAD8251 の列に示してあります。ADAQ7988 についても、最大ゲイン誤差がパーセント・フルスケールで仕様規定されており、同様に表 4に示しています。

ADAQ7988 内蔵の ADC 用ドライバの最大シグナル・ゲイン誤差は、整合抵抗ネットワークのゲイン設定抵抗(図 2 の RF および RG)の相対許容誤差に基づいて計算できます。レベル・シフト電圧の設定に使用するネットワークと同様、このネットワークには 4 つの 1 kΩ 抵抗があります。これらの抵抗で、500 Ωの RF と 2 kΩ の RG が形成され、-0.25 の公称ゲインとなります(CN-0393 schematic を参照)。ネットワークの抵抗は、相対許容誤差が ±0.05 % と仕様規定されており、このため、シグナル・ゲインの最大偏差も約 ±0.05 % になります。

リファレンス・ソースの偏差は、システムのオフセット誤差に対しては大きな影響はありませんが、システムのゲイン誤差に対しては影響します。リファレンス・ソースの主要な誤差には、初期出力電圧誤差(±0.02 % または ±1 mV)、ハンダ処理時の熱によるシフト(±0.02 % または ±1 mV)、負荷レギュレーションの限界(80 ppm/mA)による不正確さがあります。これらの仕様値は ADR4550 データシートに記載されています。図 1 の回路において、ADR4550 は両チャンネルのレベル・シフト電圧を設定している整合抵抗ネットワークに直結しています。各ネットワークは 2.5 kΩ の負荷として機能します。したがって、ADR4550 は合計 4 mA の電流源となり、負荷レギュレーション誤差のワーストケースは 320 ppm、すなわち ±1.6 mV となります。リファレンス電圧の合計最大誤差はこれら 3 つの誤差の合計値で ±3.6 mV、つまり ±0.072 % となります。

図 1 のシステム全体のゲイン誤差の最大予測値は、これらの各部品の誤差を用いて求めることができます。表 4 に、システムのゲイン誤差の最大予測値を、4 通りのチャンネル・ゲイン設定値に対して示します。これらの値は周囲温度(25 °C)での最大予測誤差であることに注意してください。

| Channel Gain | eAD8251 | eG | eREF | eADAQ7988 | eSYSTEM |

| −0.25 | ±0.03% | ±0.05% | ±0.072% | ±0.01% | ±0.162% |

| −0.5 | ±0.04% | ±0.05% | ±0.072% | ±0.01% | ±0.172% |

| −1 | ±0.04% | ±0.05% | ±0.072% | ±0.01% | ±0.172% |

| −2 | ±0.04% | ±0.05% | ±0.072% | ±0.01% | ±0.172% |

ゲイン誤差の温度ドリフト

システムのゲイン誤差は温度の変動にも敏感です。オフセット誤差のドリフトと同様、ゲインの温度ドリフトを定量化することが重要です。なぜなら、これらの変動は通常、校正では補正できないためです。シグナル・チェーンの能動部品にはそれぞれ、ゲインに関して仕様規定された温度ドリフトがあります。抵抗ネットワークにも相対的な温度係数の仕様値があり、これによって動作温度範囲の中で各抵抗の変動の相対的な整合が確保されています。

システム・ゲインの温度による変動は、各部品の温度ドリフトの仕様値の関数です。周囲温度でのシステムのゲイン誤差と同様、システム・ゲインの温度ドリフトの最大予測値は、次式のように部品のゲインの温度ドリフトの和となります。

ここで

TCSYSTEM はシステム・ゲインの温度ドリフトの最大予測値。

TCAD8251 は AD8251 のゲインの温度ドリフト仕様値。

TCG は ADAQ7988 に内蔵の ADC 用ドライバのクローズドループ・ゲインにおけるゲインの温度ドリフト(RF および RG の温度ドリフトの関数)。

TCREF は ADR4550 の温度ドリフト仕様値。

TCADAQ7988 は ADAQ7988 のゲイン誤差の温度ドリフト仕様値。

TCAD8251、TCREF、TCADAQ7988 は AD8251、ADR4550、ADAQ7988 のデータシートに記載されています。TCAD8251 は 10 ppm/°C(AD8251 の全ゲイン設定値に対して)、TCREF は 2 ppm/°C、TCADAQ7988 は 0.4 ppm/°C です。

TCG は Rf および Rg を構成する整合抵抗ネットワークの相対 TCR によって決まります。オフセット誤差の温度ドリフトのセクションで説明したように、これらの抵抗には 15 ppm/°C に相当する相対 TCR があります。ADC 用ドライバのクローズドループ・ゲインは RG に対する RF の比なので、クローズドループ・ゲインの温度ドリフトは、この相対 TCR に対応する仕様値に等しくなります。したがって、TCG は 15 ppm/°C です。

これにより、TCSYSTEM は次のようになります。

デジタル・インターフェースとアイソレーション

図 1 に示すシステムは、デジタル・ホストとデータ・アクイジション・シグナル・チェーンとの間で絶縁が施されています。ADuM3470 および ADuM3150 には それぞれ、AD8251 のアドレス信号と ADAQ7988 の SPI 信号に対してデジタル・アイソレーション・チャンネルが備わっています。

デジタル・アイソレーションを施す設計上、鍵となる考慮事項は、絶縁チャンネルを有効活用すること、すなわち設計を完成させる際に用いる絶縁チャンネルの数を最適化することです。その理由は、絶縁チャンネルを追加することで、新たな部品の追加が必要となる可能性があり、それにより設計コスト、回路面積、消費電力が増加する可能性があるためです。このシステムのデジタル実装では、絶縁障壁間の ADAQ7988 SPI 信号の配線経路を最適化することだけではなく、AD8251 のアドレス信号を制御するアイソレータ・デバイス内に配電回路を含めることで、効率化を実現しています。

図 4 に、ADAQ7988 デバイスとマスターとの間の ADuM3150 絶縁チャンネルを介したデジタル・インターフェース接続を示します。

ADuM3150 SPIsolator™ デジタル・アイソレータ・デバイスは絶縁型 SPI インターフェース向けに最適化されています。スレーブ・セレクト、MOSI、MISO、シリアル・クロック信号用の 4 つの高速絶縁チャンネルを備え、それらが両方の ADAQ7988 のデジタル入出力ピンに接続されています。

さらに、ADuM3150 には遅延クロック(DCLK)出力機能があり、これによって、SPI インターフェースでのデジタル・タイミングの制約が著しく軽減され、40 Mbps の SPI 転送レートが、シリアル・クロックをマスターにフィードバックする絶縁チャンネルを設けずに実現できます。図 4 に SPI 信号と DCLK 信号の配線図を示します。

DCLK 信号は、マスターが供給するシリアル・クロック(MCLK)を遅延させた複製信号です。MCLK と DCLK 間の遅延は、シリアル・クロックと ADuM3150 の MISO チャンネルの往復の伝搬遅延に一致するよう、出荷テスト時に調整されます。DCLK は、マスターが独立した読出しクロックとして使用し、MISO ラインのデータをクロックに同期して入力させます。この構成にすると、MISO データは DCLK にクロック同期して入力する瞬間、確実に用意ができています。詳細については、MS-2689 技術記事、Isolating SPI for High Bandwidth Sensorsを参照してください。

ADAQ7988 デバイスは、デイジーチェーン・モードで構成される設計となっています。この構成により、両方の ADAQ7988 デバイスの 16 ビット出力が 1 本の MISO(SDO)ラインで伝送でき、データをマスターに返送する絶縁チャンネルも 1 本で済みます。両デバイスからの変換結果は、2 つのシリアル接続された 16 ビットのシフト・レジスタと同様に、SCK ピンの立下がりエッジでクロックに同期して出力されます。この構成では、マスターは 32 ビットのシリアル・クロック・サイクルを出力して、両方の結果を読み出すことが必要です。

デジタル・アイソレータを使用したレイアウト設計についての詳細は、ADuM3470 および ADuM3150 のデータシートを参照してください。

配電

AD8251 のアドレスに絶縁チャンネルを設定することに加え、ADuM3470 は図 1 の回路の一次側から二次側へ電力を供給します。ADuM3470 は PWM コントローラと低インピーダンス・トランス・ドライバ(X1 および X2)を内蔵しており、これにより、外部トランス、全波ショットキー・ダイオード整流器、ローパス・フィルタを駆動します。電源回路は、5 V または 3.3 V の入力電圧時に、最大 2 W を出力する絶縁された安定化電源です。これにより、絶縁型 DC/DC コンバータを別途用意する必要がなくなります。

ADuM3470 の安定化は正側電源を用いて行われます。分圧器ネットワークから安定化用の帰還が行われ、出力電圧が約 16.5 Vのとき、帰還電圧が 1.25 V になるように選択されています。この帰還電圧は ADuM3470 の内部帰還設定電圧 1.25 V と比較されます。安定化は外部トランスを駆動する PWM 信号のデューティ・サイクルを変えることにより実行されます。

トランスの正側および負側の電力出力は、数個の ADP7118 および ADP7182 の低ドロップアウト(LDO)レギュレータによって安定化されます。表 5 に二次側に供給されるレールを示します。

| Rail Name | Voltage | Function | Device Used |

| +VS | +15 V | AD8251 positive rail | ADP7118 |

| V+ | +7.5 V | ADAQ7988 ADC driver positive rail | ADP7118 |

| VDD | +5 V | ADAQ7988 LDO input supply | ADP7118 |

| −VS | −15 V | AD8251 negative rail | ADP7182 |

| V− | −2.5 V | ADAQ7988 ADC driver negative rail | ADP7182 |

性能測定

AC 性能の測定結果

図 1 の回路のチャンネルの 1 つについて測定した、入力トーンが 1 KHz および 10 kHz の場合の AC 性能を、表 6 に示します。測定仕様は、S/N 比(SNR)、全高調波歪み(THD)、信号/ノイズ + 歪み(SINAD)です。図 5、6、7 に、SNR、THD、SINAD と 周波数の関係を、4 通りのチャンネル・ゲイン設定値について示します。THD には 5 次高調波まで含まれています。

入力信号として、Audio Precision 製 SYS-2700 シリーズのシグナル・ジェネレータを使用し、1 kHz、10 kHz、20 kHz、50 kHz の差動フルスケール信号を供給しました。ゲインが −0.25、−0.5、−1、−2 の場合に対するフルスケール入力信号はそれぞれ、±10V、±5 V、±2.5 V、±1.25 V です。

| Gain (V/V) |

fIN = 1 kHz | fIN = 10 kHz | ||||

| SNR | THD | SINAD | SNR | THD | SINAD | |

| −0.25 | 90.4 | −104.5 | 90.3 | 90.4 | −95.5 | 89.3 |

| −0.5 | 89.2 | −103.4 | 89.1 | 89.1 | −95.2 | 88.2 |

| −1 | 89.1 | −105.9 | 89.1 | 88.9 | −94.7 | 88.0 |

| −2 | 87.2 | −102.8 | 87.2 | 87.0 | −94.6 | 86.4 |

DC 性能の測定結果

各チャンネルに対するオフセット誤差とゲイン誤差を 4 通りの各ゲイン設定値について測定しました。同一基板上の両チャンネルのオフセット誤差とゲイン誤差を、4 通りのゲイン設定値で測定した結果を表 7 に示します。

表 7 に示すオフセット誤差は mV が単位で、システム入力に換算したものです。まず、AD8251 への入力を両チャンネルとも接地し、131,072 点の出力コードを取得し平均化して、システムの平均コードオフセット(NOS)を求めました。入力換算オフセットは、次式を用いて電圧に換算できます。

ここで

VREF はリファレンス電圧(このシステムでは 5 V)。

N は ADAQ7988 の内蔵 SAR ADC の解像度(16 ビット)。

G はシステムのゲインで、AD8251 のゲインと ADC 用ドライバのゲインとの積に等しい。

オフセット誤差は、単一の基板上の両チャンネルに対し、全てのゲイン設定値で測定しました。

ゲイン誤差は、値のわかっている 2 通りの電圧を入力し、結果の出力コード(および 131,072 点の平均値)を記録し、これらの結果コード間の直線の傾きと理想的な場合の傾きとを比較して決定しました。理想的な傾き(mIDEAL)は、リファレンス電圧(VREF)と SAR ADC の解像度(N)の関数で、次式で表せます。

傾きの測定値は次のとおりです。

ここで

N1 および N2 は、2 点の入力値 V1 および V2 で測定した平均の出力コード。

V1 および V2 は、システムの正側と負側のフルスケール付近の電圧。

ゲイン誤差は、表 7 においてパーセント・フルスケール(%FS)誤差として表記されています。これらは次式で計算できます。

| Gain (V/V) |

Channel A | Channel B | ||

| Offset Error (mV) | Gain Error (%FS) | Offset Error (mV) | Gain Error (%FS) | |

| −0.25 | −2.9 | −0.01 | −4.9 | 0.11 |

| −0.5 | −1.4 | −0.01 | −2.5 | 0.12 |

| −1 | −0.7 | −0.01 | −1.3 | 0.12 |

| −2 | −0.4 | −0.01 | −0.8 | 0.12 |

バリエーション回路

さらに高精度な抵抗ネットワーク

システムの精度解析のセクションで、システム全体のオフセット誤差、ゲイン誤差、ドリフトについて、各部品の性能を基に定量化しました。ADAQ7988 ADC 用ドライバのゲインとレベル・シフト電圧を設定する抵抗ネットワークの許容誤差と温度係数のマッチングが、これらの誤差(特にオフセット温度ドリフト)に大きく影響します。これらの受動部品が関与する誤差を軽減するため、システムでは許容誤差と TCR マッチングの仕様がより厳しい整合抵抗ネットワークを用いることもできます。これらの整合抵抗ネットワークによって、システム全体の正確度は向上しますが、システム・コストが上昇します。これらの部品を選択する際には、アプリケーションの最終条件を考慮する必要があります。

ADAQ7988 の単電源構成

ADAQ7988 は単電源構成で動作可能です。消費電力と部品点数を削減することが目的の設計では、負電源のレールを接地し、正電源のレールだけでデバイスを駆動とすることが適している場合があります。内蔵の ADC 用ドライバとリファレンス・バッファのヘッドルーム条件が満たされる限り、デバイスの動作仕様への影響を最小限に抑えたままこの構成を採用することができます。これらの仕様については、ADAQ7988 データシートを参照してください。

リファレンス電圧は、ADAQ7988 のリファレンス・バッファのヘッドルーム仕様を満たすよう設定する必要があります。例えば、V+ に 5 V を供給する場合、リファレンス電圧は 3.3 V を超えないようにします。

追加の回路保護

図 1 の回路には、いくつかの過電圧保護手段が組み込まれています。TVS 保護ダイオードが両チャンネルの両入力に設けられ、大きなトランジェント電圧スパイクからチャンネルを保護しています。ADAQ7988 の設計も堅牢で、AD8251 の出力が範囲を超えるような過電圧事象にも十分対処できます。ADC のESD ダイオード、内蔵の 20 Ω 抵抗、内蔵のリファレンス・バッファおよび ADC 用ドライバの短絡回路電流限界により、デバイスの損傷を防止しています(詳細は、ADAQ7988 データシートを参照)。図 8 に、ADC 内部の ESD ダイオードが接続された様子を示します。

ADAQ7988 に内蔵の ADC 用ドライバがリファレンス電圧を超えた場合、ADC 入力と REF_OUT 間に接続された ESD ダイオードがオンになります。ダイオードを流れる電流は AMP_OUTと REF_OUT の電圧および 20 Ω の直列抵抗によって決まります。標準的な SAR ADC の設計では、ESD ダイオードを流れる電流によってリファレンス・ソースが変動することのないよう注意が必要で、このソースを複数のデバイスで共有している場合は特に注意が必要です。しかし、2 つのアンプに対する短絡電流制限によって、リファレンス・バッファは変動することなく、ADC 用ドライバからの電流を吸い込めることが確保されています。

しかし、保護がさらに必要な場合は、ショットキー・ダイオードを使用して ADC の入力電圧を REF_OUT にクランプすることができます。ショットキー・ダイオードは、過電圧事象が発生した場合に、ADC 用ドライバの出力電流の代替経路となり、この出力電流が ADC の ESD ダイオードに流れ込まないようにし、リファレンスに妨害を与えないようにします。図 9 に SAR ADCシグナル・チェーンでのショットキー・ダイオードの実装例を示します。

図 1 の回路において、ADAQ7988 に内蔵の ADC 用ドライバの出力位置に、図 9 の接続図にある同一のショットキー・ダイオードを設けるだけのフットプリントがあります。回路図、ボード・レイアウト、部品表などの EVAL-CN0393-FMCZ ボードの技術文書は全て CN-0393 設計支援パッケージ(www.analog.com/CN0393-DesignSupport)から入手できます。

追加チャンネル

図 1 の回路では AD8251 デバイスに向かう 4 つのアドレス信号のそれぞれに、絶縁チャンネルを使用しています。これは 2 チャンネルの設計では適切ですが、さらに多くのチャンネルを使用する場合は、別のアプローチをとる必要があります。

チャンネル数によって、設計では追加の信号に対応してより多くのデジタル・アイソレータを設置するか、コントローラを二次側に設けてマスター・デバイスからの命令によってこれらの信号を生成するようにする場合があります。後者のオプションは 1 つの SPI インターフェースで実現でき、このため、絶縁デバイスをこれ以上増やす必要はありません。

絶縁障壁間での単電源構成

図 1 の回路の電源構成は、部品数とボード面積を削減するよう設計されています。これは、ADuM3470 を使用して、AD8251デバイスを駆動するのに十分な大きさを持つ正側および負側のレールを供給することで、実現しています。さらに ADuM3470は、電源を 2 個は必要としないアプリケーション向けに、単一の安定化電源の機能を提供します。ADP5070 DC/DC スイッチング・レギュレータを使用すれば、単一の DC 入力を用いてより大きなバイポーラ電圧を発生することができます。ADuM3470 を ADP5070 と組み合わせて、データ・アクイジション・シグナル・チェーン用にバイポーラ・レールを発生させる方法は、CN-0385 で用いられています。

回路の評価とテスト

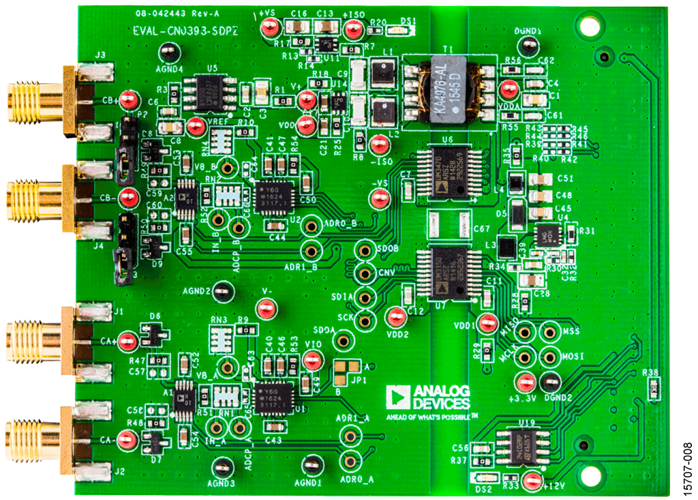

この回路では、EVAL-CN0393-FMCZ 回路ボードと SDP-H1 システム・デモンストレーション・プラットフォーム・コントローラ・ボード(EVAL-SDP-CH1Z)を使用しています。これら 2枚のボードは 160 ピン接続用コネクタで接続され、手早く組み立てて回路の性能を評価することができます。EVAL-CN0393-FMCZ ボードには図 1 の回路と SDP-H1 ボード・インターフェースが、この回路を動作させる CN-0393 評価ソフトウェアとともに含まれています。

必要な装置

以下の装置が必要になります。

- USB ポート付き Windows® XP、Windows Vista® またはWindows 7® 搭載 PC

- EVAL-CN0393-FMCZ 回路評価用ボード

- SDP-H1 コントローラ・ボード(EVAL-SDP-CH1Z)

- CN-0393 評価用ソフトウェア(ftp://ftp.analog.com/pub/cftl/CN0393/からダウンロード可能)

- 12 V DC スイッチング電源

- USB - microUSB 変換ケーブル

- 低歪み、低ノイズ・シグナル・ジェネレータ(±10 V の信号を入力する用途)

- ロー・ノイズ、高精度 DC 電源(±10 V の電源を供給する用途)

ソフトウェアのインストール

評価用ソフトウェアを ftp://ftp.analog.com/pub/cftl/CN0393/ からダウンロードし、PC にインストールします。CN-0393 ユーザー・ガイドにこのソフトウェアのインストールおよび実行方法が記載されています。

セットアップとテスト

EVAL-CN0393-FMCZ ボードと SDP-H1 ボードとを 160 ピンFMC コネクタで接続した後、電源とハードウェアを接続します。EVAL-CN0393-FMCZ および SDP-H1 のハードウェアのセットアップは、次の手順に従います。

- EVAL-CN0393-FMCZ と SDP-H1 を 160 ピン FMC コネクタで接続します。

- 12 V DC スイッチング電源を SDP-H1 ボードの +12V_VINジャックに接続します。CN-0393 評価ソフトウェアの初期化が済んでから、EVAL-CN0393-FMCZ ボードに電源を供給するように注意してください。

- SDP-H1 ボードを、USB ケーブルを介して PC に接続します。

- CN-0393 評価ソフトウェアを実行します(実行方法は CN-0393 ユーザ・ガイドを参照してください)。

テスト・セットアップの機能ブロック図を図 10 に示します。信号源は SMA コネクタまたはテスト・ポイントを介してどちらのチャンネルにも接続できます。EVAL-CN0393-FMCZ の完全な回路図については、CN-0393 設計支援パッケージを参照してください。

EVAL-CN0393-FMCZ ボードの写真を図 11 に示します。