ADAR4002

推荐用于新设计0.5 GHz 至 19 GHz、单通道、双向真实时间延迟单元

- 产品模型

- 4

概述

- 频率范围 0.5 GHz 至 19 GHz

- 可编程 7 位时间延迟

- 可编程时延范围

- 时延范围 0:0 至 508ps 范围,4ps 标准分辨率

- 时延范围 1:0 至 254ps 范围,2ps 高分辨率

- 可编程6位衰减

- 31.5 dB 调整范围

- 0.5 dB 分辨率

- 10 GHz 下的性能可达到最小时间延迟和衰减

- 插入损耗

- 时延范围 0:−20.5 分贝

- 时延范围 1:−16.2 分贝

- 输入 IP3

- 时延范围 0:15.2 dBm

- 时延范围 1:14.1 dBm

- 插入损耗

- 输入 P1dB

- 时延范围 0:5 dBm

- 时延范围 1:4.1 dBm

- 噪声系数

- 时延范围 0:21.2 dB

- 时延范围 1:16.6 dB

- 可通过 3 线或 4 线 SPI 完全编程

- 用于菊花链和快速数据加载的 14 位移位寄存器

- 功耗:1 mW,使用 1.2V 和 1.0V 双电源

- 14 引脚,3 mm × 2 mm,LFCSP

ADAR4002-CSL 是一款低功耗宽带、双向、单通道、真实时间延迟单元 (TDU) 和数字步进衰减器 (DSA)。IC 具有 18.5 GHz 的带宽,频率范围为 0.5GHz 至 19 GHz,两个 RF 端口上的输入阻抗均为 50 Ω。TDU 具有两个可编程最大时间延迟,每个都有 7 位控制。范围 0 的最大延迟为 508 ps,分辨率为 4 ps(典型值)。此范围用于较低频率,其中 ADAR4002-CSL 的插入损耗较小,并且需要更多时间延迟才能实现完整的 360° 相位覆盖。范围 1 的最大延迟为 254 ps,分辨率为 2 ps(典型值)。与范围 0 相比,此范围的插入损耗较小,并且在 ADAR4002-CSL 具有较高插入损耗且需要较少时间延迟和较小分辨率的较高频率下很有用。DSA 具有 6 位分辨率,衰减范围为 0 dB 至 31.5 dB,步长为 0.5 dB。

ADAR4002-CSL 旨在通过串行端口接口 (SPI) 或移位寄存器提供灵活的数字控制,以允许将多个芯片菊花链连接在一起。ADAR4002-CSL 包含 32 个 TDU 和 DSA 状态的寄存器内存。该存储器与片上序列器相结合,允许通过 UPDATE 引脚实现快速双向存储器推进。

ADAR4002-CSL 采用 14 引脚、3 mm × 2 mm LFCSP 封装,额定工作温度范围为 −40°C 至 +85°C。有关其他应用和技术信息,请参阅“商业太空产品计划”手册和 ADAR4002 数据手册。

应用

参考资料

在线研讨会 1

ADI 始终高度重视提供符合最高质量和可靠性水平的产品。我们通过将质量和可靠性检查纳入产品和工艺设计的各个范围以及制造过程来实现这一目标。出货产品的“零缺陷”始终是我们的目标。查看我们的质量和可靠性计划和认证以了解更多信息。

| 产品型号 | 引脚/封装图-中文版 | 文档 | CAD 符号,脚注和 3D模型 |

|---|---|---|---|

| ADAR4002ACPZ | 14-Lead LFCSP (2mm x 3mm x 0.75mm w/EP) | ||

| ADAR4002ACPZ-CSL | LFCSP | ||

| ADAR4002ACPZ-R7 | 14-Lead LFCSP (2mm x 3mm x 0.75mm w/EP) | ||

| ADAR4002ACPZR7-CSL | LFCSP |

这是最新版本的数据手册

软件资源

找不到您所需的软件或驱动?

申请驱动/软件工具及仿真模型

LTspice®是一款强大高效的免费仿真软件、原理图采集和波形观测器,为改善模拟电路的仿真提供增强功能和模型。

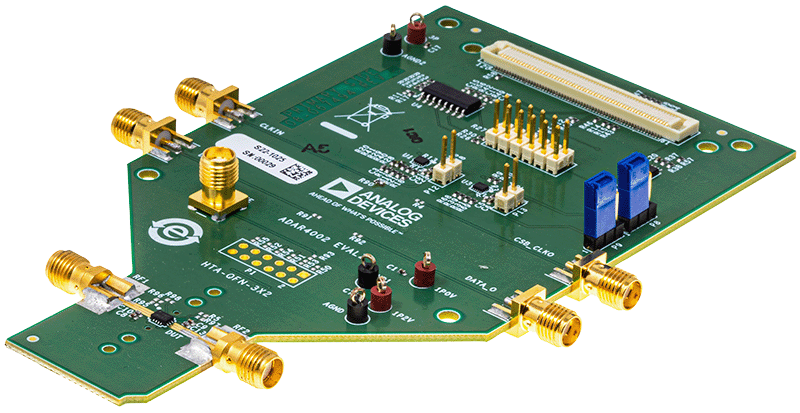

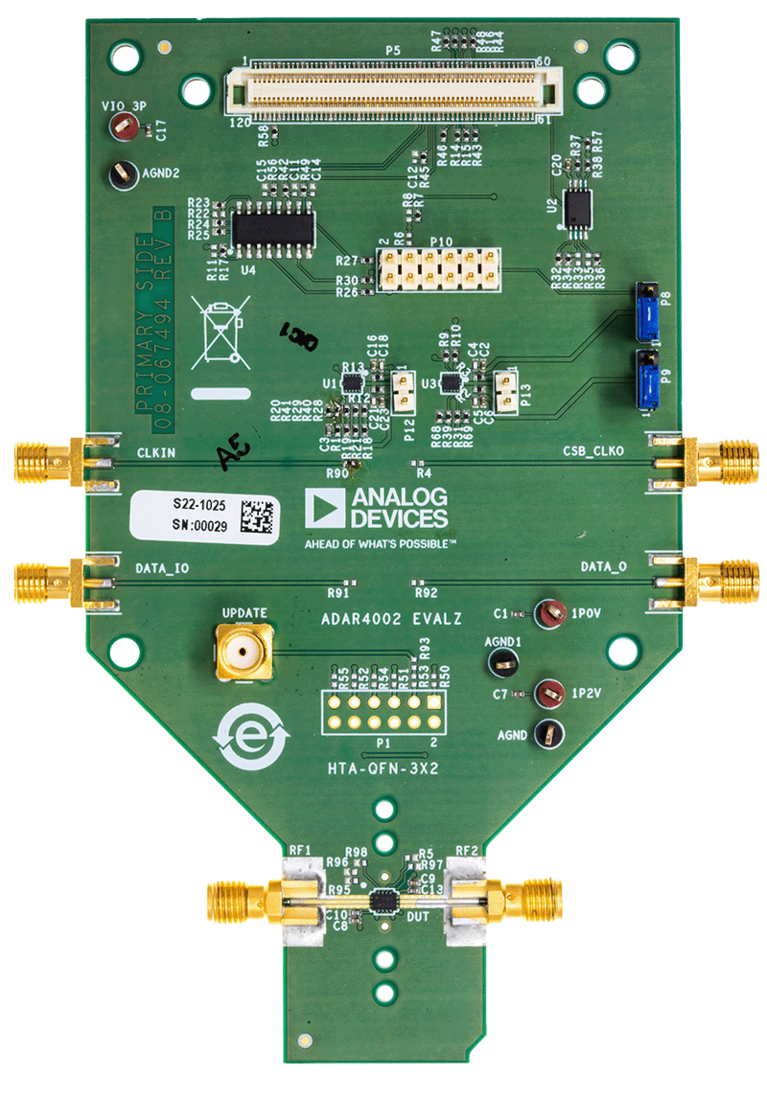

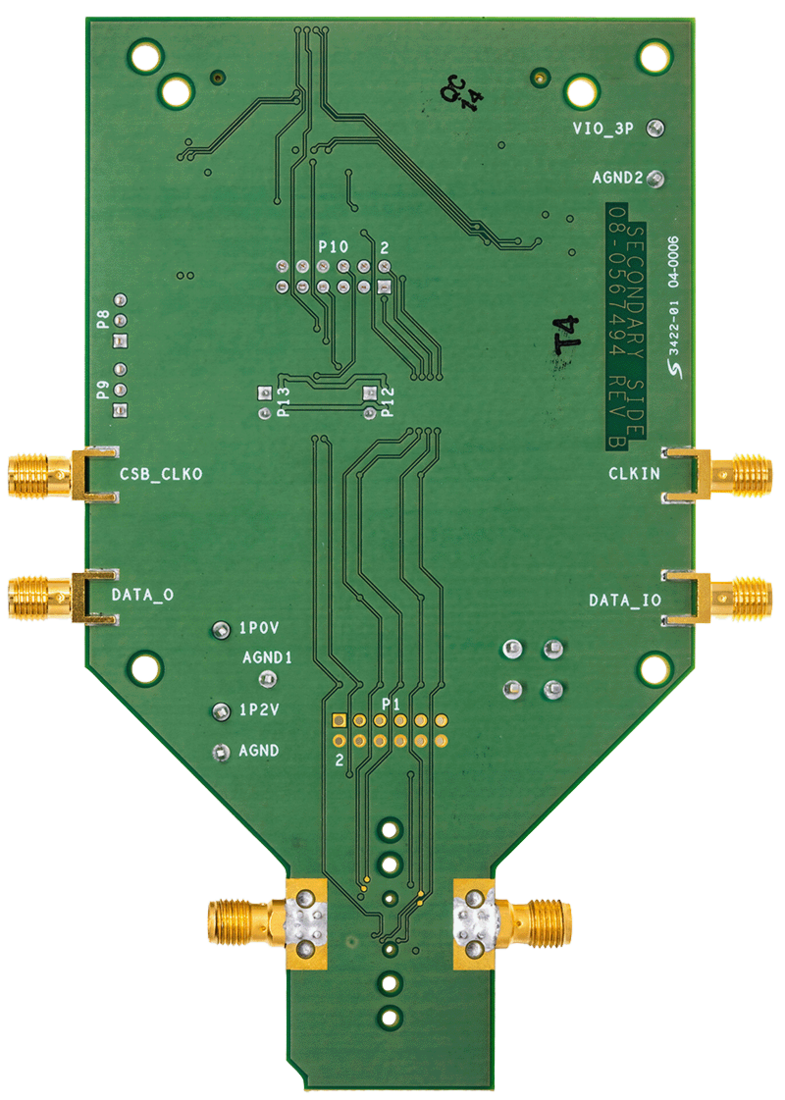

评估套件

最新评论

需要发起讨论吗? 没有关于 ADAR4002的相关讨论?是否需要发起讨论?

在EngineerZone®上发起讨论