# 0.5 GHz to 19 GHz, 1-Channel, Bidirectional True Time Delay Unit

#### **FEATURES**

- ▶ 0.5 GHz to 19 GHz frequency range

- Programmable 7-bit time delay

- Programmable time delay range (typical)

- ▶ Range 0: 0 ps to 508 ps with 4 ps standard resolution

- ▶ Range 1: 0 ps to 254 ps with 2 ps high resolution

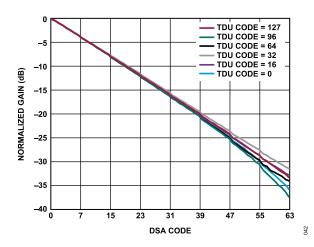

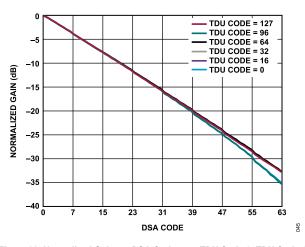

- ▶ Programmable 6-bit attenuation

- ▶ 31.5 dB adjustment range

- ▶ 0.5 dB resolution

- ▶ Performance at 10 GHz for minimum time delay and attenuation

- Insertion loss

- ▶ Time Delay Range 0: -20.5 dB

- ▶ Time Delay Range 1: -16.2 dB

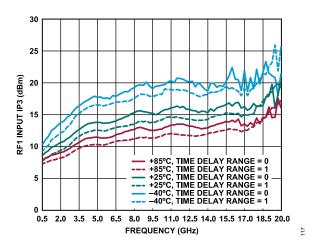

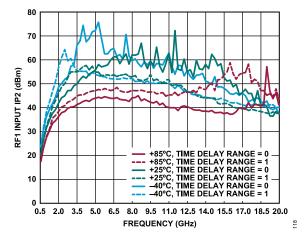

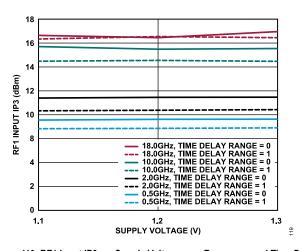

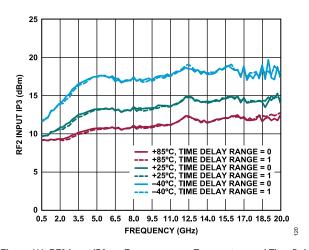

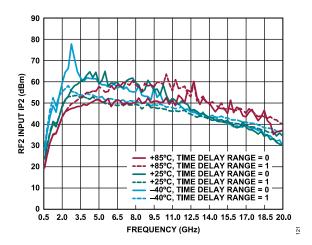

- ▶ Input IP3

- ▶ Time Delay Range 0: 15.2 dBm

- ▶ Time Delay Range 1: 14.1 dBm

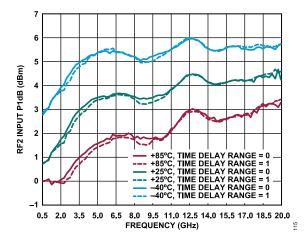

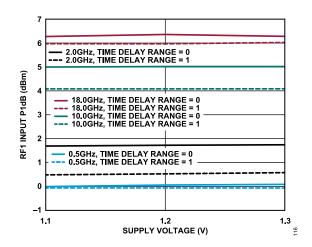

- ▶ Input P1dB

- ▶ Time Delay Range 0: 5 dBm

- ▶ Time Delay Range 1: 4.1 dBm

- Noise figure

- ▶ Time Delay Range 0: 21.2 dB

- ▶ Time Delay Range 1: 16.6 dB

- ▶ Fully programmable via a 3-wire or 4-wire SPI

- ▶ 14-bit shift register for daisy chaining and quick data load

- ▶ Power consumption: 1 mW with 1.2 V and 1.0 V dual supplies

- ▶ 14-lead, 3 mm × 2 mm, LFCSP

#### **APPLICATIONS**

- Electronic steerable antenna arrays

- Multifunction arrays

- Satellite communications (SATCOM)

- ▶ Radar

- Data links

- Test equipment

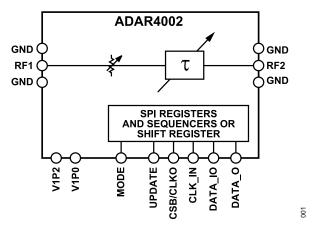

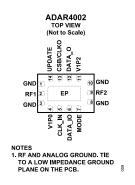

### **FUNCTIONAL BLOCK DIAGRAM**

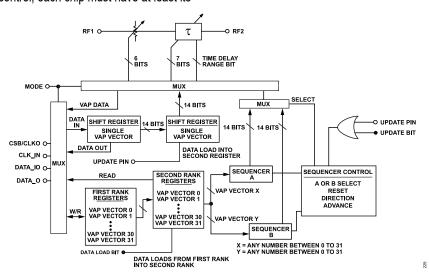

Figure 1. ADAR4002 Block Diagram

#### **GENERAL DESCRIPTION**

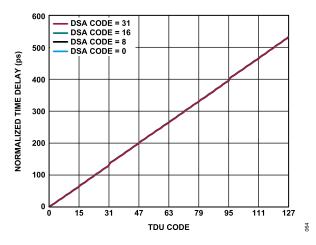

The ADAR4002 is a low power broadband, bidirectional, single-channel, true time delay unit (TDU) and a digital step attenuator (DSA). The IC has 18.5 GHz of bandwidth over a frequency range of 0.5 GHz to 19 GHz with 50  $\Omega$  input impedance at both RF ports. The TDU has two programmable maximum time delays, each with 7-bit control. Range 0 has a maximum delay of 508 ps with a resolution of 4 ps (typical). This range is used at lower frequencies where the ADAR4002 has less insertion loss and where more time delay is required for full  $360^\circ$  phase coverage. Range 1 has a maximum delay of 254 ps and a resolution of 2 ps (typical). This range has less insertion loss compared to Range 0 and is useful at higher frequencies where the ADAR4002 has higher insertion loss, and where less time delay and smaller resolution are required. The DSA has 6-bit resolution with an attenuation range of 0 dB to 31.5 dB and a step size of 0.5 dB.

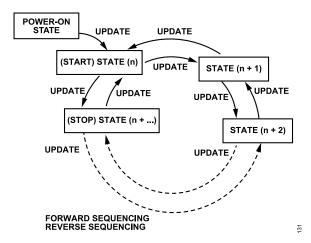

The ADAR4002 is designed to provide flexible digital control through either a serial port interface (SPI) or a shift register to allow daisy chaining multiple chips together. The ADAR4002 contains register memory for 32 TDU and DSA states. The memory combined with on-chip sequencers, allows a fast bidirectional memory advance via the UPDATE pin.

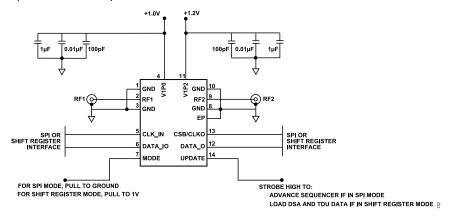

The ADAR4002 is available in a 14-lead, 2 mm x 3 mm, LFCSP and is specified from -40°C to +85°C.

# **TABLE OF CONTENTS**

| Features 1                                     | Noise Figure                                   | 31 |

|------------------------------------------------|------------------------------------------------|----|

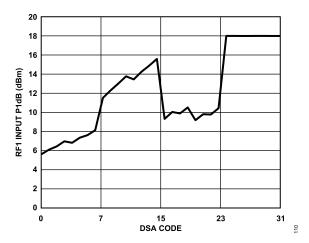

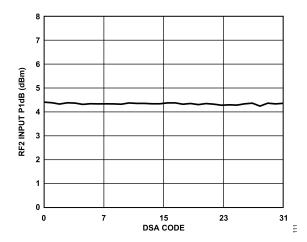

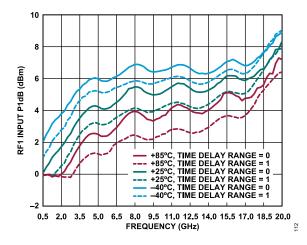

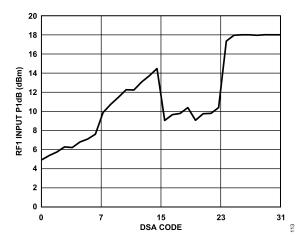

| Applications1                                  | Compression and Linearity                      | 33 |

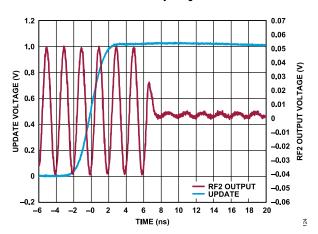

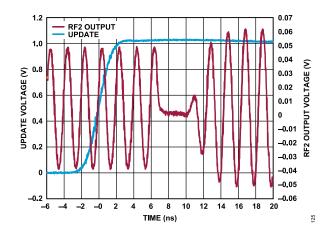

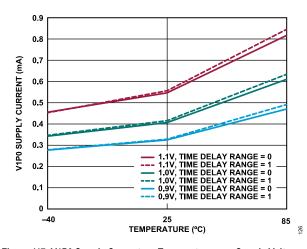

| Functional Block Diagram1                      | Supply Current and Settling Time               | 36 |

| General Description1                           | Equivalent Circuits                            | 37 |

| Specifications3                                | Terminology                                    | 38 |

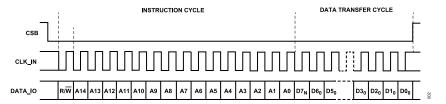

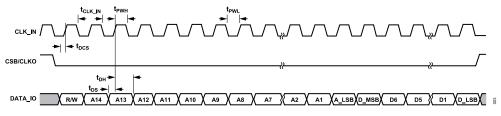

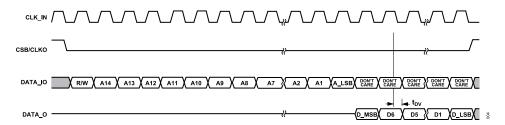

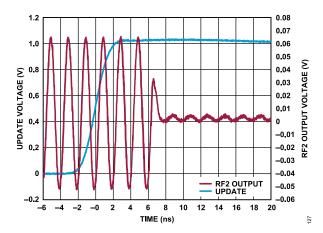

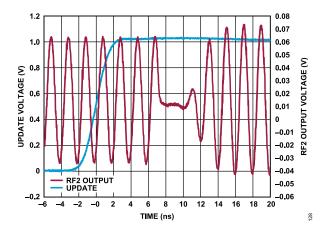

| Timing Specifications 8                        | Theory of Operation                            | 40 |

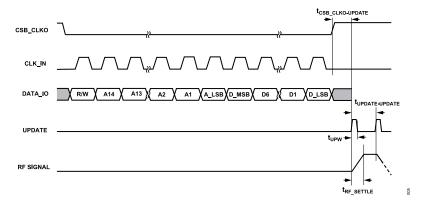

| Timing Diagrams8                               | RF Path                                        | 40 |

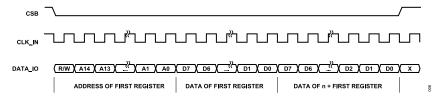

| SPI Block Write Mode10                         | TDU and DSA                                    | 40 |

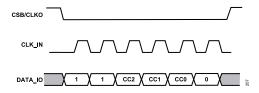

| Short Control Command10                        | Digital Section                                | 41 |

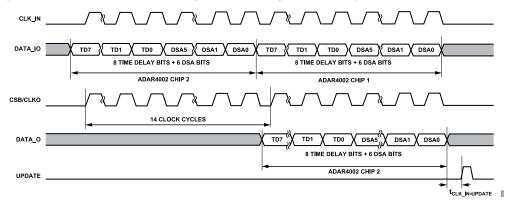

| Shift Register Mode11                          | Digital Modes and Interface                    | 41 |

| Absolute Maximum Ratings12                     | SPI Transaction Protocols                      | 42 |

| Thermal Resistance12                           | SPI Mode                                       | 42 |

| Electrostatic Discharge (ESD) Ratings12        | Data Load                                      | 42 |

| ESD Caution12                                  | Update                                         | 42 |

| Pin Configuration and Function Descriptions 13 | Shift Register Mode                            | 43 |

| Typical Performance Characteristics14          | SPI Registers                                  | 43 |

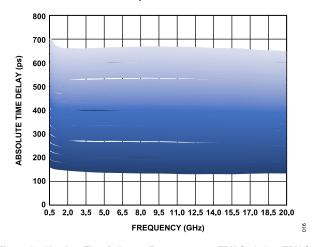

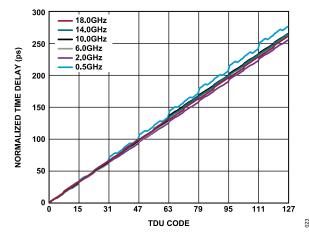

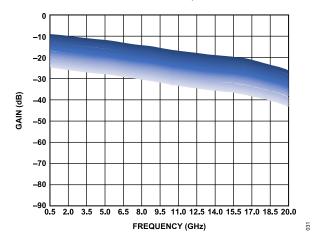

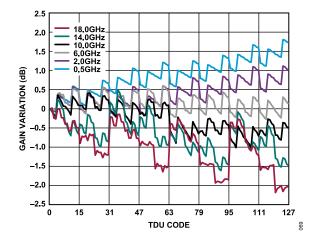

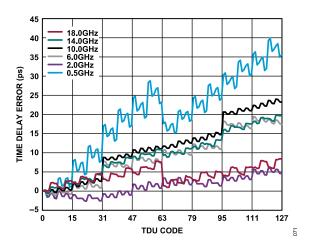

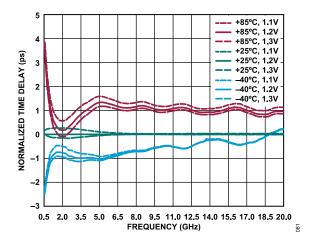

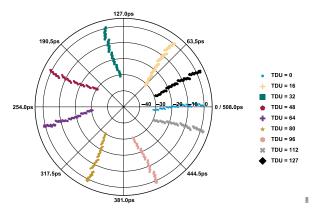

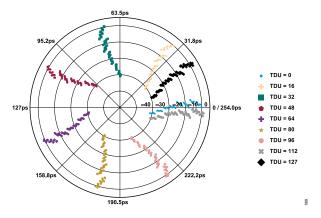

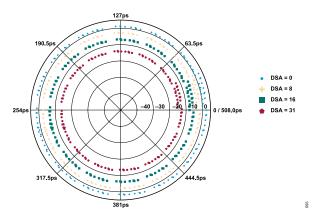

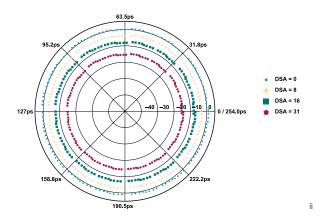

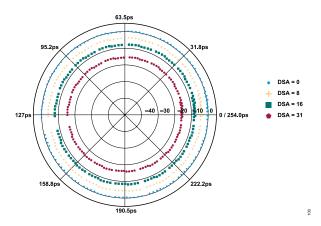

| Time Delay Sweep, Time Delay Range 014         | Applications Information                       | 45 |

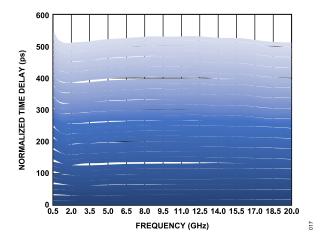

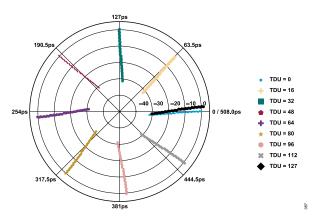

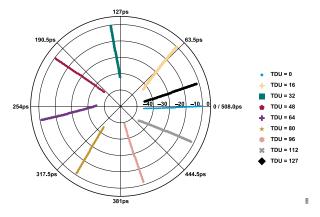

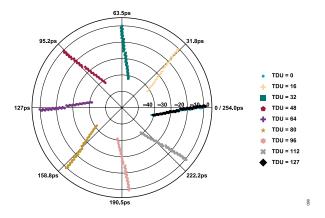

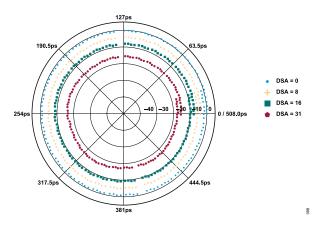

| Time Delay Sweep, Time Delay Range 116         | Basic Connections                              | 45 |

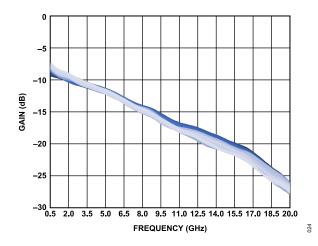

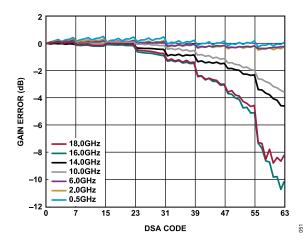

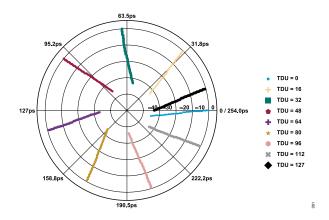

| DSA Attenuation Sweep, Time Delay Range        | Device Setup                                   | 46 |

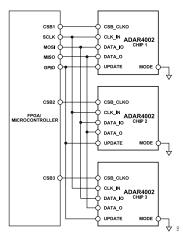

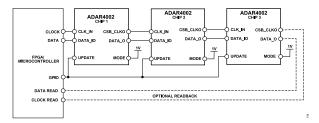

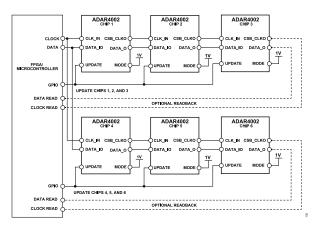

| 0 17                                           | Digital Interface for Multiple Chip Operation. | 46 |

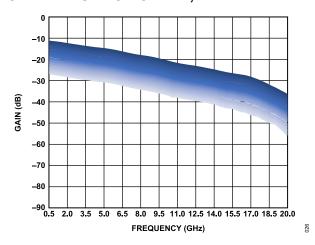

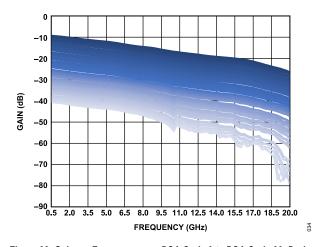

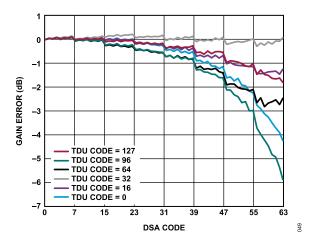

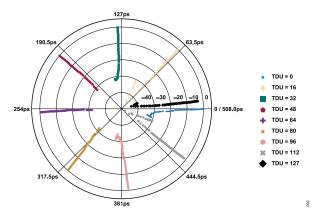

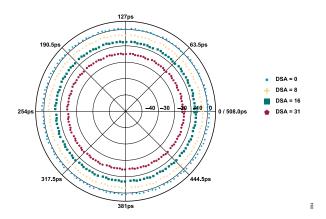

| DSA Attenuation Sweep, Time Delay Range        | Power Management Recommendations               | 47 |

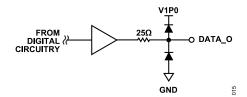

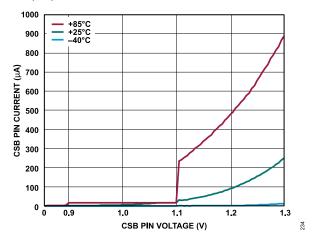

| 118                                            | Logic Voltages Greater Than 1.2 V              | 48 |

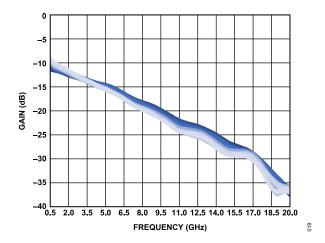

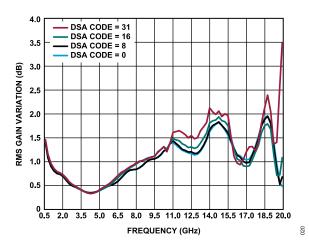

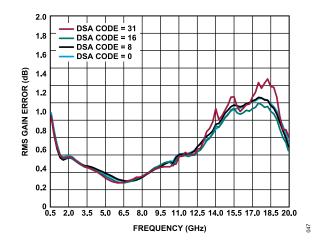

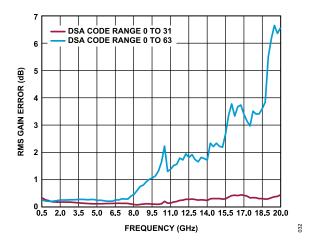

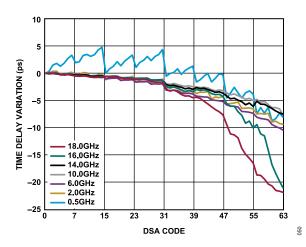

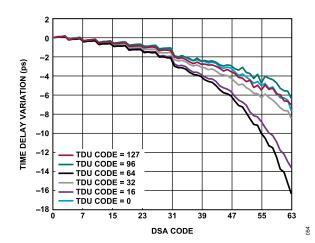

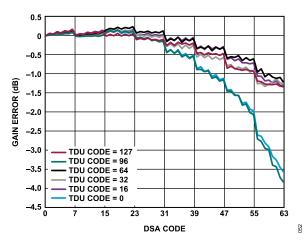

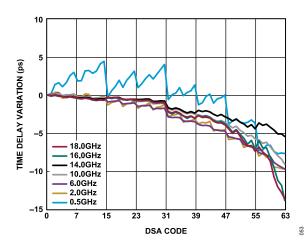

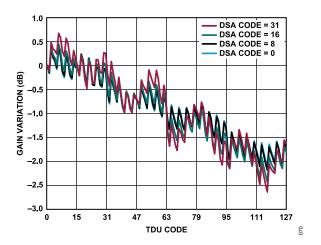

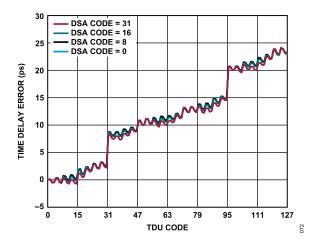

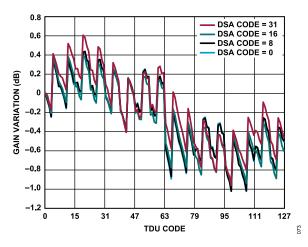

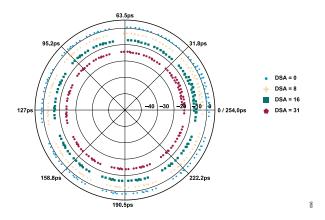

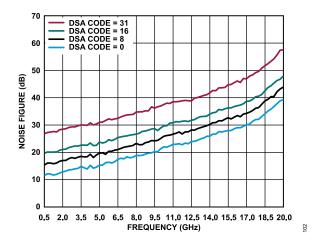

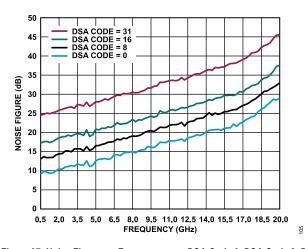

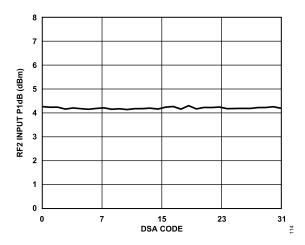

| DSA Sweeps19                                   | Register Map                                   | 49 |

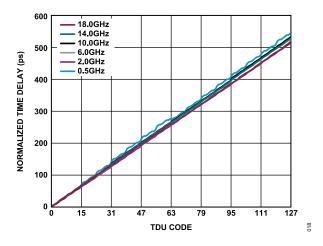

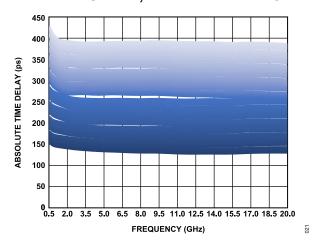

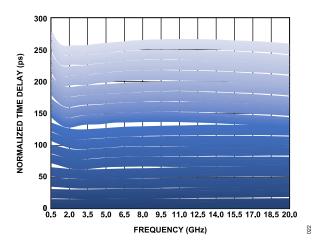

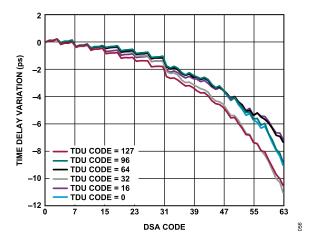

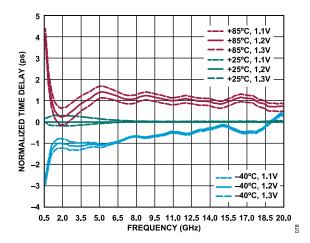

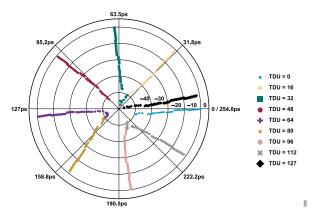

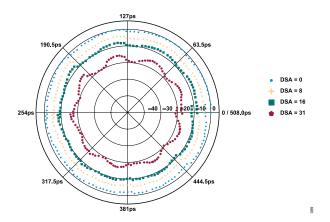

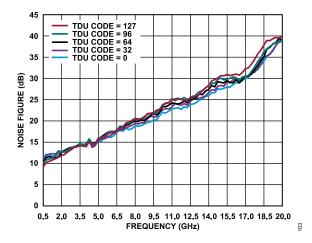

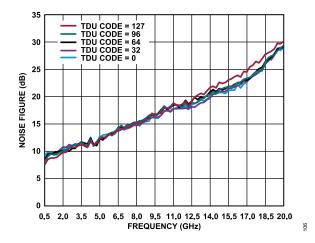

| TDU Sweeps23                                   | Outline Dimensions                             | 66 |

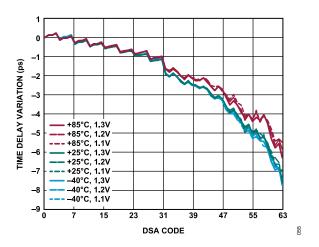

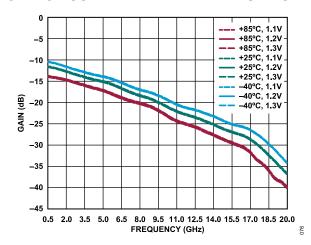

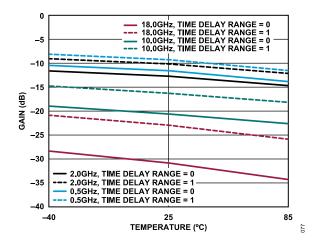

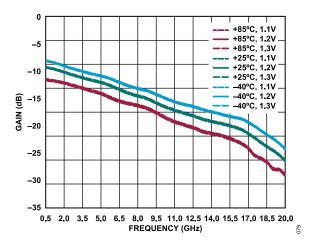

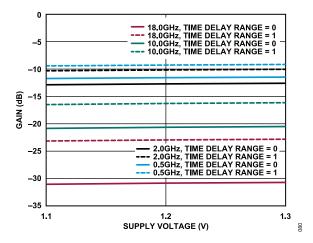

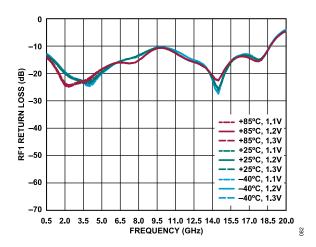

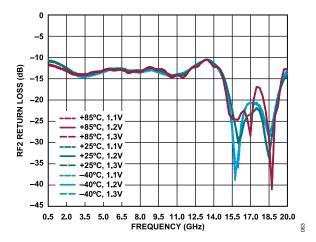

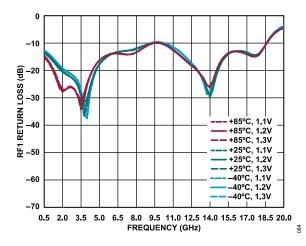

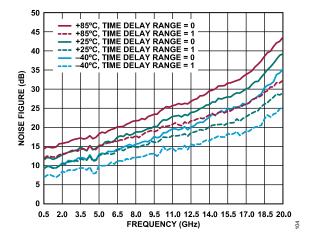

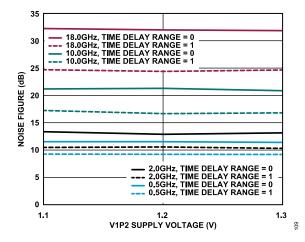

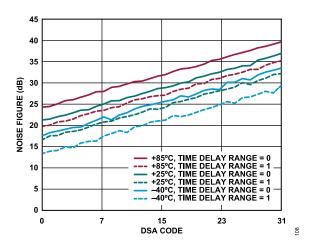

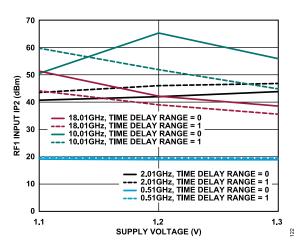

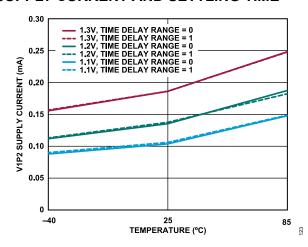

| Voltage Supply and Temperature Sweeps 26       | Ordering Guide                                 | 66 |

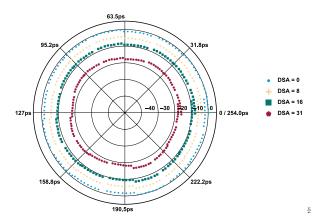

| Polar Plots28                                  | Evaluation Boards                              | 66 |

|                                                |                                                |    |

# **REVISION HISTORY**

6/2025—Revision A: Initial Version

analog.com Rev. A | 2 of 66

# **SPECIFICATIONS**

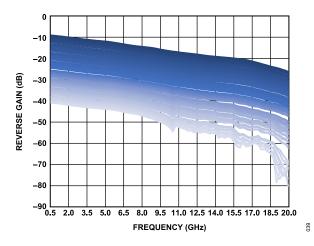

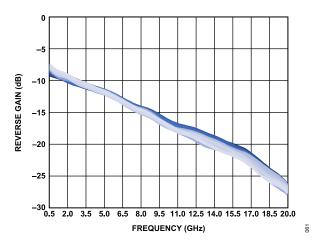

V1P2 = 1.2 V, V1P0 = 1.0 V,  $T_A$  = 25°C, frequency = 10 GHz, TDU code = 0, and DSA code = 0, unless otherwise specified. Input second-order intercept (IP2) has 1 GHz tone spacing. Input third-order intercept (IP3) has 10 MHz tone spacing. Low-side tone reported for IP2. Port 1 = RF1 and Port 2 = RF2. Gain is S21, and reverse gain is S12.

Table 1. Specifications

| Parameter                      | Test Conditions/Comments                 | Min | Тур       | Max | Unit |

|--------------------------------|------------------------------------------|-----|-----------|-----|------|

| OPERATING CONDITIONS           |                                          |     |           |     |      |

| Minimum Frequency              |                                          |     | 500       |     | MHz  |

| Maximum Frequency              |                                          |     | 19        |     | GHz  |

| Operating Temperature          |                                          | -40 |           | +85 | °C   |

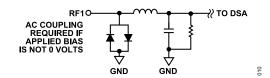

| RF SECTION                     | RF1 and RF2                              |     |           |     |      |

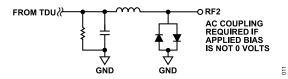

| DC Bias Voltage                |                                          |     | 01        |     | V    |

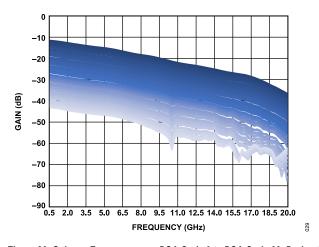

| Insertion Loss                 |                                          |     |           |     |      |

| Time Delay Range 0             | 500 MHz                                  |     | -11.5     |     | dB   |

|                                | 2 GHz                                    |     | -12.6     |     | dB   |

|                                | 10 GHz                                   |     | -20.5     |     | dB   |

|                                | 18 GHz                                   |     | -30.8     |     | dB   |

| Time Delay Range 1             | 500 MHz                                  |     | -9.3      |     | dB   |

| , 3                            | 2 GHz                                    |     | -10.1     |     | dB   |

|                                | 10 GHz                                   |     | -16.2     |     | dB   |

|                                | 18 GHz                                   |     | -22.9     |     | dB   |

| Attenuation Range              | 2 GHz, either time delay range           |     | 31.5      |     | dB   |

| Attenuation Resolution         | 2 or 12, order time delay range          |     | 0.5       |     | dB   |

| Gain Flatness vs. Frequency    | From 2 GHz to 18 GHz, across any 500 MHz |     | 0.0       |     | \ \  |

| Odin'r Iddio35 vs. i Toquency  | bandwidth                                |     |           |     |      |

|                                | Time Delay Range 0                       |     | ≤1.2      |     | dB   |

|                                | Time Delay Range 1                       |     | ≤0.8      |     | dB   |

| Gain Variation vs. Temperature | 10 GHz                                   |     |           |     | dB   |

| 1                              | Time Delay Range 0                       |     | +1.6/-2   |     | dB   |

|                                | Time Delay Range 1                       |     | +1.6/-1.8 |     | dB   |

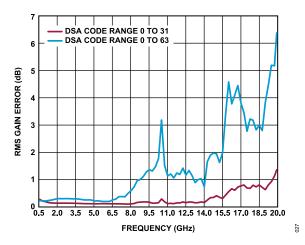

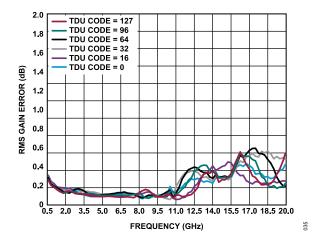

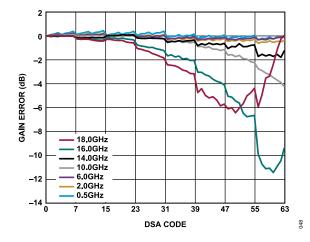

| RMS Gain Error <sup>2</sup>    | , ,                                      |     |           |     |      |

| Time Delay Range 0             |                                          |     |           |     |      |

| 500 MHz                        | DSA Sweep 0 to 15.5 dB                   |     | 0.25      |     | dB   |

|                                | DSA Sweep 0 to 31.5 dB                   |     | 0.2       |     | dB   |

| 2 GHz                          | DSA Sweep 0 to 15.5 dB                   |     | 0.11      |     | dB   |

|                                | DSA Sweep 0 to 31.5 dB                   |     | 0.28      |     | dB   |

| 10 GHz                         | DSA Sweep 0 to 15.5 dB                   |     | 0.11      |     | dB   |

|                                | DSA Sweep 0 to 31.5 dB                   |     | 1.45      |     | dB   |

| 18 GHz                         | DSA Sweep 0 to 15.5 dB                   |     | 0.77      |     | dB   |

|                                | DSA Sweep 0 to 31.5 dB                   |     | 3.16      |     | dB   |

| Time Delay Range 1             | •                                        |     |           |     |      |

| 500 MHz                        | DSA Sweep 0 to 15.5 dB                   |     | 0.3       |     | dB   |

|                                | DSA Sweep 0 to 31.5 dB                   |     | 0.23      |     | dB   |

| 2 GHz                          | DSA Sweep 0 to 15.5 dB                   |     | 0.16      |     | dB   |

|                                | DSA Sweep 0 to 31.5 dB                   |     | 0.24      |     | dB   |

| 10 GHz                         | DSA Sweep 0 to 15.5 dB                   |     | 0.08      |     | dB   |

|                                | DSA Sweep 0 to 31.5 dB                   |     | 1.3       |     | dB   |

| 18 GHz                         | DSA Sweep 0 to 15.5 dB                   |     | 0.32      |     | dB   |

|                                | DSA Sweep 0 to 31.5 dB                   |     | 3.4       |     | dB   |

analog.com Rev. A | 3 of 66

# **SPECIFICATIONS**

Table 1. Specifications (Continued)

| arameter                    | Test Conditions/Comments | Min | Тур Мах | Unit    |

|-----------------------------|--------------------------|-----|---------|---------|

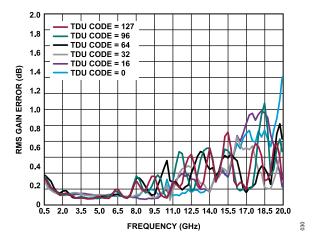

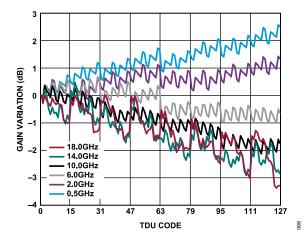

| RMS Gain Variation          |                          |     |         |         |

| Time Delay Range 0          |                          |     |         |         |

| 500 MHz                     | TDU Sweep 0 to 127       |     | 1.45    | dB      |

| 2 GHz                       | TDU Sweep 0 to 127       |     | 0.72    | dB      |

| 10 GHz                      | TDU Sweep 0 to 127       |     | 1.43    | dB      |

| 18 GHz                      | TDU Sweep 0 to 127       |     | 1.52    | dB      |

| Time Delay Range 1          | · ·                      |     |         |         |

| 500 MHz                     | TDU Sweep 0 to 127       |     | 0.98    | dB      |

| 2 GHz                       | TDU Sweep 0 to 127       |     | 0.53    | dB      |

| 10 GHz                      | TDU Sweep 0 to 127       |     | 0.46    | dB      |

| 18 GHz                      | TDU Sweep 0 to 127       |     | 1.12    | dB      |

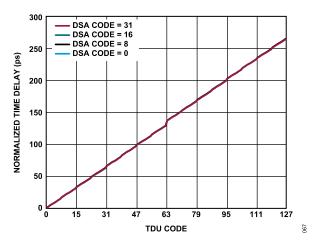

| Time Delay Adjustment Range | 120 011000 0 10 121      |     | 2       | 45      |

| Time Delay Range 0          |                          |     |         |         |

| Time Delay                  | 500 MHz                  |     | 543.5   | ps      |

| Time Belay                  | 2 GHz                    |     | 512.5   | ps      |

|                             | 10 GHz                   |     | 531.2   | ps      |

|                             | 18 GHz                   |     | 516.3   | ps      |

| Phase <sup>3</sup>          | 500 MHz                  |     | 97.83   |         |

| Pilase                      |                          |     |         | Degrees |

|                             | 2 GHz                    |     | 369     | Degrees |

|                             | 10 GHz                   |     | 1921.32 | Degrees |

|                             | 18 GHz                   |     | 3345.6  | Degrees |

| Time Delay Range 1          |                          |     |         |         |

| Time Delay                  | 500 MHz                  |     | 276.2   | ps      |

|                             | 2 GHz                    |     | 254.7   | ps      |

|                             | 10 GHz                   |     | 264.8   | ps      |

|                             | 18 GHz                   |     | 260.9   | ps      |

| Phase                       | 500 MHz                  |     | 49.7    | Degrees |

|                             | 2 GHz                    |     | 183.4   | Degrees |

|                             | 10 GHz                   |     | 953.3   | Degrees |

|                             | 18 GHz                   |     | 1690.6  | Degrees |

| Time Delay Resolution       |                          |     |         |         |

| Time Delay Range 0          |                          |     |         |         |

| Time Delay                  | 500 MHz                  |     | 4       | ps      |

| •                           | 2 GHz                    |     | 4       | ps      |

|                             | 10 GHz                   |     | 4.15    | ps      |

|                             | 18 GHz                   |     | 4.06    | ps      |

| Phase                       | 500 MHz                  |     | 0.72    | Degrees |

|                             | 2 GHz                    |     | 2.88    | Degrees |

|                             | 10 GHz                   |     | 14.4    | Degrees |

|                             | 18 GHz                   |     | 25.92   | Degrees |

| Time Delay Range 1          | 10 0.12                  |     |         | 209.000 |

| Time Delay                  | 500 MHz                  |     | 2       | ps      |

| Time Belay                  | 2 GHz                    |     | 2       |         |

|                             | 10 GHz                   |     | 2.1     | ps      |

|                             | 18 GHz                   |     | 2.1     | ps      |

| Dhaca                       |                          |     |         | ps      |

| Phase                       | 500 MHz                  |     | 0.36    | Degrees |

|                             | 2 GHz                    |     | 1.44    | Degrees |

|                             | 10 GHz                   |     | 7.2     | Degrees |

|                             | 18 GHz                   |     | 12.96   | Degrees |

analog.com Rev. A | 4 of 66

# **SPECIFICATIONS**

Table 1. Specifications (Continued)

| arameter                          | Test Conditions/Comments     | Min Typ | Max Unit |

|-----------------------------------|------------------------------|---------|----------|

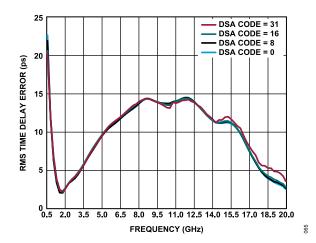

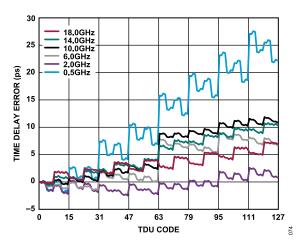

| RMS Time Delay Error <sup>4</sup> |                              |         |          |

| Time Delay Range 0                |                              |         |          |

| 500 MHz                           | TDU Sweep 0 to TDU Sweep 127 | 22.59   | ps       |

| 2 GHz                             | TDU Sweep 0 to TDU Sweep 127 | 2.58    | ps       |

| 10 GHz                            | TDU Sweep 0 to TDU Sweep 127 | 13.68   | ps       |

| 18 GHz                            | TDU Sweep 0 to TDU Sweep 127 | 4.83    | ps       |

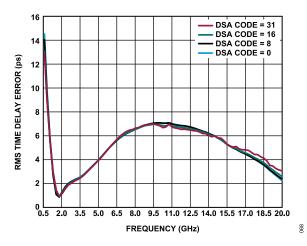

| Time Delay Range 1                |                              |         | ľ        |

| 500 MHz                           | TDU Sweep 0 to TDU Sweep 127 | 14.56   | ps       |

| 2 GHz                             | TDU Sweep 0 to TDU Sweep 127 | 1.15    | ps       |

| 10 GHz                            | TDU Sweep 0 to TDU Sweep 127 | 7.1     | ps       |

| 18 GHz                            | TDU Sweep 0 to TDU Sweep 127 | 4.04    | ps       |

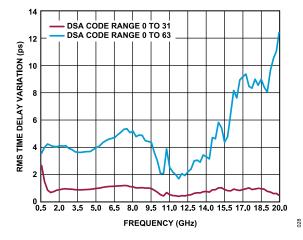

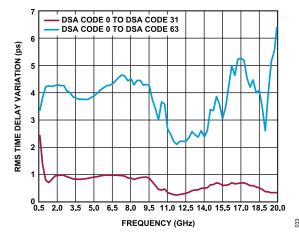

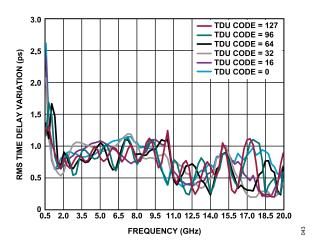

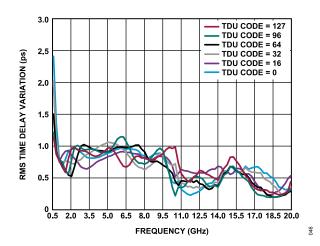

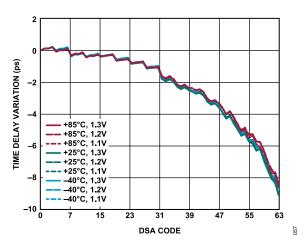

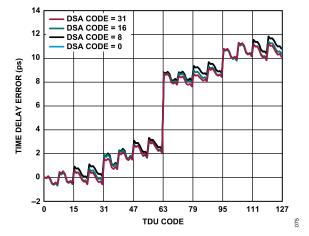

| RMS Time Delay Variation          |                              |         |          |

| Time Delay Range 0                |                              |         |          |

| 500 MHz                           | DSA sweep, 0 dB to 15.5 dB   | 2.62    | ps       |

|                                   | DSA sweep, 0 dB to 31.5 dB   | 3.52    | ps       |

| 2 GHz                             | DSA sweep, 0 dB to 15.5 dB   | 0.84    | ps       |

| _ 3                               | DSA sweep, 0 dB to 31.5 dB   | 4.1     | ps       |

| 10 GHz                            | DSA sweep, 0 dB to 15.5 dB   | 0.65    | ps       |

| 10 0112                           | DSA sweep, 0 dB to 31.5 dB   | 2.95    | ps       |

| 18 GHz                            | DSA sweep, 0 dB to 15.5 dB   | 0.89    | ps       |

| 10 0112                           | DSA sweep, 0 dB to 31.5 dB   | 8.97    | ps       |

| Time Delay Range 1                | BOA SWEEP, 0 db to 51.5 db   | 0.37    | po       |

| 500 MHz                           | DSA sweep, 0 dB to 15.5 dB   | 2.41    | ps       |

| 300 WH 12                         | DSA sweep, 0 dB to 31.5 dB   | 3.34    |          |

| 2 GHz                             | DSA sweep, 0 dB to 31.5 dB   | 0.94    | ps       |

| 2 0112                            | DSA sweep, 0 dB to 10.5 dB   | 4.28    | ps       |

| 10 GHz                            | DSA sweep, 0 dB to 31.5 dB   | 0.57    | ps       |

| 10 GHZ                            |                              | 3.4     | ps       |

| 18 GHz                            | DSA sweep, 0 dB to 31.5 dB   |         | ps       |

| 10 GHZ                            | DSA sweep, 0 dB to 15.5 dB   | 0.57    | ps       |

| Naiss Figure 5                    | DSA sweep, 0 dB to 31.5 dB   | 4.46    | ps       |

| Noise Figure <sup>5</sup>         | 500 MH-                      | 44.4    | AD.      |

| Time Delay Range 0                | 500 MHz                      | 11.4    | dB       |

|                                   | 2 GHz                        | 12.77   | dB       |

|                                   | 10 GHz                       | 21.2    | dB       |

| T                                 | 18 GHz                       | 32      | dB       |

| Time Delay Range 1                | 500 MHz                      | 9.1     | dB       |

|                                   | 2 GHz                        | 10.4    | dB       |

|                                   | 10 GHz                       | 16.6    | dB       |

|                                   | 18 GHz                       | 24.4    | dB       |

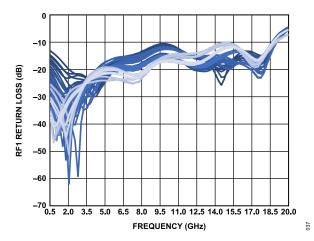

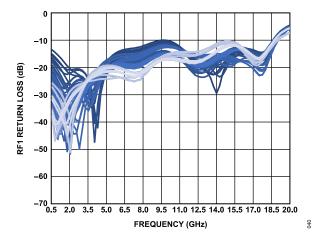

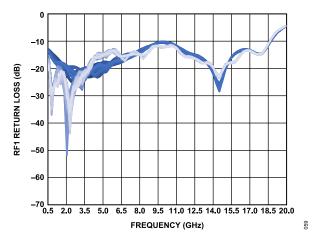

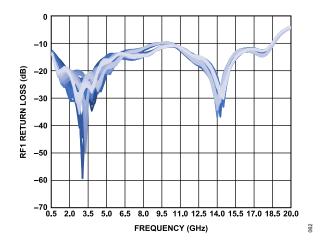

| Input Return Loss                 | RF1                          |         |          |

| Time Delay Range 0                | 500 MHz                      | -13.5   | dB       |

|                                   | 2 GHz                        | -20.2   | dB       |

|                                   | 10 GHz                       | -10.4   | dB       |

|                                   | 18 GHz                       | -14.7   | dB       |

| Time Delay Range 1                | 500 MHz                      | -13.3   | dB       |

|                                   | 2 GHz                        | -20.7   | dB       |

|                                   | 10 GHz                       | -10.1   | dB       |

|                                   | 18 GHz                       | -14.1   | dB       |

analog.com Rev. A | 5 of 66

# **SPECIFICATIONS**

Table 1. Specifications (Continued)

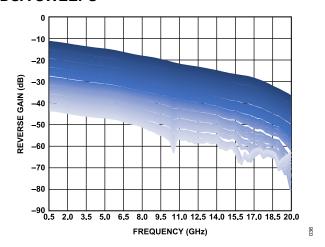

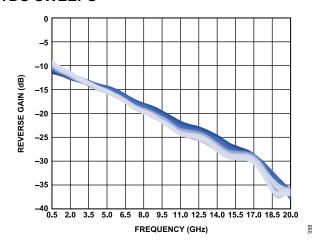

| Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Test Conditions/Comments                                                              | Min               | Тур   | Max               | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-------------------|-------|-------------------|------|

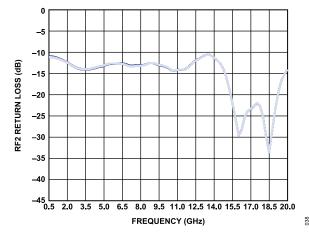

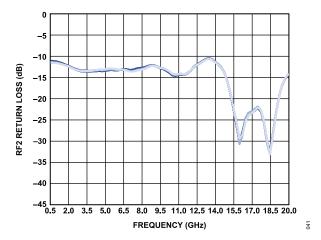

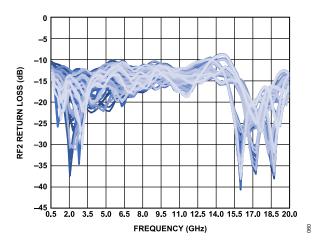

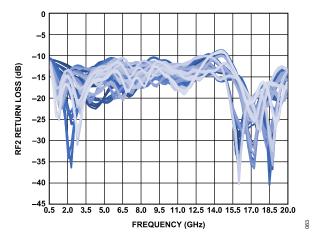

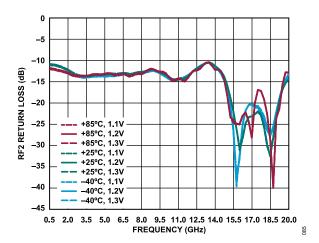

| Output Return Loss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | RF2                                                                                   |                   |       |                   |      |

| Time Delay Range 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 500 MHz                                                                               |                   | -10.9 |                   | dB   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2 GHz                                                                                 |                   | -12.6 |                   | dB   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 10 GHz                                                                                |                   | -13.2 |                   | dB   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 18 GHz                                                                                |                   | -25.4 |                   | dB   |

| Time Delay Range 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 500 MHz                                                                               |                   | -11.2 |                   | dB   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2 GHz                                                                                 |                   | -12.4 |                   | dB   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 10 GHz                                                                                |                   | -13.4 |                   | dB   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 18 GHz                                                                                |                   | -25.2 |                   | dB   |

| Input Third-Order Intercept (IP3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | RF1                                                                                   |                   |       |                   |      |

| Time Delay Range 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 500 MHz                                                                               |                   | 8.6   |                   | dBm  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2 GHz                                                                                 |                   | 10.6  |                   | dBm  |