Mixed Signal Front Ends (MxFE)

Mixed-signal front-end (MxFE®) products from Analog Devices offer a smart integration of RF analog-to-digital converters (ADCs), RF digital-to-analog converters (DACs), on-chip digital signal processi

Go to Product Selection Table

Viewing:

Products in Category

ADSY1100

PRE-RELEASE

4 Tx/4 Rx, 0.1 GHz to 20 GHz Apollo MxFE 3UVPX Tuner + Digitizer + Processor

AD9088

RECOMMENDED FOR NEW DESIGNS

Apollo MxFE Octal, 16-Bit, 16 GSPS RF DAC and Octal, 12-Bit, 8 GSPS RF ADC

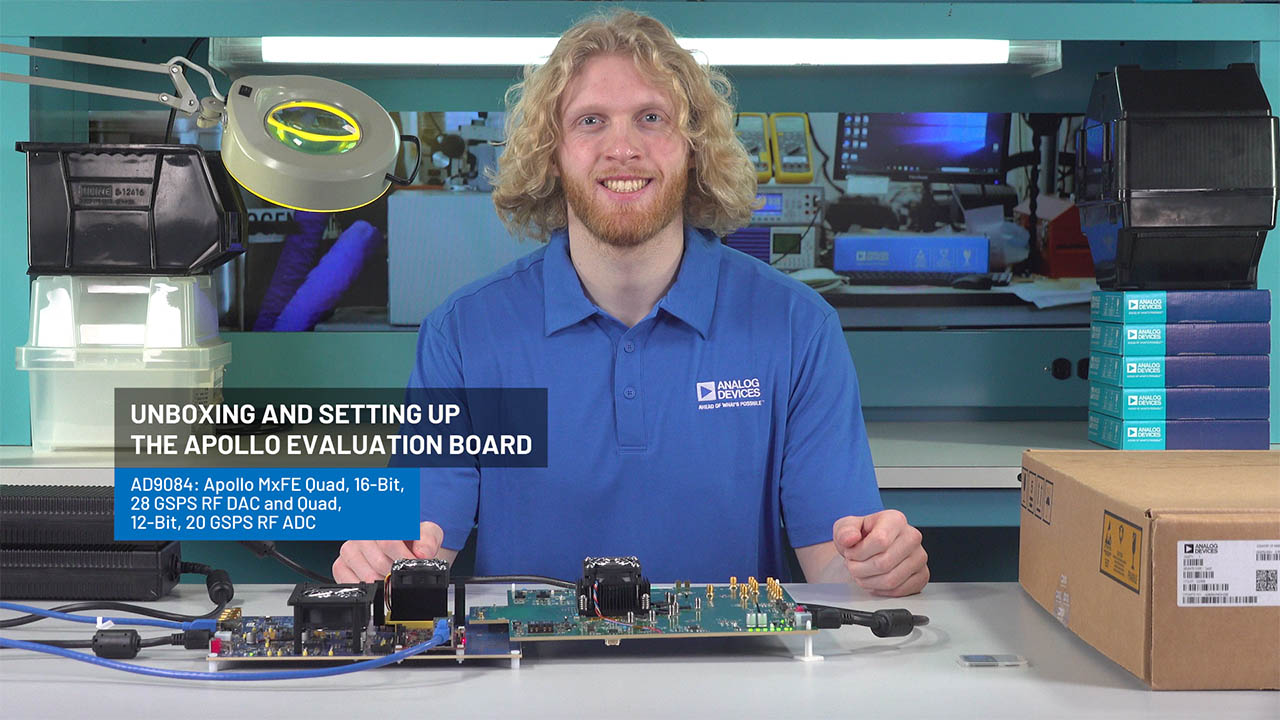

AD9084

RECOMMENDED FOR NEW DESIGNS

Apollo MxFE Quad, 16-Bit, 28GSPS RF DAC and Quad, 12-Bit, 20 GSPS RF ADC

AD9986

RECOMMENDED FOR NEW DESIGNS

4T2R Direct RF Transmitter and Observation Receiver

AD9988

RECOMMENDED FOR NEW DESIGNS

4T4R Direct RF Receiver and Transmitter

AD9081

RECOMMENDED FOR NEW DESIGNS

MxFE™ Quad, 16-Bit, 12GSPS RFDAC and Quad, 12-Bit, 4GSPS RFADC

AD9082

RECOMMENDED FOR NEW DESIGNS

MxFE Quad, 16-Bit, 12 GSPS RF DAC and Dual, 12-Bit, 6 GSPS RF ADC

AD9963

RECOMMENDED FOR NEW DESIGNS

10-/12-Bit, Low Power, Broadband MxFE

AD9961

RECOMMENDED FOR NEW DESIGNS

10-/12-Bit, Low Power, Broadband MxFE

AD9878

PRODUCTION

Low Cost, 3.3 V, CMOS Mixed Signal Front End (MxFE®) for Broadband Applications

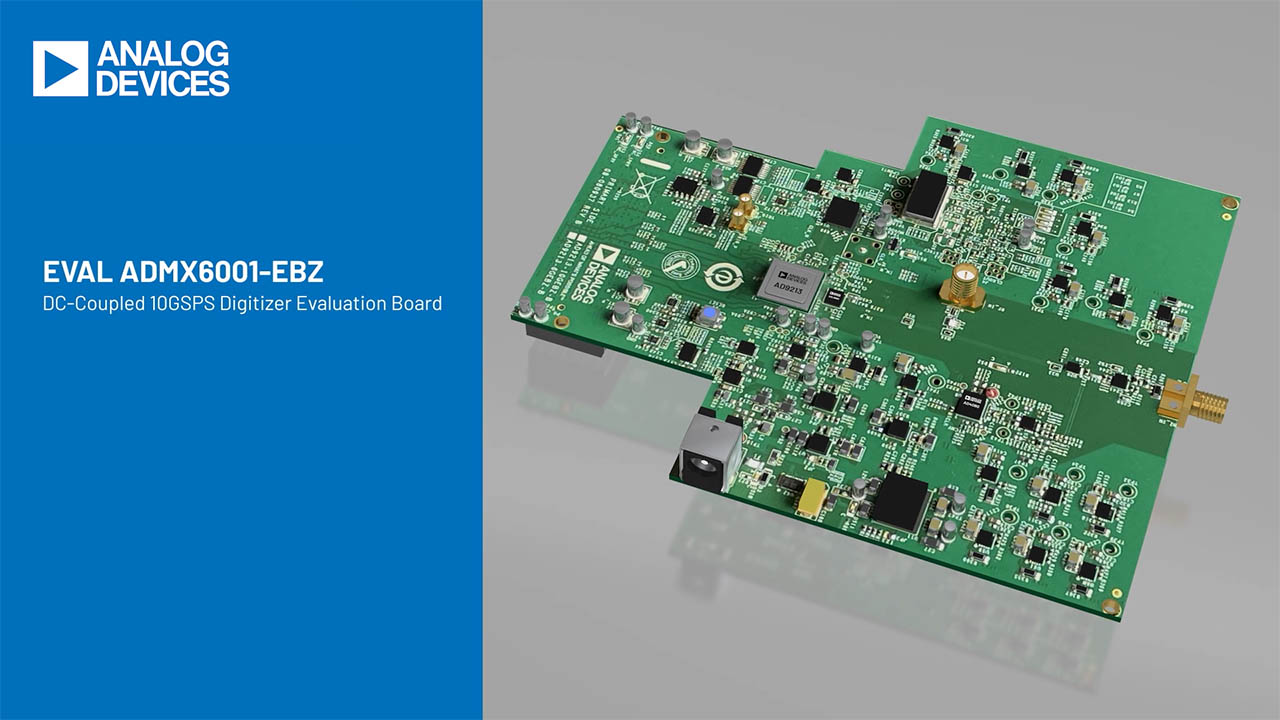

{{modalTitle}}

{{modalDescription}}

{{dropdownTitle}}

- {{defaultSelectedText}} {{#each projectNames}}

- {{name}} {{/each}} {{#if newProjectText}}

-

{{newProjectText}}

{{/if}}

{{newProjectTitle}}

{{projectNameErrorText}}