AN-1464: AD7172-2、AD7172-4、AD7173-8、AD7175-2、AD7175-8、AD7176-2、AD7177-2、AD7124-4、AD7124-8 の補正

はじめに

アナログ・デバイセズ製の高精度シグマ・デルタ(Σ-Δ)製品には、オンチップ補正が組み込まれており、内部補正とシステム補正の両方をサポートしています。Σ-Δ 製品はシステム、ゲイン、内部リファレンスで必要になる多数の構成ブロックを内蔵しています。内部補正により、内部オフセット誤差とゲイン誤差が最低限に抑えられます。デバイスで使用される補正方法により、すべての内部ブロックのオフセットとゲイン誤差が補正されます。例えば、ゲイン段の誤差は補正されます。

システムのオフセット誤差とゲイン誤差の補正はコンバータによってサポートされています。ここで、外付け部品は内部誤差のソースと一緒に A/D コンバータ(ADC)によって補正されます。

このアプリケーション・ノートでは、AD7172-2、AD7172-4、AD7173-8、AD7175-2、AD7175-8、AD7176-2、AD7177-2、AD7124-4、AD7124-8 で使用される補正方法について詳細に説明します。

オフセット誤差とゲイン誤差

このアプリケーション・ノートで説明する ADC では、ユニポーラおよびバイポーラ・モードの両方の動作が可能です。ここでは、ユニポーラ・モードと一緒にオフセット誤差とゲイン誤差について説明します。

ADC コードが 000 の場合の電圧の理想値からの偏差がオフセット誤差になります。図 1 に、ADC の伝達関数を示します。

図 1. ADC の伝達関数

ADC のゲイン誤差は、電圧の理想値からの最大誤差です。この値は最大および最小の入力電圧での誤差です(図 2 を参照)。

図 2. ADC ゲイン誤差

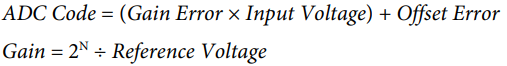

図 2 の ADC 伝達関数は、Y = MX + B の直線式と等しくなります。これは次の式に対応します。

シグナル・チェーン全体のオフセット誤差とゲイン誤差を調整できます。これにより、システムの全体的な精度が向上します。オフセット誤差を調整するには、オフセット補正またはゼロスケール補正を実行します。一方、ゲイン誤差を調整するには、ゲイン補正またはフルスケール補正を実行します。

通常、アナログ - デジタル変換の結果から、変換による誤差の大きさがわかります。補正を実行することで、確実に誤差を調整できます。補正を実行するには、マイクロコントローラ・ユニット(MCU)で定義済みのソフトウェアを使用します。補正係数はMCU メモリに保存されています。これらの補正係数により、ADC変換の結果がスケーリングされ、ゲインとオフセットの誤差が除去されます。この手法では、MCU で ADC 変換を後処理して正確な値を取得する必要があるので、時間がかかります。

アナログ・デバイセズの高精度 Σ-Δ ADC ポートフォリオには、ADC 変換結果のゲイン誤差とオフセット誤差を調整できる補正モードが組み込まれています。これらの Σ-Δ ADC は、補正係数を保存するためのオンチップ・レジスタを備えています。

これらの係数は、ADC 変換結果のゲイン誤差とオフセット誤差の両方を自動的に補正します。変換結果からオフセット補正係数を減算してから、ゲイン誤差係数で乗算します。

補正モード

AD7124-4、AD7124-8、AD7172-2、AD7172-4、AD7173-8、AD7175-2、AD7175-8, AD7176-2、AD7177-2 Σ-Δ ADC は、同様の方法で補正を実行します。

AD7124-4 およびAD7124-8 は、低消費電力の Σ-Δ ADC ファミリーで、高精度の測定アプリケーションで使用するフル機能のアナログ・フロント・エンドが内蔵されています。AD7124-4 およびAD7124-8 では、次の 4 つの補正モードをサポートしています。

- 内部ゼロスケール補正

- 内部フルスケール補正

- システム・ゼロスケール補正

- システム・フルスケール補正

AD7172-2、AD7172-4、AD7173-8、AD7175-2、AD7175-8、AD7176-2、AD7177-2 は低ノイズ、高速セトリング、マルチプレクス型 Σ-ΔADC で、次の 3 つの補正モードをサポートします。

- 内部ゼロスケール補正

- システム・ゼロスケール補正

- システム・フルスケール補正

これらの補正モードは、ソフトウェアでプログラムでき、AD7124-4およびAD7124-8 では ADC_CONTROL レジスタからアクセスでき、AD7172-2、AD7172-4、AD7173-8、AD7175-2、AD7175-8、AD7176-2、AD7177-2 では ADC モード・レジスタからアクセスできます。

オフセット(ゼロスケール)とゲイン(フルスケール)補正は、既知のアナログ入力を使用した変換です。すべての場合で、補正が開始すると RDY がハイになり、補正が完了するとローに戻ります。

内部ゼロスケールのオフセット補正

内部ゼロスケールのオフセット補正では、自動的に選択した正のアナログ入力ピンが切断され、選択した負のアナログ入力ピンに内部で接続されます。このため、選択した負のアナログ入力ピンの電圧が許容値を超えることはなく、過度なノイズや干渉は発生しません。図 3 に、内部接続、正アナログ入力(AINP)、負アナログ入力(AINM)のブロック図を示します。

図 3. 内部ゼロスケールのオフセット補正

システム・ゼロスケールのオフセット補正

システム・ゼロスケールのオフセット補正では、補正電圧を ADCピンに入力する必要があります。このタイプの補正では、外部回路のオフセットと ADC オフセットがシグナル・チェーンから除去されます。例えば、入力モジュールでは、コネクタ端子で入力を短絡し、シグナル・コンディショニングと ADC オフセットの誤差を補正することで除去できます。図 4 に、EVAL-AD7124-4SDZ評価用ボードで AIN0 と AIN1 を互いに短絡させるセットアップを示します。EVAL-AD7124-4SDZ は、ADP1720 によって駆動され、ADR4525 をリファレンスとして使用し、EVAL-SDP-CB1Z を評価用コントローラ・ボードとして使用します。EVAL-SDP-CB1Zは ADSP-BF527 プロセッサをベースにしています。

図 4. EVAL-AD7124-4SDZ 評価用ボードのシステム・ゼロスケール補正のセットアップ

EVAL-AD7124-4SDZ 評価用ボードおよびAD7124-4/AD7124-8 Eval+ ソフトウェアが使用されています。AD7124-4 は次のように構成されています。

- チャンネル:AIN0 と AIN1

- 評価用ボードでは、LK5 を使用して ピン AIN0 とピン AIN1が短絡されています

- VBIAS はイネーブル

- Gain = 2

- 電力モード: 通常消費電力モード

- 出力データ・レート:50 SPS

図 5 に、AD7124-4 の補正前の結果および AIN0 と AIN1 を短絡して補正した後の結果を示します。外部オブセット補正の実行後、オフセット誤差は減少し、変換結果は約 0 V になります。ADC の変換結果は、0x7FFF60 または補正なしの 24 μV オフセットを示します。詳細については、AD7124-4 のデータシートを参照してください。

図 5. 補正なしの結果とシステム・ゼロスケール補正後の結果

低消費電力モードでは、システム・ゼロスケール補正の実行後に、オフセット・レジスタが 0x7FFF89 に更新されます。変換を実行すると、ADC の結果は 0x7FFFFC(約 120 nV 平均)になります。この値は、ノイズとほぼ同等の約 330 nV RMS になります。

内部フルスケールのゲイン補正

内部フルスケールのゲイン補正を実行すると、フルスケールに近い入力電圧を選択したアナログ入力に自動的に接続されます。

AD7124-4 とAD7124-8 は抵抗ネットワークを備えているので、ADC は VREF ÷ ゲインの大きさの信号を生成できます。このため、デバイスは各ゲインで内部フルスケール補正をサポートできます。

通常消費電力モードに設定されたAD7124-4 およびAD7124-8 では、内部フルスケール(ゲイン)補正を実行できません。低消費電力または中消費電力モードを使用してください。低消費電力または中消費電力モードで内部フルスケール補正を実行し、変換中に通常消費電力モードに切り替えることはできます。同じリファレンスとゲインを使用する場合は、補正係数が引き続き適用されます。

システム・フルスケールのゲイン補正

システム・レベルのフルスケール・ゲイン補正では、入力にフルスケール電圧をかける必要があります。このタイプの補正の結果では、ADC 外部のゲイン誤差と ADC のゲイン誤差を削減できます。例として入力モジュールを使用すると、補正中にフルスケール信号は ADC 入力ではなくモジュール入力に適用され、モジュール全体のゲイン誤差が補正されます。図 6 は、EVAL-AD7124-4SDZ評価用ボードを使用したAD7124-4 のシステム・フルスケール補正のブロック図です。システム・フルスケール補正を実行するには、AIN0(ゲイン = 2 で 1.25 V)にフルスケール電圧をかけ、AIN1 を AVSS に接続します。

図 6. EVAL-AD7124-4SDZ システム・フルスケール補正のセットアップ

図 7 に、AD7124-4 およびAD7124-8 のシステム・ゲイン補正ルーチンの性能を示します。この場合も、EVAL-AD7124-4SDZ 評価用ボードとソフトウェアが使用され、AD7124-4 は次のように構成されます。

- チャンネル:AIN0 と AIN1

- バイポーラ・モード

- Gain = 2

- 電力モード: 通常消費電力モード

- 出力データ・レート:50 SPS

AIN1 を AVSS に接続し、コネクタ J6 経由で AIN0 に 1.25 V の電圧をかけます。補正前に、0xFF13C(16,744,765)の ADC 出力コードを生成します。

図 7. EVAL-AD7124-4SDZ の補正なしとシステム・フルスケール補正後の比較

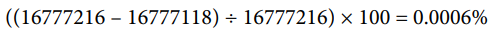

システム・フルスケール補正の後、ゲイン・レジスタは 0x55A2D3に更新されます。同じ入力電圧を使用した場合の ADC 平均結果は 0xFFFF9D(16,777,118)になります。そのため、結果のゲイン誤差は次のように低減します。

工場出荷時の補正値

オフセット・レジスタのデフォルト値は 0x800000 で、ゲイン・レジスタの公称値は 0x5XXXXX です。ゲイン誤差は、ゲイン 1 で出荷時に補正されています。そのため、AD7124-4、AD7124-8、AD7172-2、AD7172-4、AD7173-8、AD7175-2、AD7175-8、AD7176-2、AD7177-2 にはデフォルトのゲイン係数が設定されていますが、デバイスごとに値が異なります。AD7124-4 およびAD7124-8 は、ゲイン 1 の内部フルスケール補正をサポートしていません。

システム補正電圧

AD7124-4、AD7124-8、AD7172-2、AD7172-4、AD7173-8、AD7175-2、AD7175-8、AD7176-2、AD7177-2 の入力範囲は、0.8 × VREF ÷ ゲインから 2.1 × VREF ÷ ゲインです(AD7124-4 および AD7124-8 ではゲイン 1~ 128、AD7172-2、AD7172-4、AD7173-8、AD7175-2、AD7175-8、AD7176-2、および AD7177-2 ではゲイン = 1)。そのため、ユーザーは入力範囲を調整できます。ADC 入力範囲を使用できない設計もあるので便利です。例えば、センサーからの信号振幅は ADC の許容入力範囲の 95 % までです。この場合、(0.95 ×VREF ÷ ゲイン)の入力信号を ADC に適用できます。ADC は、この信号強度を使用してシステム・フルスケール補正を実行します。

補正の実行

補正は、AD7124-4、AD7124-8 の場合は ADC_CONTROL レジスタの ADC モード・ビットに何かを書き込むか、AD7172-2、AD7172-4、AD7173-8、AD7175-2、AD7176-2、AD7177-2 の場合は、ADC モード・レジスタ内の MODE ビットに所定の値を書き込むことにより開始されます。補正を開始すると、DOUT/RDY ピン、およびステータス・レジスタの RDY ビットがハイ・レベルになります。必要な補正が完了すると、対応するオフセットまたはゲイン・レジスタの内容が更新され、ステータス・レジスタの RDY ビットがローになり、DOUT/RDY ピンがローに戻ります(CS がローの場合)。このため、RDY 立下がりエッジまたは RDY ステータス・ビットによって補正の終了が通知されるので、補正時間を監視する必要はありません。

補正の順序は、ADC によって異なります。AD7172-2、AD7172-4、AD7173-8、AD7175-2、AD7175-8、AD7176-2、AD7177-2 でオフセットとゲインの両方を補正する場合、ゼロスケール補正を実行してからフルスケール補正を実行します。

AD7124-4 および AD7124-8 では、オフセット・レジスタが 0x800000のデフォルト値の場合のみ、内部フルスケール補正を実行できます。そのため、内部ゼロスケールと内部フルスケールの両方を補正する場合、次のルーチンが推奨されます。

- オフセット・レジスタを 0x800000 にリセットします。

- 内部フルスケール補正を実行します。

- 内部ゼロスケール補正を実行します。

システム・ゼロスケール補正は、システム・フルスケール補正の前に実行する必要があります。

すべての補正において、選択されたフィルタのセトリング・タイムと出力データ・レートが整定するまでの時間が必要です。内部フルスケール補正は例外です。この場合、ゲイン 1 では 1 つのセトリング期間、1 より大きい ゲインでは、4 つのセトリング期間が必要です。

AD7124-4 および AD7124-8 では、低消費電力モードまたは中消費電力モードのみで補正がサポートされます。

ゲイン誤差とオフセット誤差の補正は、どちらも任意のゲインまたは出力データ・レートで実行できます。補正は既知のアナログ入力を使用した変換です。ただし、低出力データ・レートで補正することを推奨します。低出力データ・レートではノイズが低く、AD7124-4、AD7124-8、AD7172-2、AD7172-4、AD7173-8、AD7175-2、AD7175-8、AD7176-2、AD7177-2 の性能は最高になります。取得される補正係数は、任意の出力データ・レートで使用されます。

補正係数の使用

ADC 出力コードは、AD7124-4、AD7124-8、AD7172-2、AD7172-4、AD7173-8、AD7175-2、AD7175-8、AD7176-2、AD7177-2 のアナログ入力電圧を示します。両方のファミリーで、オフセット・バイナリ・コードが使用されます。

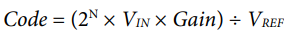

このため、ユニポーラ操作における理想的な関係は次のようになります。

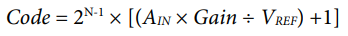

バイポーラ動作では、次式のようになります。

ここで、

N = 24、ビット数(分解能)。

NIN はアナログ入力電圧。

VREF はリファレンス電圧。

Gain はゲイン設定です(AD7124-4 および AD7124-8 では 1 ~ 128、AD7172-2、AD7172-4、AD7173-8、AD7175-2、AD7175-8、AD7176-2、AD7177-2 では 1)。

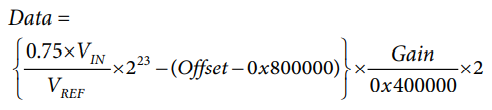

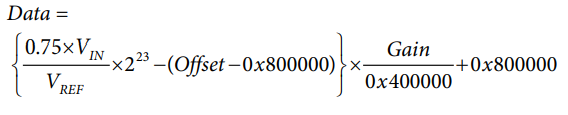

オフセットとゲインの補正を ADC 変換結果に含める必要があるので、実際の ADC 出力コーディングは若干異なります。

ユニポーラ・モードの関係は

バイポーラ・モードの関係は

ここで、

Offset はオフセット係数

Gain はゲイン係数

これらの式では、オフセット係数とゲイン係数を使用して、ADC デジタル出力をスケールリングします。

サンプリングされたアナログ入力は、ADC 内で 25 % 低減されます。このスケーリングは、フルスケール信号が Σ-Δ 変調器に印加されないよう、つまり変調器が飽和しないように実行されます。全体的な計算で、減衰量は(ゲイン ÷ 0x400000)の単位で補正されます。

CN-0381 には、AD7124-8 でゲインとオフセットの補正を実行すると、精度が向上することが示されています。

図 8 に CN-0381 の回路図を示します。このシステムでは、AD7124-8と ADC に接続された Pt100 温度センサーの測温抵抗体(RTD)を使用しています。センサーの直線化は、ADC 変換によって実行されます。

図 8. CN-0381 の回路図

室温で動作する AD7124-8 を使用して −50 °C ~ +150 °C の温度範囲で RTD の温度を掃引すると、デフォルトのゲイン係数とオフセット係数を使用している場合、結果の精度が予想される範囲外になります。

ただし、25 °C で内部オフセットとゲインの補正を 1 回実行すると、精度が向上し、システムの変換結果は Pt100 RTD で想定されるプロファイルに収まります。図 9 に、AD7124-8 を使用した Pt100RTD センサーの結果を示します。

図 9. AD7124-8 補正あり/なし、Pt100 プロファイル各温度に対する強制値と測定値の差、Pt100 クラス Bの精度と温度の関係

補正を実行するタイミング

補正はパワーアップ後に実行する必要があります。そのため、初期化ルーチンの実行時に使用する各チャンネルを選択し、チャンネルを構成する必要があります。例えば、リファレンス・ソースを選択してゲインを設定します。オフセットとゲインの補正をチャンネルで実行する必要があります。補正を実行する場合は、1 つのチャンネルのみをイネーブルにします。複数のチャンネルがイネーブルの場合、ADC は、シーケンスの最初のチャンネルのみを補正します。ゲイン値を変更した場合は、チャンネルを再補正する必要があります。

定期的な補正を実行して、オフセットとゲイン誤差のドリフトを最低限に抑えるのが望ましい場合もあります。このような追加の補正を実行する頻度は、ユーザーのアプリケーションにおける温度変化率によって決定されます。

ただし、AD7124-4、AD7124-8、AD7172-2、AD7172-4、AD7173-8、AD7175-2、AD7175-8、AD7176-2、AD7177-2 のオフセット・ドリフトとゲイン・ドリフトは小さいため、多くのアプリケーションでは、パワーアップ後に補正を 1 回実行するだけで十分です。

通常、ADC ドリフト性能により、オフセット誤差とゲイン誤差を調整するための内部補正が実行されます。CN-0381 には、さまざまな温度範囲で AD7124-8 の内部補正を使用してオフセットおよびゲインの誤差を調整する方法が示されています。

システム補正を実行して、ADC システムのフロント・エンドまたは外部回路で生成されるオフセットとゲインの誤差を補償します。ロード・セルには精度ドリフトが発生するので、重量計アプリケーションでシステム補正を実行するのが最適です。ドリフトに起因する精度を調整するには、システム補正を実行する必要があります。

まとめ

アナログ・デバイセズの Σ-Δ ADC では、ゲイン誤差とオフセット誤差の補正だけでなく、内部補正とシステム・レベルの補正を使用できます。これらの補正オンチップにより、システムの全体的な精度が向上し、サンプルの補正を実装するための条件が不要になり、全体的な設計が簡略化され、時間も節約されます。

参考資料

Kester, Walt2005 年The Data Conversion Handbook.アナログ・デバイセズ第 3 章および第 7 章