概览

设计资源

FPGA/HDL

优势和特点

- 两个完整的无线电

- 2 Tx、2 Rx、2观测

- 多个电源选项

- 壁式连接、以太网供电、电池

- 内置IMU和GPS进行跟踪

- 完全可配置和可定制软件

参考资料

-

CN0412 user Guide Wiki2019/7/31WIKI

-

CN0412:ADRV-PACKRF 便携式无线电设计 (Rev. 0)2019/7/31PDF564 K

电路功能与优势

ADRV-PACKRF套件为软件开发人员、系统架构师、算法开发人员和产品团队提供了一套射频(RF)平台,平台支持宽调谐范围(70 MHz至6 GHz)和宽带宽(200 kHz至56 MHz)。开源硬件设备语言(HDL)和Linux软件可以将平台与MATLAB®、Simulink®或GNU Radio连接起来,将算法部署到内置的现场可编程门阵列(FPGA)中。无线电模块可加速从初始评估和概念到原型、再到现场部署的开发过程。

该无线电模块附带完整的单载波调制解调器参考设计。调制解调器是一种恒常发射的频分双工(FDD)系统,具有1个发射通道(上行链路)和1个接收通道(下行链路),支持两个节点之间实现双向点对点链路。使用此套件中提供的网络摄像头,可以在两个节点之间演示无线视频传输。

无线电位于一个铝制外壳内,外壳支持连接电源、以太网、USB、OLED显示屏、音频和micro SD卡。天线连接到设备背面的SMA,用于发射(Tx)、接收(Rx)、Tx监测和全球定位卫星(GPS)输入/输出。

电路描述

便携式无线电参考设计

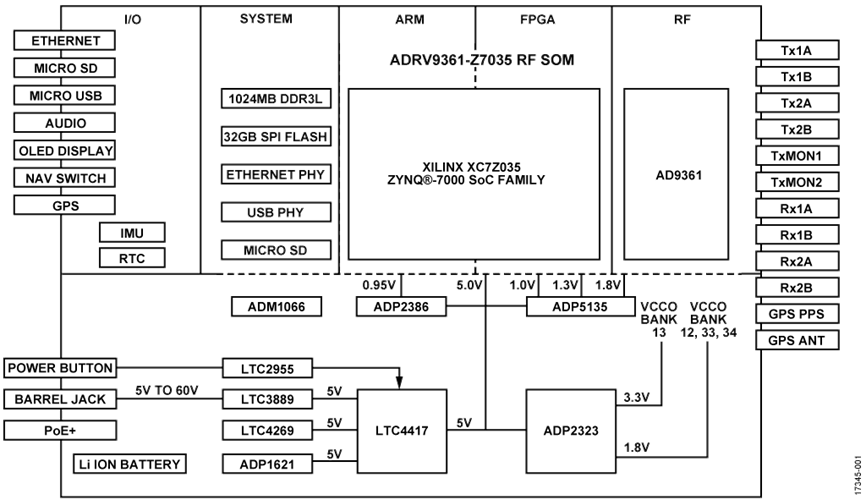

便携式无线电参考设计结合了ADRV9361-Z7035 RF系统化模块(SOM)、定制载板、自动生成的HDL、定制Linux内核及用户空间软件。这种组合为硬件、软件和HDL提供了一个开源的端到端参考设计,形成一个可以建立Linux TCP/IP连接的完整数据链。

该项目还包括一个单载波QPSK调制解调器设计的MATLAB浮点仿真、Simulink浮点模型和的HDL定点模型。它还能与其他SDR设备集成,包括PlutoSDR、FMCOMMS2/3/4和ADRV-PACKRF,以支持实际测试。

所有设计都可以相互进行无线通信,并且可以通过一个通用测试工具进行验证。这些设计共同展示了从仿真到硬件部署的真正开发周期。在脱离了MATLAB或Simulink的情况下,我们也可以通过ADI公司的板级支持包(BSP)创建了一个专用/定制参考设计,并利用ADRV-PACKRF套件演示视频传输。

ADRV9361-Z7035 RF SOM

ADRV9361-Z7035 RF系统化模块(SOM)提供标准化FPGA加收发器平台,以简化无线系统设计和原型制作。该SOM使最终用户无需实现和验证FPGA与转换器之间的复杂连接、DDR3L、USB 2.0 OTG物理层以及10/100/1000以太网物理层。因此,用户可以专注于SOM上的信号处理,设计需要其他硬件的承载卡。

ADRV-PACKRF 承载卡

ADRV-PACKRF内的定制承载卡支持用户连接手持式无线电应用所需的其他硬件外设,比如传感器、电源、实时时钟和其他模拟功能。

多个连接器直接安装在承载卡上,并从ADRV-PACKRF的面板引出,如以太网、micro SD、DC管式插孔、micro USB和音频。

承载卡上的其他接口可连接OLED、导航开关、IMU、ON/OFF按钮和电池。这些模块通过各种电缆连接到承载卡。

SOM通过四个100针连接器连接到承载卡。盒子面板上的SMA通过一系列UFL转SMA电缆直接连接到RF收发器。

电源

承载卡负责为包含ADRV-PACKRF在内的一切器件供电。该系统可以由三种输入电源可供选择:

- 以太网供电(PoE)

- 外部直流电源

- 备用电池

每个输入源产生一个5 V电压轨,能够为所有下游电路提供5 A电流。ADP2323是一款双通道同步降压型稳压器,除了为ADRV9361-Z7035供电外,还能产生3.3 V和1.8 V电源为ADRV-PACKRF承载卡上的外设供电。图5详细显示了整个系统的电源分配。

系统主电源默认为PoE(如存在),然后是外部直流电源,最后才依赖备用电池。如果检测到PoE或外部直流电源,则会为备用电池充电以防断电。

以太网供电

ADRV-PACKRF符合IEEE 802.3at-2009 Type 2以太网供电(PoE+)标准,或Class 4。不要与原来的IEEE 802.3af-2003 PoE标准混淆,后者定义了Class 0到Class 3,为受电设备(PD)提供最高12.95 W的功率。更新的IEEE 802.3at-2009 PoE+标准(PoE+或PoE plus)可为Type 2、Class 4设备提供最高25.5 W的功率。

| 级别 (Class) | 类型 (Type) | PSE 功率 | PD 功率 |

| 0 | 1 (802.3af) | 15.4 W | 0.44 W 至 12.95 W |

| 1 | 1 (802.3af) | 4.0 W | 0.44 W 至 3.84 W |

| 2 | 1 (802.3af) | 7.0 W | 3.84 W 至 6.49 W |

| 3 | 1 (802.3af) | 15.4 W | 6.49 W 至 12.95 W |

| 4 | 2 (802.3at) | 30 W | 12.95 W 至 25.5 W |

带有集成同步反激控制器的LTC4269-1受电设备(PD)可为ADRV-PACKRF提供5 V电源轨。它能处理所有必要的握手操作,只有在连接到Type 2 (25.5 W)或更高功率的供电设备(PSE)以接收电源时才会自行使能。

在操作中,涓流充电电阻RTR连接到VIN,提供一个典型值在1 mA左右的小电流对CTR充电。最初,LTC4269-1处于关闭状态,仅汲取启动电流。当CTR达到VCC导通阈值电压时,LTC4269-1突然导通并汲取正常电源电流。开关动作开始,转换器开始向输出输送电源。输出电压最初为低电平,反激电压也为低电平;因此,CTR提供LTC4269-1的大部分电流(只有一小部分来自RTR)。VCC电压继续下降,直到一段时间(通常为数十毫秒)后,输出电压接近期望值。然后,反激绕组提供LTC4269-1电源电流,VCC电压保持稳定。

如果CTR过小,VCC在稳定前就会达到VCC关断阈值,LTC4269-1将关断。然后,VCC节点开始通过RTR回充,达到导通阈值时,器件再次导通。根据电路具体情况,这可能导致器件在实现正常运行之前发生多次启动-关闭循环,或者在VCC节点处发生永久启动-关闭振荡。

应使CTR足够大,以避免发生上述启动-关闭振荡行为。经验测试是确定CTR最简单的方法;对于ADRV-PACKRF,47 μF电容值是足够的。

外部直流电源

外部直流电源输入为5.5 mm管式插孔,支持LTC3899的宽输入电压范围(4.5 V至60 V),使得无线电可以由多种外部电源供电,包括:

- AC/DC 适配器

- 汽车点烟器适配器

并非所有管式插孔都相同。ADRV-PACKRF需要一个中心为正的导体,内径为2.1 mm,外径为5.5 mm。仔细检查要求:大多数AC/DC适配器的中心都是正极,但有些适配器也会存在中心为负/外管为正的极性。

汽车电源适配器通常有5.5 mm直径的管式插孔,因此适合用作电源。然而,此类电源的一个主要挑战是较新式节能车辆要求电动机冷启动。为达到更高的燃油经济性指标,许多新型汽车都含有自动启停系统,遇到红灯或交通拥堵时发动机会关闭。当发动机重启时,起动电机冷启动电池以使发动机开始工作。为安全起见,电源管理系统在这些启停事件期间不能降低输出电压,在10 ms至100 ms的时间内可能会看到超低电压(约3 V)。

负载突降是一个类似的问题。对于标称12 V车辆,当电池或其他某种相当大的负载意外断开时,汽车交流发电机产生的电压浪涌可能暂时高达60 V。连接到汽车电源的所有电子设备都需要承受此类电压。

备用电池

ADRV-PACKRF内含一个由可充电3200 mAH锂离子电池构成的备用电池。ADP1621升压DC-DC控制器可调节电池电压(典型值为3.7 V)以产生应急电源。备用电池只能在有限的时间内为系统供电。FPGA上的重负载会将备用电池工作时间减少到1小时以下,但该时间完全取决于系统利用率和耗电量。

电池内置保护电路,可检测过充电、过度消耗、短路、过温等情况,以保护电池(和系统)免受损坏。电池可通过另外两种输入电源中充电,本电路笔记稍后会详细介绍。

电池充电

电池充电由ADP5061监控,用户可以设置和修改某些关键变量,包括但不限于以下内容:

- 涓流和快速充电电流水平

- 涓流和快速充电电压阈值

- 输入限流值

- 看门狗时间周期

- 弱电池阈值检测

- 电池温度

设置和修改这些关键变量,确保电池安全稳妥地充电。

当电池电量不足时,系统会对电池充电,但需要将PoE或交流/直流适配器插入无线电以提供电源。这些电压不需要经过电源选择器LTC4417。LTC4415二极管会对这些电压进行"或"运算,为电池充电器IC ADP5061提供专用电源。

LTC4417电源选择器输出电压(5 V)不用于为电池充电IC供电,因为如果这样设计需要开机才能为电池充电。

电池充电维护

保持电池电量对所有电子产品都很重要。必须避免所有形式的电流过度消耗。当电池不产生5.0 V电压时,有一条通过二极管的从+V_Batt到+5V_Batt的路径。这意味着该网络上的任何负载(包括电阻分压器和IC二极管)都会消耗电池电量。在电流路径中放置一个高额定电流的晶体管,便可通过控制信号驱动栅极,以及断开电流路径与负载的连接。当开关关闭时,电池的负载最小。

电源选择

输入电源由LTC4417 Power Path™控制器验证并确定使用优先级。电源按照PoE (V1)、外部直流电源(V2)和备用电池(V3)的物理连接进行排列。

独立验证每个输入电压,将其与欠压(UV)和过压(OV)阈值进行比较。电压必须在窗口内维持256 ms,否则将被认为无效,定时器会复位。

有效信号是高压开漏输出,当相应的V1、V2、V3在OV/UV窗口内并维持256 ms时,输出会变为低电平。当V1、V2或V3超过阈值窗口时,引脚被释放。这些引脚与FPGA连接,系统级软件可以(通过简单的逻辑表)确定正在使用哪个电源,并根据哪个电源处于活动状态来管理其自身状态。

LTC4417将UV1和OV1的输入与1.0 V进行比较。UV1信号低于1.0 V表示发生欠压事件。OV1信号升至1.0 V以上表示发生过压事件。电阻用于对输入电压进行分压,以与阈值进行比较。

所有三个电源都是实时验证,彼此独立的。当一个输入电源得到验证后,LTC4417上的相应有效信号会被驱动到低电平。

每个通道都有一对背靠背MOSFET,以防止电流从一个电源反向馈送到另一个电源。

确定使用什么电压来验证电池时必须小心。使用电池输出(+V_BATT)不能很好地验证电池输入。如果向上转换的电压得到了妥善的调节,它不会提供任何指示。同时+V_BATT (3.2 V)和GND之间还放置了一个大约30 kΩ的电阻。这会产生100 μA的负载,当器件关闭并持续消耗电池电量时,无法禁用此负载。

输入电源之间的热插拔

ADRV-PACKRF能够处理热插拔事件。工作期间可以插入或拔出任何电源,系统会保持通电状态(备用电池须有足够的电量)。所有验证和优先级排序仍由LTC4417处理。

当在输入电源之间切换时,LTC4417输出端的大电容组为系统供电。电容组(C)的大小由一个经典公式确定:

其中:

C 是在输入电源之间切换时为无线电供电所需的电容量。

I 是无线电在工作期间消耗的电流(最大值)。

dT 是电容组必须提供电流的时间量。

dV 是无线电消耗功率引起的电容电压的下降。

数据手册建议dTMAX为20 μs。用于计算的dT为75 μs,目的是在热插拔期间提供相当可观的裕量。消耗的最大电流量(I)为4 A。

dV的确定很复杂。门槛是ADRV9361-Z7035输入电压范围(4.5 V至5.5 V)。ADRV9361-Z7035上的ADM1166电源时序控制器通过遵守XCZ7035数据手册中明确的上电和断电规范来保护FPGA。如果电压降至4.5 V以下,时序控制器就会关闭系统。须将裕量包括在内以支持电源之间的切换,。

所以需要权衡。裕量不足(50 mV)会大大减少电容组保持4.5 V以上电压的时间。需要增加相应的电容。

增加电容对电源稳定性有负面影响,而且会占用PCB上过多的物理面积。不能假设电流低于最大值,因为无线电必须在所有条件下运行。

同样,裕量过多(400 mV)也会造成很多问题。这虽然降低了电容要求(750 μF),但也拉紧了UV和OV阈值,使得输入电源上的任何初始精度误差(线路或负载调整率)都会导致UV阈值误报,而且还会中断RF SOM的操作。

选择的电压约为200 mV:

这里含有一些空焊盘,以便在温度改变、电压降额或有其他变化的情况下能够改变净电容。

计算UV阈值

输入电源电压降至4.7 V以下会触发UV阈值。LTC4417输入比较器的输入范围为0.985 V至1.015 V(输入误差为1.5%)。处理UV阈值时,使用此范围的低端(0.985 V)可确保其支持所有器件的运行。

为R1和R2选择的值分别为16.9 kΩ和4.53 kΩ。所有UV电阻均为0.1%容差。使用标准电阻值会导致电压裕量略微增加至约230 mV。

计算OV阈值

输入电源电压升至5.3 V以上会触发LTC4417的OV阈值。过压阈值与欠压阈值具有相同的输入范围(0.985 V至1.015 V)。处理OV阈值时,使用此范围的高端可确保其支持所有器件的运行。

为R1和R2选择的值分别为24.3 kΩ和5.49 kΩ。所有OV电阻均为0.1%容差。使用标准电阻值会导致电压裕量略微增加至约230 mV。

掉电

PCB上有如此大的电容组对热插拔期间维持系统运行很有帮助。然而,它也带来了意料之外的负面影响。由于电容组无法足够快地放电到地,所以系统无法快速关闭和重启(大约几秒)。

这就需要一个晶体管,其由SYSTEM_ENABLE信号(图12)驱动,用来缩短该电容的放电时间。

按钮控制器

LTC2955按钮控制器负责处理与ADRV-PACKRF上电或关断相关的使能、中断或终止信号。一个小型三输入电源复用器允许任何输入电源为使能电路供电,并保证该模块始终有电。

即使PoE和壁式电源适配器断开连接,电池电压也会给使能电路供电,并支持器件进行适当的开关机循环。此电路消耗的功率对电池充电的影响极小。

OLED显示屏和导航开关

每个ADRV-PACKRF都有一个全彩色1.69英寸OLED显示屏和一个带滚轮和中心选择器的2轴机械开关。显示和导航开关连接到FPGA,用来控制菜单导航、变量读取以及ADRV-PACKRF特性的设置和修改(例如:GPS坐标、IP地址、TX和RX LO频率、电池状态等)。

IMU

ADIS16460是一款完整的惯性测量单元(IMU),内置一个三轴陀螺仪和一个三轴加速度计。IMU在工厂中针对灵敏度、偏置和对齐进行了预校准。陀螺仪的测量范围为±100°/秒,运动中偏置稳定度为8°/小时(典型值),X轴角向随机游动为0.12°/√小时(典型值)。加速度计具有±5 g的动态范围。

GPS

Quectel L76-M33 IC是一款小型(10.1 mm x 9.7 mm) GNSS模块。该IC有33个跟踪通道和99个采集通道,可以跟踪任何GPS或GLONASS信号。L76-M33具备低功耗、抗干扰和高灵敏度(-165 dBm跟踪、-148 dBm采集)特性,支持创建快速、精确的GPS系统。

RTC

ADRV-PACKRF包含一个I2C实时时钟(RTC)及带备用电池的SRAM。如果系统断电,RTC即由电池电压供电,所以它总是能够精确地记录时间。

RTC与ADM1166共用一个I2C地址,后者是RF SOM上的一个器件。因此,系统含有一个I2C地址转换器,用来对每个器件分别寻址。RTC的地址从0x68变为0x69。下表列出了载板或RF SOM上所有器件的I2C地址。

通过与按钮控制器(LTC2955)互动,RTC的中断信号可用来使能或禁用系统。这样,经过特定的可编程ΔT之后可以开启或关闭系统。

音频

ADAU1761立体声音频编解码器与配件检测开关相结合,支持使用任何开放式移动终端平台(OMTP)或蜂窝电信行业协会(CTIA)耳机标准。借助标准检测和插孔插入检测,系统可以在设备插入盒子时识别并适应其标准,为用户提供干净可用的音频。

| 引脚 | 描述 |

| 1 | 地 |

| 2 | 麦克风 |

| 3 | 右侧耳机 |

| 4 | 左侧耳机 |

| 引脚 | 描述 |

| 1 | 麦克风 |

| 2 | 地 |

| 3 | 右侧耳机 |

| 4 | 左侧耳机 |

图15. 连接器接口引脚图

插入后,系统检测麦克风音频标准,麦克风连接(应用麦克风偏置)并将地连接到耳机地。

机械设计

- 元件放置

- 外壳面板

- 3D建模、设计和装配

PCB边缘连接器和ADRV9361-Z7035之间的元件放置非常紧密。连接器、禁区、隔离、电感和二极管需要大量PCB面积。重新定位任何连接器最终都要求重新布置PCB的整个前部。

设计糟糕的面板会造成极差的用户体验。主要困难是连接器靠得太近,因而难以单独插拔一条电缆。重要的是要考虑人的手指有各种形状和大小,必须能够进入设计的特定部分而不会无意中触及其他部分。

面板设计也影响了PCB的高密度元件区域。就像为了提供更好的用户体验而将连接器在面板上移来移去一样,PCB的上述部分大多数也是这么做。

3D打印工具对该系统的设计非常有益。第一个3D打印项目是原型PCB的比例模型,用于验证物理约束。项目的早期阶段完成了大部分3D建模和垂直元件碰撞检查。

当为了验证变更而更新设计时,面板修订版是3D打印的。连接器位置略有变化,这看起来并不重要,但最终却非常重要。因此,3D建模可以快速验证潜在的代价高昂的错误。

最大的装配挑战是将UFL电缆固定在盒子内部。一旦机箱关闭,电缆部分或完全断开的可能性是无法接受的。一个3D打印的小型塑料支架对实现牢固的UFL连接器解决方案起到重要作用。连接由塑料中的各个沟道固定,并使用PCB的安装孔通过螺丝压住。图19显示了电缆与PCB的连接是如何固定到位的,即使需要推拉和布置电缆,也不会影响这种固定。

系统软件架构

ADRV-PACKRF的软件由ADI公司作为开源参考设计提供的,可用于各种应用。系统源代码由几个部分组成,这些部分共同用来控制板载器件,并提供与外部工具的连接以支持开发。以下部分要么用于构建ADRV-PACKRF固件,要么可以从主机PC通过网络连接远程使用:

- FPGA HDL代码

- Linux内核/器件驱动

- U-boot引导程序

- 图形用户界面(GUI)

- 调制解调器应用设计

- IIO示波器

- 第三方仿真和开发工具

- MATLAB, Simulink, GNU Radio

ADRV-PACKRF可以将数据直接流传输到标准框架,如MATLAB、Simulink和GNU Radio等,从而支持快速设计数字信号处理(DSP)原型和开发。此外,ADI公司还提供完整的开源应用IIO示波器,可用于简化板载AD9361收发器的调试和评估。此应用基于工业输入/输出(IIO) Linux内核框架和支持libIIO用户库。用户既可以远程控制不同的板载硬件,也可以在设备上控制。为ADRV-PACKRF提供的标准内核是经过定制的,支持系统提供的其他硬件,包括IIO框架之外的硬件,例如板载GPS接收器、OLED屏幕、点击式转盘界面等。为优化设计减少PS资源该平台,可以使用Xilinx®软件开发套件(XSDK)设计裸机驱动程序。

FPGA/HDL设计

我们为ADRV9361-Z7035提供了一套标准硬件设备语言(HDL)参考设计,其专为安装ADRV9361-Z7035的载板而设计。通过HDL Coder可以使此参考设计以HDL为目标,从MATLAB和Simulink进行快速原型开发。

从低压差分信号(LVDS)传输到双倍数据速率(DDR)存储器存储的整个Rx/Tx数据路径都是通过不同IP内核以HDL实现,支持重新配置和移植到最终设计。

AD9361 IP内核实现了LVDS双端口全双工接口,允许使用AD9361时钟和数据延迟以及ZC7035 IO延迟元件进行校准和验证。如果需要,该IP支持直接数字频率合成(DDS)信号生成、直流偏移校正和I/Q校正。

该IP内核包含时分双工(TDD)逻辑,可用于驱动器件的ENABLE/TXNRX控制引脚,在TDD模式下实现比仅使用软件控制更快的切换速度。

该项目的设计是高度模块化的,便于移植到不同的载板,而所有用来驱动ADRV9361-Z7035硬件的IP内核保持不变。

Linux子系统—LibIIO

LibIIO用于连接Linux工业输入/输出(IIO)子系统。Linux IIO子系统为ADI器件(比如模数转换器ADC或数模转换器DAC)提供支持。这些器件包括但不限于ADC、加速度计、陀螺仪、IMU、电容数字转换器(CDC)、压力传感器、彩色/光线/接近传感器、温度传感器、磁力计、DAC、直接数字频率合成(DDS)、锁相环(PLL)、可变增益放大器(VGA)、可编程增益放大器(PGA)和RF收发器。

LibIIO可以在嵌入式Linux目标设备上使用,或者也可以用来从Linux、Windows®或MAC主机通过USB、以太网或串行端口远程连接到该目标设备。LibIIO通过抽象隐藏了IIO内核ABI的低级细节,因此侧重于易用性。该跨平台系统库还提供C、C++、C#或Python等高级语言绑定,允许应用开发人员使用其偏爱的编程语言。

收发器器件驱动程序堆栈

axi_ad9361 IP内核是本项目中使用的HDL/FPGA传输层内核。它处理Rx/Tx和ADC/DAC传输方向。该单个物理IP核在逻辑上被分离,然后由两个独立的IIO驱动程序处理,每个驱动程序对应一个传输数据方向。第三个控制驱动程序配置和控制AD9361内部寄存器;此部分通过SPI总线实例化,称为PHY (ad9361-phy)驱动程序。PHY驱动程序控制典型的收发器无线电功能,例如LO频率、基带滤波器、速率、增益控制、Tx衰减等。

AXI-ADC HDL驱动程序控制数据接收方向。数据接收驱动程序(AXI-ADC)的器件探测功能将会延迟到SPI控制PHY驱动程序完全实例化为止,该功能用于控制AXI-HDL内核寄存器和DMA (AXI_DMAC)。这种分离是必要的,因为AXI-ADC和SPI PHY部分是通过不同总线实例化,但共享同一数据结构,这样PHY驱动程序便可控制和查询AXI寄存器的参数,如格式转换、数字接口时序验证、调谐等。或者,PHY驱动程序也可以独立于AXI-ADC接收驱动程序和底层HDL设计使用。此外,AXI-ADC驱动程序可以选择从板载GPS器件接收1 pps信号,并计算同步时钟源与AD9361产生的基带速率之间的偏移,从而实现精确的频率偏移校正。

发射方向上使用AXI-DAC-DDS HDL驱动程序。与接收驱动程序一样,此驱动程序也独立于物理接口层,因此可以与CMOS或LVDS型接口一起使用。在本设计中,该驱动程序以独立模式使用。但是,设计使用了Linux公共时钟框架(CCF),以便该驱动程序知道所连接的转换器PHY器件的采样频率。

该传输层驱动程序还实现了每通道多相双音DDS内核以及基于DMA的波形缓冲机制。缓冲器可以用任意数据填充,然后循环重复或数据流的方式使用。

图24中的框图显示了axi_ad9361 IP内核及其内部集成的TDD控制器模块。如果控制器已使能,则所有流入或流出AD9361的数据均由此模块控制。此模块使用的器件驱动程序称为AXI TDD HDL驱动程序。有关本电路笔记中讨论的所有软件组件的信息,请参见ADI公司维基百科上的相应页面。

软件控制的组件

还有其他一些Linux器件驱动程序用于控制ADRV-PACKRF的功能。这些驱动程序全都作为标准库提供,并且包含在无线电平台的定制Linux镜像中。

| ADRV-PACKRF 功能 | 驱动程序框架 |

| OLED 显示屏 | 帧缓冲器件 |

| 旋转轮 | 输入器件 |

| 导航按钮 | 输入器件 |

| 电源开关 | 输入器件 |

| LEDs | LED 类 |

| ADAU1761 | ALSA SoC子系统 |

| ADP5061, LTC2942 | 电源子系统 |

| AD9361, ADIS16460 | IIO子系统 |

ADRV-PACKRF GUI

ADRV-PACKRF的图形用户界面(GUI)提供了一种简单的脚本式方法来实现菜单、控件和外部应用程序的启动。

软件应用

使用ADRV-PACKRF可以实现许多不同的应用,包括通信、仪器仪表、雷达等。该器件具有高度可编程性,可以根据应用需要加载不同的HDL和软件,然后针对其他应用交换或重新配置HDL和软件。默认情况下,ADRV-PACKRF以基本设计交付,允许直接访问和控制板载收发器及原始I/Q数据流。此数据可以流传输回到IIO-Scope或其他受支持的第三方工具。作为对此标准设计的补充,ADRV-PACKRF也提供一个点对点链路调制解调器设计。此设计可以通过更换附带的SD卡来加载,然后由最终用户加以定制。有关可用软件应用的更多信息,请参阅 CN-0412 用户指南。

数字调制解调器参考设计

围绕ADRV9361-Z7035构建的一个常见产品是便携式通信链路,其部署在无蜂窝基础设施或用户可能希望保持离网状态的区域中。在此类应用中,为使无线电之间能够通信,必须对发射和接收的数据流进行信号处理以同步无线电,从而实现有效通信。AD9361收发器不提供链路级同步,因为同步与波形有关。ADRV9361-Z7035可用于实现指定波形的必要算法。

ADRV-PACKRF包含一个开源单载波调制解调器设计,演示了如何实现数字通信链路。该调制解调器参考设计(MRD)分散在ADRV9361-Z7035的可编程逻辑(PL)和处理系统(PS)上。这种划分支持确定性高速数字信号处理(DSP)和灵活的控制与监测。

MRD使用频分双工(FDD)媒体访问控制(MAC)层,允许两个无线电之间连续发射和接收,如图27所示,其中无线电A具有上行链路频率1和下行链路频率2。无线电B的配置相反。

图27. FDD数据链路

ADRV9361-Z7035的PL中的接收器信号处理提供了必要的自适应算法来维持两个无线电之间的链路,并将来自收发器的数字编码转换为成组的比特信息。该接收器信号链如图28所示。

图28. 调制解调器接收器信号链

该接收器链通过决策反馈均衡器(DFE)处理无线电之间±25 ppm的可能偏移以及无线信道中的衰落。当使能前向纠错(FEC)时,MRD可以维持5 Mbps的数据速率。为实现该速率,使用5 MHz信道,收发器合成带宽为20 MHz,码率为1/2,采用QPSK调制。

调制解调器设置在运行着Linux的PS用户空间中,作为标准网络接口。这是利用Linux内核提供的TUN/TAP框架实现的,支持无缝应用级交互。

网络支持

TUN/TAP为简单的点对点或以太网设备提供网络数据包接收与发送。TUN/TAP不是从物理介质接收数据包,而是从用户空间程序接收数据包;不是通过物理介质发送数据包,而是将其写入用户空间程序。

电路评估与测试

通过图29所示的设置,用户可以利用数据链和USB网络摄像头开展简单的实验。

设备要求

PackRF无线电模块(ADRV-PACKRF)套件中包含了如下必需的设备:

- 2个便携式参考无线电

- 2个直流电源

- 1根micro USB OTG电缆

- 1个C270高清USB网络摄像头

- 2个micro SD卡

开始使用

本部分介绍如何设置测试和配置以重复本电路笔记所述的演示和结果。有关如何逐步完成参考设计设置的更详细信息,请参阅CN-0412用户指南。

在无线电1上执行以下步骤:

- 将USB网络摄像头插入USB OTG电缆。

- 将USB OTG电缆插入面板上的micro USB连接器。

- 使用以太网电缆通过以太网端口将无线电1与无线电2连接起来。

在无线电1和无线电2上执行以下步骤:

- 将所提供的micro SD卡插入插槽。

- 将SMA天线连接到TX1A和RX1A。

- 插上电源。

- 按下电源按钮。

在无线电1(已连接网络摄像头)上,

- 从OLED屏幕打开Network(网络)菜单。

- 将IP Address(IP地址)设置为192.168.0.101。

- 将Peer IP Address(对等IP地址)设置为192.168.0.102。

- 返回主菜单。

- 打开Modem(调制解调器)菜单。

- 将IP Address(IP地址)设置为192.168.23.1。

- 将Peer IP Address(对等IP地址)设置为192.168.23.2。

在无线电2(未连接网络摄像头)上,

- 从OLED屏幕打开Network(网络)菜单。

- 将IP Address(IP地址)设置为192.168.0.102。

- 将Peer IP Address(对等IP地址)设置为192.168.0.101。

- 返回主菜单。

- 打开Modem(调制解调器)菜单。

- 将IP Address(IP地址)设置为192.168.23.2。

- 将Peer IP Address(对等IP地址)设置为192.168.23.1。

在无线电1(已连接网络摄像头)上,从主菜单运行Autoconfig(自动配置),让此操作全部完成。

在无线电2(未连接网络摄像头)上,转到OLED屏幕,从主菜单中单击Recv Video(接收视频)。

在无线电1(已连接网络摄像头)上,转到OLED屏幕,从主菜单中单击Send Video(发送视频)。

有关设置的更多信息和完整详情,请参阅CN-0412用户指南。