ADN4692E

量产带1型接收机的3.3 V、100 Mbps、全双工、高速M-LVDS收发器

- 产品模型

- 2

概述

- 多点LVDS收发器(低电压差分信号驱动器和接收器对)

- 开关速率: 100 Mbps (50 MHz)

- 支持的总线负载: 30 Ω至55 Ω

- 2类接收器可供选择

- 1类(ADN4690E/ADN4692E): 迟滞为25 mV

- 符合M-LVDS的TIA/EIA-899标准

- M-LVDS总线上的无毛刺上电/关断

- 驱动器输出转换时间可控

- 共模范围: -1 V至+3.4 V,允许在2 V接地噪声下进行通信

- 欲了解更多特性,请参考数据手册

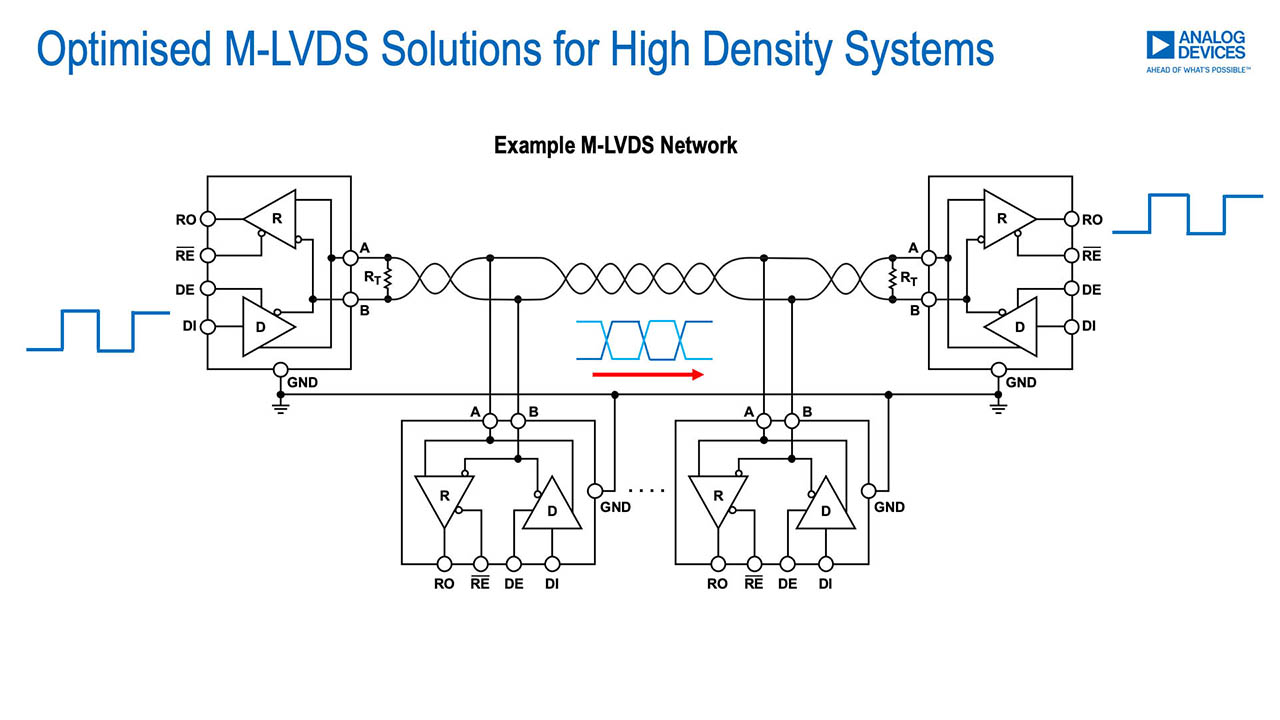

ADN4690E/ADN4692E是多点低压差分信号(M-LVDS)收发器(驱动器和接收机对),工作速率最高可达100 Mbps (50 MHz)。驱动器输出端实施压摆率控制,以增强输出信号完整性,并较大程度地减少反射。接收机可在-1 V至+3.4 V的共模电压范围内利用低至50 mV的差分输入检测总线状态。总线引脚上提供最高可达±15 kV的ESD保护。

ADN4690E/ADN4692E遵循M-LVDS的TIA/EIA-899标准,为TIA/EIA-644 LVDS器件添加了额外的多点能力。该驱动器在多点总线拓扑结构上允许低至30 Ω的总线负载,且控制驱动器输出转换时间以较大程度地减少反射。总线最多支持与32个节点连接。

ADN4690E/ADN4692E是1型接收机,在差分输入电压下具有25 mV的迟滞,因此缓慢变化的信号或输入损耗不至于引起输出振荡。

ADN4690E/ADN4692E提供8引脚SOIC封装的半双工配置(ADN4690E)或14引脚SOIC封装的全双工配置(ADN4692E)。

应用

- 背板和电缆多点数据传输

- 多点时钟分配

- 低功耗、高速替代器件,可缩短RS-485链路

- 网络路由器和交换机

- 无线基站基础设施

参考资料

数据手册 1

用户手册 1

应用笔记 3

视频 5

ADI 始终高度重视提供符合最高质量和可靠性水平的产品。我们通过将质量和可靠性检查纳入产品和工艺设计的各个范围以及制造过程来实现这一目标。出货产品的“零缺陷”始终是我们的目标。查看我们的质量和可靠性计划和认证以了解更多信息。

| 产品型号 | 引脚/封装图-中文版 | 文档 | CAD 符号,脚注和 3D模型 |

|---|---|---|---|

| ADN4692EBRZ | 14-Lead SOIC | ||

| ADN4692EBRZ-RL7 | 14-Lead SOIC |

| 产品型号 | 产品生命周期 | PCN |

|---|---|---|

|

9月 16, 2015 - 15_0129 Metal Mask Edits to ADN469XE Family of Devices. |

||

| ADN4692EBRZ | 量产 | |

| ADN4692EBRZ-RL7 | 量产 | |

这是最新版本的数据手册

工具及仿真模型

IBIS 模型 1

评估套件

最新评论

需要发起讨论吗? 没有关于 ADN4692E的相关讨论?是否需要发起讨论?

在EngineerZone®上发起讨论