広帯域 GSPS ADC のスプリアスフリー・ダイナミック・レンジを理解する

高性能システム用の広帯域 A/D コンバータ(ADC)を選択する際には、ADC の分解能、サンプリング・レート、S/N 比(SNR)、有効ビット数(ENOB)、入力帯域幅、スプリアス・フリー・ダイナミック・レンジ(SFDR)、微分/積分非直線性など、数多くのアナログ入力仕様を考慮する必要があります。

GSPS(ギガサンプル/秒)ADC において、SFDR は最も重要な AC性能仕様の 1 つでしょう。この値は、ADC が他のノイズやスプリアス周波数から搬送波信号を解読する能力、そして結果的にはシステムの解読能力を示すものです。

GSPS ADC で使用する変換速度を実現するにあたり、目的の高サンプル・レートで信号をキャプチャするアーキテクチャがいくつかあります。しかし、これらのうちいくつかのアーキテクチャは、全帯域幅 SFDR 性能を犠牲にすることによって、この要求を満たしています。

ここでは、コンバータの SFDR がシステムに与える影響を理解するために、SFDR 仕様の詳細、コンバータのデータシートでの記載方法、ADC の性能を制限するアーキテクチャと最大限に生かすアーキテクチャ、SFDR 性能を制限するシステム設計要素などに関して、設計技術者から寄せられたいくつかの一般的な質問に答えていきます。

データシートに示されている SFDR には注記のあるものとないものがあります。SFDR とは、正確には何でしょうか?

多くのシグナル・アクイジション・システムの鍵となるのは、ノイズと信号を正確に識別できる能力です。定められた電気通信プロトコル、レーダー・スイープ、測定機器の別を問わず、微弱な信号を取り込んで解読することは、優れたシステム性能の要です。

SFDR は、大きな干渉信号から識別可能な最小の電力信号を表すもので、搬送波電力の rms 値(二乗平均平方根値)と、高速フーリエ変換(FFT)などの周波数領域に見られる 2 番目に大きいスプリアス信号の rms 値の動的な比率を決定します。したがって、定義上、このダイナミック・レンジには他のスプリアス周波数は存在しないはずです。

多くの場合、SFDR は、対象となる搬送波の電力から 2 番目に大きいスプリアス周波数の電力までの相対的な範囲として表されます(dBc)が、フルスケール信号の電力を基準に表す(dBFS)ことも可能です。対象となる搬送波は比較的低電力の信号で、ADC へのフルスケール入力をはるかに下回ることがあるので、これは重要な差です。この場合は、ノイズやスプリアス周波数からの信号を識別する上で SFDR が最も重要な指標となります。

ADC の SFDR を制限する要素は何ですか?

高調波周波数は基本周波数を整数倍したものです。適切に設計されたモノリシック ADC コアの SFDR は、通常、搬送波周波数と、対象基本周波数の第 2 または第 3 高調波の間のダイナミック・レンジに支配されます。狭帯域 ADC のデータシートの中には、狭い動作帯域内だけの SFDR を定義しているものがありますが、その場合は第 2 および第 3 高調波が帯域外にあるのが普通です。また、広帯域での SFDR を記載したうえで、その性能を得るための条件が注記されているデータシートもあります。

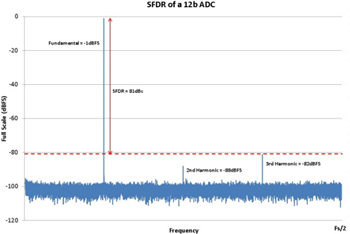

通常、主要なスプリアス周波数は第 2 または第 3 高調波ですが、システム上の他の理由から GSPS ADC の SFDR 性能を制限する可能性のあるスプリアスも存在します。例えば、インターリーブ ADC コアが複数存在する場合は、周波数領域にインターリーブ・アーチファクトが生じることによって、スプリアス周波数が生成される可能性があります。これらは基本周波数の第 2 または第 3 高調波より大きくなることがあるので、SFDR の主要な制限要素となり得ます。直感的にはわかりにくいかもしれませんが、インターリーブ ADC のデータシートでは、インターリーブ・スプリアスが計算から除外されていることを注記したうえで SFDR を仕様規定する場合もあります(図 1)。

図 1. これはモノリシック 12 ビット ADC の FFT で、第 3 高調波が SFDR に影響する主要な要素であることがわかります。この場合のダイナミック・レンジは搬送波電力を基準とするため、基本波(−1 dBFS)から第 3 高調波(−82 dBFS)までのダイナミック・レンジは −81 dBc です。

狭帯域 SFDR を広帯域 SFDR に補外することはできますか?

システムの使用する帯域が狭帯域のスペクトラムだけの場合は、バンドパス・アンチエイリアシング入力フィルタを使って、当該帯域外の高調波やアーチファクトを除去することができます。一部のアプリケーションでは、フィルタによって除去したこの周波数帯域内の信号を監視する必要がない限り、この方法が有効です。しかし、広帯域シグナル・アクイジション・システムにこの方法を用いることはできません。データシートによっては、ADC の全入力帯域幅よりもはるかに狭い範囲でスライスした帯域幅に対して、ADC の SFDR を仕様規定している場合もあります。

通常、狭帯域の SFDR を補外すれば、Fs/2 ナイキスト帯域のより広い範囲あるいは全域にわたる性能がわかるとは考えられません。これは主に、狭帯域の基本波に関する周波数プランニングが、高次の高調波をフィルタリングして対象周波数帯域外へ除外するために意図的に作成されたものだからです。フィルタを除去すると、これらの高調波とその他のスプリアスは、システム内に見られる広帯域 SFDR の一部となります(図 2 および図 3)。

図 2. 狭帯域アプリケーションでは、広帯域 SFDR 性能があまり高くない ADCでも効果的に使用することができます。アンチエイリアス・フィルタを使用して赤い網掛け部分の周波数を除外することにより、通常ならば SFDR を低下させる高調波またはスプリアスが帯域外に除外されています。

図 3. 同じ条件で ADC フィルタリングを使用しないとすると、SFDR は広帯域高調波またはスプリアスによって制限されます。これは、狭帯域 SFDR が優れていても、広帯域 SFDR に補外できない場合もあることを示しています。

差動入力 ADC の SFDR が他のフロント・エンド・システム部品の影響を受ける可能性はありますか?

ほとんどの高速 ADC は差動入力方式を使用しています。この方式は良好な同相ノイズ除去能力を提供しますが、この利点を生かすには、多くのアクイジション・システムにおいて、ADC入力の前段でシングルエンド信号を差動信号に変換する必要があります。このシングルエンド信号から差動信号への変換プロセスのための主な選択肢として、受動バランまたはトランス、および能動アンプが挙げられます。システムのこの部分に選択できる高性能部品は多数ありますが、最良のソリューションを選択したとしても差動信号にはある程度のアンバランスが含まれるので、目的の信号に歪みが生じて、ADC 全体の SFDR 値は低下します。

ADC のフロント・エンドで差動入力信号の両側入力間に生じる位相不整合は、基本信号の高調波電力を増大させます。これは、一方の差動信号が、周期を基準として一定の位相分だけ他方より時間的に進んでいる場合に発生する可能性があります。この現象を図 4 に示します。この場合、差動ペアの一方の周期的位相が、他方よりわずかに進んでいます。

図 4. この例では、ADC 差動入力に対するバランの出力には数度の位相不整合があります。これにより、差動入力の位相が完全に整合している場合よりもFFT 上の第 2 高調波が大きくなり、その結果 SFDR に悪影響を与えます。

差動信号アクイジション・システムのフロント・エンドにおいて考えられるもう 1 つのアンバランスは、振幅の不整合です。差動信号の一方のゲインが他方と異なる場合は、ADC 入力の一方が大きく、他方が小さくなります。これは基本信号のフル電力を低下させるもう 1 つの要因で、SFDR の dBc 値を減少させます。差動入力間に 2 dB の振幅不整合があると、入力信号電力のフルスケール値が 1 dB 低下します。フロント・エンド信号の完全性に関するこれらの問題は、それぞれ ADC の SFDRとシステム全体の信号解読能力を低下させる可能性があります。

SFDR を制限する可能性のあるADC アーキテクチャには、どのようなものがありますか?

最大サンプル・レートが 1 GSPS 以上のいくつかの ADC は、高速データ・レート性能を最大限に引き出すために、2 つ以上のディスクリート・チャンネルまたはコアを使用するインターリーブ方式を採用しています。例えば、インターリービングを使用することにより、サンプル・アクイジション・プロセスを通じて各コアが順番に動作するデュアル・チャンネル ADC を使って最大限のサンプル・レートを実現することができます。1 つのチャンネルがサンプリングを行っている間、他のチャンネルはまだ前のサンプルの処理を続けます。インターリーブ・アーキテクチャでは、3 個以上の ADC コアを使用することもあります。

インターリーブ方式を使用すると、複数の ADC コアを並列で機能させることが可能で、シングル・コアの場合よりも高いサンプル・レートが得られます。ただし、これらの各コアの入力には、位相、オフセット、ゲイン、および帯域幅にわずかな差が存在します。その結果、周波数スペクトラムに新たなインターリーブ・アーチファクトやイメージ・スプリアスが生じ、それによって ADC の広帯域 SFDR が低下する可能性があります。これはシステムのダイナミック・レンジを減少させ、対象となる微弱信号とインターリーブ・スプリアスを識別する能力を低下させます。システム・エンジニアは、インターリーブ ADC からのアーチファクトを軽減するために、特別なキャリブレーション・モードやスプリアスに関するプランニング方法について、詳細なアプリケーション・ノートを参照する必要があります。

処理用のコアが 1 つだけのモノリシック ADC アーキテクチャでは、インターリーブ・スプリアスは発生しません。シングル・パイプライン・コア ADC は、比較的高い SFDR を備えた広帯域コンバータの一例で、通常は第 2 または第 3 高調波の制限を受けます。

周波数領域でのインターリーブ ADC にはどのような性能が見られますか?

3 個のディスクリート・インターリーブ・コアで構成されたサンプリング・アーキテクチャでは、2 つのゲインおよび位相イメージ・スプリアスと、1 つのオフセット・スプリアスがあります(図 5)。オフセット・スプリアスは 2/3 × ナイキストの位置に確認できますが、これはこの場合の SFDR に影響する主要な要素ではありません。 SFDR を制限するゲインおよび位相スプリアスは、(2/3 × ナイキスト ± アナログ入力周波数) の位置に見られます。

図 5. この FFT は、インターリーブ・システム基板に使われている 3 個のディスクリート ADC のものです。この場合のインターリーブ・スプリアス・アーチファクトは、第 2 高調波の場合(−85 dBFS)よりも SFDR を −8 dBc 低下させます。

システムの SFDR に影響する主要な要素は最も大きいスプリアスです。インターリーブ・スプリアスがなければ、SFDR は基本周波数から第 2 高調波までのダイナミック・レンジとなりますが、この場合は、インターリーブ・イメージ・スプリアスのために SFDR 性能が − 8 dB 低下しています。

4 個のディスクリート・インターリーブ・コアで構成されたサンプリング・アーキテクチャでは、3 つのゲインおよび位相イメージ・スプリアスと、2 つのオフセット・スプリアスがあります(図 6)。ナイキスト周波数と 1/2 × ナイキスト周波数の位置にオフセット・スプリアスがあり、もう 1 つのイメージ・スプリアスが (ナイキスト − アナログ入力周波数) の位置にありますが、この場合、これらは SFDR を決定付けるようなものではありません。SFDR を決定付けるゲインおよび位相スプリアスは、(½ × ナイキスト ± アナログ入力周波数) の位置にあります。

図 6. この FFT は、インターリーブ・システム基板に使われている 4 個のディスクリート ADC のものです。SFDR に影響するイメージ・スプリアス・アーチファクトは ½ × ナイキスト ± Ain の位置にあり、第 3 高調波の場合(−84 dBFS)よりも SFDR を −13 dBc 低下させます。

これらのスプリアスが第 2 または第 3 高調波より大きい場合は、システムの SFDR に影響する主要な要素となります。インターリーブ・スプリアスがなければ、SFDR は基本周波数から第 3高調波までのダイナミック・レンジとなりますが、この場合は、インターリーブ・イメージ・スプリアスのために SFDR 性能が −13 dB 低下しています。

SFDR を制限するその他の要素

SFDR を低下させる可能性があるもう 1 つの要素は、ADC のアナログ入力やクロック入力に外部ノイズが加わるようなシステム設計です。また、システム基板のレイアウトを慎重に行わないと、ADC のデジタル出力が入力に戻ってしまうおそれがあります。外部ノイズは、ADC のリファレンス、電源、あるいはグラウンド領域にも入り込む可能性があります。ノイズが十分に大きく半周期的なものである場合は、SFDR を制限する望ましくないスプリアスとしてシステムの周波数領域に現れることがありますが、これらのスプリアスは基本周波数や ADC アーキテクチャとは無関係です。

GSPS ADC の将来

現在では、これまでシステム性能を制限してきたインターリーブ・アーチファクトのない、高い広帯域 SFDR を提供する GSPSADC が使用できるようになりました。AD9680 はデュアル・チャンネルの 14 ビット 1 GSPS ADC で、1 GHz 入力で 78 dBc のSFDR を実現します。また、AD9625 は 12 ビットの 2 GSPS ADCで、1 GHz 入力時の代表値で 80 dBc の広帯域 SFDR を提供します。

SFDR は GSPS ADC の重要な性能指標です。通常、広帯域 SFDRは基本信号の第 2 または第 3 高調波によって制限されます。シングル・モノリシック・パイプライン ADC やその他の先進的アーキテクチャは、高性能 GSPS コンバータの新たな領域を開きつつあります。これらのアーキテクチャは、従来 GSPS レベルの ADC アーキテクチャに見られた、周波数領域のインターリーブ・スプリアスを発生させません。

広帯域応答が求められるアプリケーションでは、これらのアーチファクトの特定、プランニング、および除去が問題になる可能性があります。新しいソリューションはこれらのシステム上の問題を解決し、広帯域スペクトル全域にわたって最先端の SFDR 性能を提供します。

著者について

この記事に関して

製品

A/Dコンバータ、12ビット、2.0/2.5/2.6GSPS、1.3V/2.5V

A/Dコンバータ、14ビット、1.25GSPS/1GSPS/820MSPS/500MSPS、デュアル、JESD204B