概要

設計リソース

設計/統合ファイル

- Schematic

- Bill of Materials

- Gerbers Files

- PADS Files

- Assembly Drawing

評価用ボード

型番に"Z"が付いているものは、RoHS対応製品です。 本回路の評価には以下の評価用ボードが必要です。

- EVAL-CN0251-SDPZ ($98.44) A Flexible 4-Channel Analog Front End for Wide Dynamic Range Signal Conditioning

- EVAL-SDP-CB1Z ($134.00) Eval Control Board

デバイス・ドライバ

コンポーネントのデジタル・インターフェースとを介して通信するために使用されるCコードやFPGAコードなどのソフトウェアです。

AD719x GitHub no-OS Driver Source Code

AD7192 IIO High Precision ADC GitHub Linux Driver Source Code

機能と利点

- 4チャンネル、広いダイナミックレンジ

- 産業用信号レベル

- 高いコモン・モード除去比

製品カテゴリ

マーケット & テクノロジー

使用されている製品

参考資料

-

CN-0251 Software User Guide2018/10/22WIKI

-

MT-101: Decoupling Techniques2015/02/14PDF954 kB

-

MT-073: High Speed Variable Gain Amplifiers2015/02/14PDF177 kB

-

MT-023: ADC Architectures IV: Sigma-Delta ADC Advanced Concepts and Applications2015/02/14PDF936 kB

-

MT-022: ADC Architectures III: Sigma-Delta ADC Basics2015/02/14PDF289 kB

-

MT-031: データ・コンバータのグラウンディングと、「AGND」および「DGND」に関する疑問の解消2009/03/20PDF144 kB

回路機能とその特長

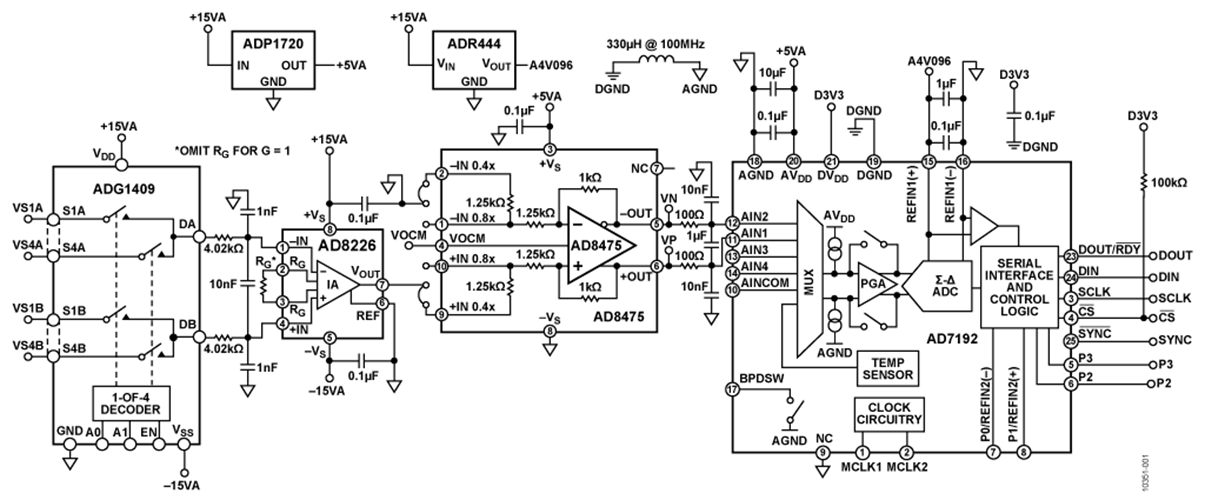

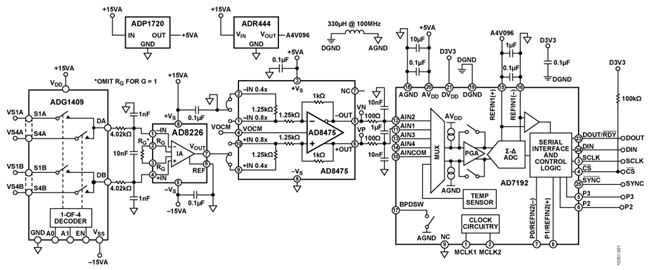

図 1 に示したのは、A/D コンバータ(ADC)用のシグナル・コンディショニング(信号調整)回路の回路図です。この回路は、数mVp-p から20Vp-p までの広いダイナミック・レンジで信号を処理できる高い柔軟性を備えています。このダイナミック・レンジ は、プログラマブル・ゲイン・アンプ(PGA)を内蔵する高分解能のADC を使うことで、必要なコンディショニングとレベル・ シフトを行うことで実現しています。

プロセス制御や産業用オートメーションの分野では、±10V のフルスケール信号が広く一般的に使用されています。±10V の信号を低電圧動作の最新ADC で処理するには、信号の減衰とレベル・シフトが必要になります。ただし、アプリケーションによっては、信号がわずか数mV のレベルにとどまることもあります。小振幅の信号を扱う場合、ADC のダイナミック・レンジを活かすためには信号を増幅する必要があります。こうした理由から、入力信号が広い範囲にわたって変動するアプリケーションでは、プログラマブル・ゲイン機能を持つ回路を使用するのが望ましいということになります。

また、小振幅の信号を扱う場合、大きなコモン・モード電圧に対処しなければならないこともあります。それには、高いコモン・モード除去比(CMR)が必要です。加えて、ソース・インピーダンスが大きいアプリケーションでは、アナログ・フロントエンド回路には高い入力インピーダンスが求められます。

図1の回路は、プログラマブルなゲイン、高いCMR、高い入力インピーダンスを備えており、上述したすべての課題を解決することができます。入力信号は、4チャンネルのマルチプレクサ「 ADG1409」を介して、入力範囲が広く、低コストの計装アンプ「 AD8226」に送られます。AD8226は、最高80dBの高いCMRと、非常に高い入力インピーダンス(差動モードで800MΩ、コモン・モードで400MΩ)を備えています。広い入力範囲とレールtoレール出力に対応するので、AD8226は電源電圧までの範囲でフルに信号を増幅することができます。

「 AD8475 」は、ゲイン設定用の高精度抵抗を内蔵した完全差動型の減衰アンプです。高い精度での減衰(ゲインG=0.4または0.8)、コモン・モード電圧のレベル・シフト、シングルエンドから差動への変換が可能です。AD8475は使いやすい高精度のゲイン・ブロックであり、単電源で最大±10Vの信号レベルを処理できるよう設計されています。そのため、高いCMRを維持しつつAD8226からの最大20Vp-pの信号を減衰し、後段のADCに差動信号を供給するという用途に適しています。

「 AD7192」は、PGAを内蔵するシグマ・デルタ(ΣΔ)方式の24ビットADCです。低ノイズのオンチップ・ゲイン段(G=1、8、16、32、64、128)を備えているため、振幅の大小にかかわらず、信号を直接入力することが可能です。

以上のICを組み合わせたこの回路は、構成が容易でありながら、広範な振幅の信号に対して非常に優れた性能を発揮します。産業用オートメーション、プロセス制御、計測、医療用機器などの用途に適したシグナル・コンディショニング回路です。

回路説明

図1の回路では、マルチプレクサのADG1409、計装アンプのAD8226、差動アンプのAD8475、ΣΔ方式ADCのAD7192に加え、電圧リファレンスの「ADR444」、リニア・レギュレータの「ADP1720-5」を使用しています。保護、フィルタリング、デカップリングに使用している外部部品はわずかなので、プリント回路基板上の占有面積は非常に小さくて済みます。

レギュレータとリファレンスの選択

この回路では、5Vの電圧を生成するレギュレータとしてADP1720-5を選択しました。ADP1720-5は、高電圧、マイクロパワー(低消費電力)、低ドロップアウトのリニア・レギュレータであり、工業用アプリケーションに適しています。

また電圧リファレンスとしては、出力電圧が4.096VのADR444を選択しました。ADR444は、超低ノイズ、高精度、低ドロップアウトであることを特徴とします。特に、高分解能のΣΔ方式ADCや高精度のデータ収集システムに適しています。

入力スイッチと保護回路

マルチプレクサのADG1409は、2ビットのバイナリ・アドレス・ラインにより、4つの入力チャンネルのうちの1つを選択します。実際の回路評価基板では、標準的なダイオードや、過渡電圧を抑制するための外部保護部品を使用することで堅牢性を強化しています。それらの部品は図1には示されていませんが、CN0251設計サポート・パッケージ (CN0251 Design Support Package)に含まれる詳細な回路図やその他のドキュメントには記載されています。

ADG1409は、4対の差動入力信号(VS1AとVS1B、VS2AとVS2B、VS3AとVS3B、VS4AとVS4B)に対応しています。その出力であるDA、DBは、計装アンプ(AD8226)の入力に接続されています。

入力計装アンプ(AD8226)

AD8226のゲインは、外部抵抗RGによって設定します。図1ではRGについて明示していませんが、これを使用しない場合は、計装アンプ段のゲインは1になります。AD8226の出力は、xを入力チャンネルの番号とすると、「VSxA-VSxB」になります。

値が4.02kΩの2つの抵抗と10nFのコンデンサにより、カットオフ周波数が2.0kHzの単極RCフィルタが構成されています。これによって、AD8226の差動入力信号がフィルタリングされることになります。また、値が1nFの2つのコンデンサにより、カットオフ周波数が40kHzのコモン・モード・フィルタも構成されています。

AD7192が備えるPGAのゲイン設定

ADCのAD7192は、AD8475からの差動出力信号を差動アナログ入力信号として受け取るように構成されています。AD7192のフルスケール入力範囲は±VREF/ゲインで決まります。ここで、±VREF=REFINx(+)-REFINx(-)です。

AD7192が備えるバッファ(アンプ)がイネーブルになると、そのバッファの高インピーダンスの入力段を入力チャンネルが駆動します。このモードにおける絶対入力電圧範囲は、AGND+250mV~AVDD-250mVとなります。ゲイン段がイネーブルになると、バッファの出力がPGAの入力に接続されます。PGAにはさらにヘッドルームが必要なので、アナログ信号の入力範囲は±(AVDD-1.25V)/ゲインに制限する必要があります。以上のことから、4.096Vのリファレンス電圧と5Vの電源電圧を使用する場合、ADCのダイナミック・レンジを最大限に利用するために、信号を減衰/増幅することができます。

| 入力範囲 (VSxA − VSxB) | AD8475のゲイン | AD7192のゲイン | PGAの出力範囲 (バイポーラモード)(V) |

| ±10 V | 0.4 | 1 | ±4 |

| ±5 V | 0.8 | 1 | ±4 |

| ±1 V | 0.4 | 8 | ±3.2 |

| ±500 mV | 0.8 | 8 | ±3.2 |

| ±250 mV | 0.8 | 16 | ±3.2 |

| ± 125 mV | 0.8 | 32 | ±3.2 |

| ±62.5 mV | 0.8 | 64 | ±3.2 |

| ±31.25 mV |

0.8 | 128 | ±3.2 |

差動減衰アンプ(AD8475)

低電圧動作のADCを駆動するには、±10Vまたは±5Vといったレベルの信号を減衰/レベル・シフトする必要があります。高精度の抵抗を使用する必要がある差動アンプ回路では、抵抗間の不整合に起因して必然的にCMR性能が低下します。一方で、減衰とレベル・シフトを担うAD8475は、レーザー・トリミングによって整合を実現した高精度の抵抗を内蔵しています。そのため、小さなゲイン誤差、小さなゲイン・ドリフト(最大で3ppm/℃)、高いCMRが保証されています。

AD8475では、0.4または0.8のゲインをピンによって選択可能です。VOCMピンにより、ADCの入力範囲に応じてダイナミック・レンジが最大になるよう出力コモン・モード電圧を調整し、高精度なレベル・シフトを行います。なお、このピンはオープンでも使用することができます。AD8475は、電源とグラウンドの間に、2つの抵抗(値はいずれも200kΩ)で構成される高精度の分圧回路を内蔵しています。AD8475の内部では、VOCMピンはこの電圧でバイアスされています。つまり、VOCMピンには電源電圧の1/2の電圧が与えられているということです。

AD8475には、値が100Ωの2つの抵抗と1μFのコンデンサで構成される単極差動RCフィルタが付加されています。これは、AD7192に対するカットオフ周波数が800Hzのアンチエイリアシング・フィルタ/ノイズ低減フィルタとして機能します。値が10nFの2つのコンデンサは、カットオフ周波数が160kHzのコモン・モード・フィルタとして機能します。

フィルタ、出力データ・レート、セトリング・タイム

ΣΔ方式のADCであるAD7192は、変調器とその後段のデジタル・フィルタで構成されています。その出力データ・レート(fADC)とセトリング・タイム(tSETTLE) は、フィルタとチョップの設定に依存します。表2に、各種設定における出力データ・レートとセトリング・タイムの算出式を示します。

| チョップとフィルタの設定 | SINC3 | SINC4 |

| ディスエーブル | fADC = fCLK/(1024 × FS[9:0]) tSETTLE = 3/fADC |

fADC = fCLK/(1024 × FS[9:0]) tSETTLE = 4/fADC |

| イネーブル | fADC = fCLK/(3 × 1024 × FS[9:0]) tSETTLE = 2/fADC |

fADC = fCLK/(4 × 1024 × FS[9:0]) tSETTLE = 2/fADC |

レイアウトに関する検討事項

図 1 の回路を含めて、高速または高分解能の回路の性能は、プリ ント回路基板のレイアウトが適切に行われているかどうかに大 きく依存します。注意すべきポイントは、電源のバイパス、信号 の配線、電源プレーンとグラウンド・プレーンのレイアウト設計 です(ただし、これらだけに注意すればよいというわけではあり ません)。プリント回路基板のレイアウトについて、詳細は 「MT-031」、「MT-101」、「 高速プリント回路基板 レイアウトの実務ガイド」を参照してください。

システム性能

ΣΔ方式の 24 ビットADC であるAD7192 は、この回路において 非常に優れた性能を発揮します。ΣΔ方式ADC の詳細について は、 MT-022 と MT-023 を参照してくださ い。

図2、図3 に、AD7192 のサンプル500 個についての評価結果を示しました。図2 はノイズ性能、図3 はノイズのヒストグラムです。これらは、チョップをディスエーブル、出力データ・レートを4.7Hz、ゲインを1 に設定し、SINC4 フィルタを選択するという条件で測定しました。図1 の回路で測定されたピークto ピーク・ノイズは約3.9μV(図2 参照)で、RMS(実効値)ノイズは860nV です。これらは、20 ビットのピークto ピーク(ノイズフリー・コード)分解能と23 ビットのRMS 分解能に相当する値です。 表に、AD7192 において、チョップをディスエーブルとしてSINC4 フィルタを選択し、データ・レートとゲインをいくつかの値に設定した場合のRMS ノイズの値をまとめました。

| フィルタ・ワード (10進数) | 出力データレート (Hz) | セトリング・タイム (ms) | Gain 1 | Gain 8 | Gain 16 | Gain 32 | Gain 64 | Gain 128 |

| 1023 | 4.7 | 852.5 | 23.0 | 21.8 | 20.4 | 19.7 | 18.8 | 17.4 |

| 640 | 7.5 | 533 | 22.5 | 21.5 | 20.0 | 19.5 | 18.5 | 17.2 |

| 96 | 50 | 80 | 22.3 | 20.9 | 19.8 | 19.3 | 18.2 | 17.0 |

| 16 | 300 | 13.3 | 21.8 | 20.2 | 19.3 | 18.6 | 17.6 | 16.8 |

| 5 | 960 | 4.17 | 20.9 | 19.8 | 18.9 | 18.0 | 17.2 | 16.2 |

| 1 | 4800 | 0.83 | 19.2 | 19.0 | 18.4 | 17.6 | 16.6 |

15.8 |

バリエーション回路

PGA を内蔵し、分解能が24 ビット以下のほかのΣΔ方式ADCを使用することができます。具体的には、 AD7190、 AD7193、 AD7797、 AD7799などが該当します。また、入力信号の 減衰が不要な場合には、「AD8476」を使用することで、AD8475を使用する場合よりも消費電力を抑えることが可能です。

減衰や高い入力インピーダンスが不要な場合には、AD7192 をセ ンサーに直接接続することで、コンディショニング用のアナロ グ・フロントエンド回路によって生じるノイズを低減することが 可能です。例えば、ロードセルはフルスケールの出力電圧が小さ いので、減衰は不要です。そのため、AD7192 の差動入力に直接 接続することができます(CN-0102, CN-0107, CN-0108, CN-0118, CN-0119, CN-0155を参照してください)。

回路の評価とテスト

図 1 の回路の評価/ テストには、回路評価基板である 「EVAL-CN0251-SDPZ」とシステム・デモンストレーション・プ ラットフォーム(SDP)の評価基板である「EVAL-SDP-CB1Z」 を利用することができます。EVAL-CN0251-SDPZ には、このド キュメントで説明した回路が実装されています。2 つの基板は、 整合性のある120 ピンのコネクタを備えており、迅速に設定を 行って回路の性能を評価することが可能です。具体的には、SDP とCN-0251 の評価ソフトウェアを共に使用することによって、 EVAL-CN0251-SDPZ からのデータを取得します。SDP は、入力 マルチプレクサとAD7192 の多様な機能の制御にも使用します。

必要な装置など

評価/テストには、以下の装置類が必要となります。

- USB ポートを備え、Windows XP、Windows Vista(32 ビット 版)、Windows 7(32 ビット版)のいずれかを搭載するPC

- 回路評価基板: EVAL-CN0251-SDPZ

- SDP 評価基板: EVAL-SDP-CB1Z SDP

- DC 電源電圧:15V、-15V、6V

- CN-0251 の評価ソフトウェア

作業の準備

CN-0251 の評価ソフトウェアを収録したCD をPC のCD ドライ ブに挿入し、評価ソフトウェアをロードします。PC 上でそのCD ドライブに移動し、Readme ファイルを開きます。Readme ファイ ルに書かれた指示に従い、評価ソフトウェアをインストールして 使用してください。

機能ブロック図

図 4 に、評価/テストを行うための設定を機能ブロック図として 示します。EVAL-CN0251-SDPZ の詳細な回路図については、 EVAL-CN0251-SDPZ-SCH.pdf を参照してください。このPDF ファイルは、CN-0251 設計サポート・パッケージ CN0251-DesignSupportに含まれています。

セットアップ

EVAL-CN0251-SDPZ の120 ピン・コネクタをEVAL-SDP-CB1Z (SDP)のCONA コネクタに接続します。ナイロン製の留め具を 使用し、120 ピン・コネクタの末端にある穴を利用して2 つの基 板をしっかりと固定してください。DC電源の出力を15V、-15V、 6V に設定したら、いったん電源をオフにします。

電源をオフにした状態で、15V の電源をJ3 の+15VA ピン、-15V の電源をJ3 の-15VA ピン、GND をJ3 のAGND ピンに接続しま す。また、電源をオフにしたままで、6V の電源をJ2 に接続しま す。次に電源をオンにして、SDP のUSB ケーブルをPC のUSB ポートにつなぎます。EVAL-CN0251-SDPZ のDC 電源をオンに するまでは、USB ケーブルはSDP のmini-USB コネクタに接続し ないでください。

テスト

電源を設定して EVAL-CN0251-SDPZ に接続したら、評価ソフト ウェアを起動し、PC からのUSB ケーブルをSDP のmini-USB コ ネクタに接続します。アナログ・デバイセズのシステム開発プ ラットフォーム・ドライバがデバイス・マネージャに表示されて いれば、ソフトウェアはSDP基板と通信を行うことができます。

USB による通信がいったん確立されれば、SDP を使用して EVAL-CN0251-SDPZ からのシリアル・データの送信/受信/取り込 みを行うことができます。続いて、測定用の信号源を接続してく ださい。