AD9213

RECOMMENDED FOR NEW DESIGNS12-Bit, 10.25 GSPS, JESD204B, RF Analog-to-Digital Converter

- Part Models

- 2

- 1ku List Price

- Starting From $1346.79

Overview

- High instantaneous dynamic range

- NSD

- −155 dBFS/Hz at 10 GSPS with −9 dBFS, 170 MHz input

- −153 dBFS/Hz at 10 GSPS with −1 dBFS, 170 MHz input

- SFDR: 70 dBFS at 10 GSPS with −1 dBFS, 1000 MHz input

- SFDR excluding H2 and H3 (worst other spur): 89 dBFS at 10 GSPS with −1 dBFS, 1000 MHz input

- Low power dissipation: <4.6 W typical at 10 GSPS

- Integrated input buffer (6.5 GHz input bandwidth)

- 1.4 V p-p full-scale analog input with RIN = 50 Ω

- Overvoltage protection

- 16-lane JESD204B output (up to 16 Gbps line rate)

- Multichip synchronization capable with 1 sample accuracy

- DDC NCO synchronization included

- Integrated DDC

- Selectable decimation factors

- 16 profile settings for fast frequency hopping

- Fast overrange detection for efficient AGC

- On-chip temperature sensor

- On-chip negative voltage generators

- Low CER: <1 × 10−16

- 12 mm × 12 mm, 192-ball BGA-ED package

The AD9213 is a single, 12-bit, 6 GSPS/10.25 GSPS, radio frequency (RF) analog-to-digital converter (ADC) with a 6.5 GHz input bandwidth. The AD9213 supports high dynamic range frequency and time domain applications requiring wide instantaneous bandwidth and low conversion error rates (CER). The AD9213 features a 16-lane JESD204B interface to support maximum bandwidth capability.

The AD9213 achieves dynamic range and linearity performance while consuming <4.6 W typical. The device is based on an interleaved pipeline architecture and features a proprietary calibration and randomization technique that suppresses interleaving spurious artifacts into its noise floor. The linearity performance of the AD9213 is preserved by a combination of on-chip dithering and calibration, which results in excellent spurious-free performance over a wide range of input signal conditions.

Applications that require less instantaneous bandwidth can benefit from the on-chip, digital signal processing (DSP) capability of the AD9213 that reduces the output data rate along with the number of JESD204B lanes required to support the device. The DSP path includes a digital downconverter (DDC) with a 48-bit, numerically controlled oscillator (NCO), followed by an I/Q digital decimator stage that allows selectable decimation rates that are factors of two or three. For fast frequency hopping applications, the AD9213 NCO supports up to 16 profile settings with a separate trigger input, allowing wide surveillance frequency coverage at a reduced JESD204B lane count.

The AD9213 supports sample accurate multichip synchronization that includes synchronization of the NCOs. The AD9213 is offered in a 192-ball ball grid array (BGA) package and is specified over a junction temperature range of −20°C to +115°C.

Documentation

Data Sheet 1

User Guide 2

Technical Articles 5

Evaluation Design File 1

Video 1

Device Drivers 1

3rd Party Solutions 1

Analog Dialogue 4

Webcast 3

ADI has always placed the highest emphasis on delivering products that meet the maximum levels of quality and reliability. We achieve this by incorporating quality and reliability checks in every scope of product and process design, and in the manufacturing process as well. "Zero defects" for shipped products is always our goal. View our quality and reliability program and certifications for more information.

| Part Model | Pin/Package Drawing | Documentation | CAD Symbols, Footprints, and 3D Models |

|---|---|---|---|

| AD9213BBPZ-10G | 192-Ball BGA_ED (12mm x 12mm x 1.56mm w/ EP) | ||

| AD9213BBPZ-6G | 192-Ball BGA_ED (12mm x 12mm x 1.56mm w/ EP) |

This is the most up-to-date revision of the Data Sheet.

Software Resources

Device Drivers 1

Evaluation Software 0

Can't find the software or driver you need?

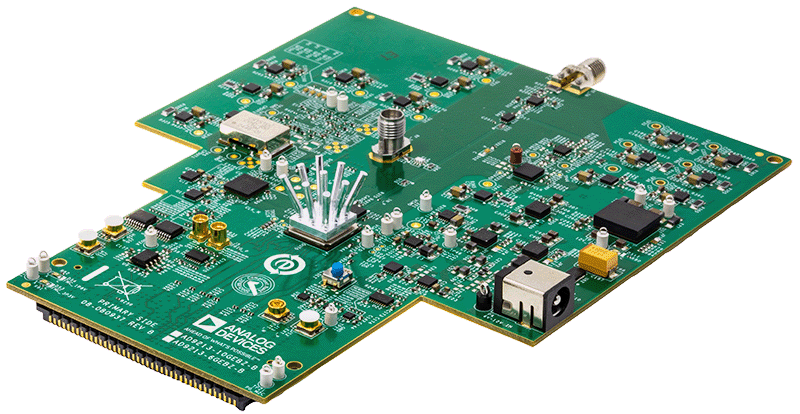

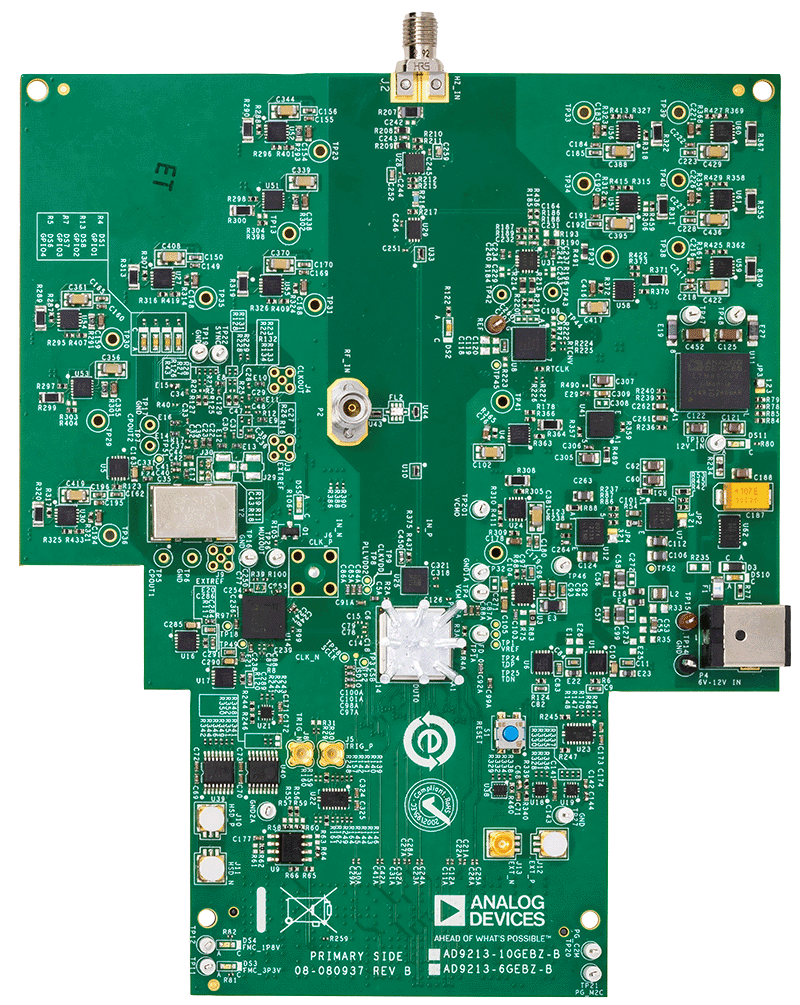

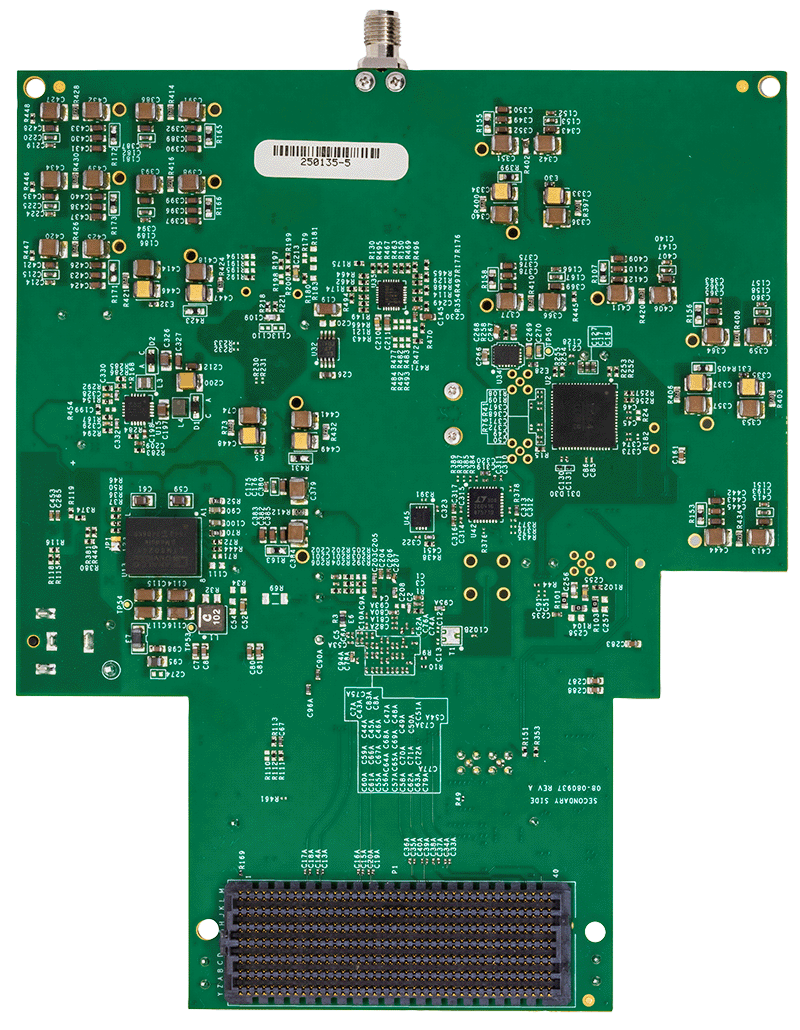

Hardware Ecosystem

| Parts | Product Life Cycle | Description |

|---|---|---|

| Clock ICs 2 | ||

| HMC7044 | RECOMMENDED FOR NEW DESIGNS | High Performance, 3.2 GHz, 14-Output Jitter Attenuator with JESD204B and JESD204C Support |

| LTC6952 | LAST TIME BUY | Ultralow Jitter, 4.5GHz PLL with 11 Outputs and JESD204B / JESD204C Support |

| Fanout Buffers 1 | ||

| LTC6955 | LAST TIME BUY | Ultralow Jitter, 7.5GHz, 11 Output Fanout Buffer Family |

| LDO Linear Regulators 5 | ||

| LT3042 | RECOMMENDED FOR NEW DESIGNS | 20V, 200mA, Ultralow Noise, Ultrahigh PSRR RF Linear Regulator |

| ADP7158 | RECOMMENDED FOR NEW DESIGNS | 2 A, Ultralow Noise, High PSRR, Fixed Output, RF Linear Regulator |

| ADP1764 | RECOMMENDED FOR NEW DESIGNS | 4 A, Low VIN, Low Noise, CMOS Linear Regulator |

| ADP172 | RECOMMENDED FOR NEW DESIGNS | 300 mA, Low Quiescent Current, CMOS Linear Regulator |

| LT3045 | RECOMMENDED FOR NEW DESIGNS | 20V, 500mA, Ultralow Noise, Ultrahigh PSRR Linear Regulator |

| Phase-Locked Loop (PLL) Synthesizers 1 | ||

| ADF4377 | RECOMMENDED FOR NEW DESIGNS | Microwave Wideband Synthesizer with Integrated VCO |

| Switching Regulators & Controllers 2 | ||

| LTM4622A | RECOMMENDED FOR NEW DESIGNS | Dual Ultrathin 2A or Single 4A Step-Down DC/DC μModule Regulator |

|

LTM4644 LTM4644-1 |

Quad DC/DC μModule (Power Module) Regulator with Configurable 4A Output Array | |

Tools & Simulations

IBIS Model 1

AD9213 AMI Download

Open ToolAD9213 Remote Evaluation Tool

This tool gives users access to a live AD9213 evaluation board in an Analog Devices lab, connected to signal and clock generators, and an ADS8-V1EBZ FPGA board for data capture. The user is able to run tests on this remote lab bench to evaluate the AD9213 performance at any time, day or night. It is a great way to check performance of the product before, or in lieu of, purchase of an evaluation board. This tool can also be used to compare performance to a user-designed board.

Open ToolS-Parameter 1

Software and Simulation 1

LTspice® is a powerful, fast and free simulation software, schematic capture and waveform viewer with enhancements and models for improving the simulation of analog circuits.