概览

设计资源

设计与集成文件

• Schematic• Bill of Materials

• Gerber Files

• Layout Files (PADs)

• Assembly Drawing 下载设计文件 1.54 M

评估硬件

产品型号带"Z"表示符合RoHS标准。评估此电路需要下列选中的电路板

- ADL5801-EVALZ ($198.11) ADL5801-EVALZ

- EV-ADF4355-2SD1Z ($424.52) EV-ADF4355-2SD1Z

- EVAL-CN0369SDPZ ($369.15) EVAL-CN0369SDPZ

- EVAL-SDP-CS1Z ($66.32) Eval Control Board

优势和特点

- 转换环路频率合成器

- 5GHz至5.4GHz RF输出

- 低相位噪声

产品类别

领域和技术

所用产品

参考资料

-

UG-806: Evaluating the EVAL-CN0369SDPZ (Rev. 0)2016/12/14PDF349 K

-

CN-0369:低相位噪声的转换锁相环频率合成器 (Rev. 0)2016/12/22PDF496 K

电路功能与优势

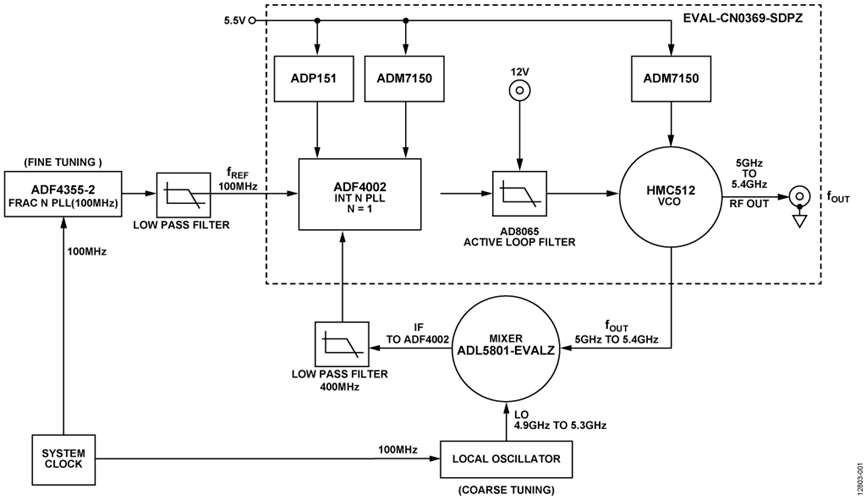

图1所示电路框图是一个低相位噪声转换环路频率合成器(也称为偏移环路)。此电路将ADF4002 锁相环 (PLL) 的较低100 MHz参考频率转换到5.0 GHz至5.4 GHz的较高频率范围,后一频率由本振 (LO) 频率决定。

与仅采用PLL的频率合成器相比,转换环路频率合成器的相位噪声非常低 (<50 fs)。相位噪声之所以很低,是因为ADF4002整数N分频PLL使用的N值非常低,该N值用于控制压控振荡器 (VCO)。本例中,ADF4002鉴频鉴相器 (PFD) 运行频率为100 MHz,N = 1,所产生的相位噪声性能不受PLL的N值限制。

电路描述

在标准PLL和VCO频率合成器系统中,低相位噪声一般是主要目标。PLL的相位噪声可用两个分量来描述:一个是平坦噪声分量,即所谓PLL品质因数 (FOM);另一个是1/f噪声曲线分量,即所谓PLL 1/f或闪烁噪声。

PLL噪底PNTOT1由下式给出:

其中:

PNSYNTH为频率合成器FOM,是器件特定的。

N为PLL所用的分频比。

fPFD为鉴频鉴相器的频率。

N值为1的PLL的噪底为 10log10(fPFD).

PLL 1/f噪声PNTOT2由下式给出:

其中:

PN1/f为数据手册中相对于输出RF频率偏移10 kHz时的PLL 1/f噪声(归一化到1 GHz输出)。

fRF为输出RF频率。

PLL总噪声PNTOT由下式给出:

此等式表明噪声源以和方根形式相加;因此,总噪声以较大噪声源为主。

N值非常低的PLL,其相位噪声以PLL 1/f噪声为主。

转换环路频率合成器根据N分频器值解耦所需的通道间隔,从而优化PLL的相位噪声。在这个转换环路频率合成器例子中,N = 1。

图1中的转换环路频率合成器将较高频率4.8 GHz至5.2 GHz VCO锁定至100 MHz fREF信号。 ADL5801 混频器和LO共同执行此PLL的分频功能。

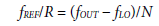

LO在反馈环路中,ADF4002 PLL的平衡方程变为:

其中N和R分别为N和R分频器值(本电路中,R = 1且N = 1)

因此,输出频率为:

ADF4355-2 小数N分频频率合成器

本电路中的 ADF4355-2为转换环路提供参考频率 (fREF),如图2所示。

ADF4355-2是一款集成VCO的宽带频率合成器,提供55 MHz到4400 MHz的输出频率范围。ADF4355-2使用38位高分辨率模数,可以实现非常精细的频率分辨率,无频率残差。本电路中的ADF4355-2使用50 MHz的PFD和100 kHz的环路带宽。利用ADI公司的ADIsimPLL工具来设计和仿真环路滤波器。图3显示了ADIsimPLL仿真的相位噪声性能。100 kHz的环路带宽 (LBW) 足以让ADF4355-2实现所需的精密频率调谐。

本设计中的ADF4355-2以6400 MHz的内部VCO频率工作。该高VCO频率用最大分频值64分频后,产生100 MHz RF输出频率。在VCO输出端增加一个分频器可改善相位噪声性能,每2分频提高6 dB。分频后的VCO输出包含分频过程固有的谐波。在ADF4355-2的RF输出端插入一个100 MHz低通滤波器以滤除这些谐波。

偏移10 kHz时,仿真相位噪声为−137 dBc。对于此转换环路,ADF4355-2是优选参考器件,因为其具有非常低的相位噪声和非常精密的输出频率分辨率。

图4显示了在 EV-ADF4355-2SD1Z RFOUTA获得的相位噪声曲线。

ADF4002转换环路频率合成器

ADF4002 为转换环路频率合成器,以100 MHz的高PFD频率和最小N = 1工作。以高PFD频率工作可减少参考杂散并降低N值,从而降低相位噪声。为获得更好的杂散性能,转换环路频率合成器使用整数N分频PLL操作,而不是小数N分频。ADF4002满足整数N分频操作、低最小N值和良好相位噪声性能的要求。精密调谐由参考源提供,故无需小数N分频。本电路中,ADF4002的RF输入由 ADL5801 混频器的100 MHz IF输出驱动。

ADF4002内部电荷泵的电源电压为5 V。然而,许多宽带VCO要求最高18 V的调谐电压。驱动9.6 GHz至10.8 GHz VCO需要2 V至12 V的调谐电压。为此,必须使用有源环路滤波器。有源滤波器将ADF4002的输出调谐范围乘以运算放大器的增益。

ADF4002支持可编程电荷泵电流特性,用户可以在不改变物理元件的情况下更改环路滤波器动态特性。本电路中,LBW为1 MHz,使用的电荷泵电流为5 mA。若要降低或提高LBW,可以更改电荷泵电流,而无需实际改变环路滤波器元件。

采用AD8065构建有源滤波器

运算放大器 AD8065 具有24 V电源电压范围、大约145 MHz的增益带宽积 (GBP) 和低噪声特性 (7 nV/√Hz)。这些特性使它成为有源滤波器的理想选择。对于本应用,12 V电源电压用于AD8065即足以提供所需的输出摆幅。

对于大多数PLL应用,相位裕量建议设置为45°至55°,以便维持稳定的环路并使建立时间更短。在有源环路滤波器中(即环路滤波器中有一个运算放大器),有一个额外的极点出现在运算放大器的单位增益频率(或增益带宽积)处。此额外极点会带来额外的相位滞后;因此,根据极点的频率,它可能会使环路变得不稳定。

GBP与LBW的比值越大,相位滞后越少。例如,根据表1所示,GBP/LBW比值为10时,相位裕量降低5.7°。如果GBP/LBW比值过低,相位裕量也会变得过低,导致环路不稳定。

| GBP/LBW 比 | 额外相位滞后 (°) |

| 5 (例如:GBP = 1 MHz, LBW = 200 kHz) | 11.3 |

| 10 | 5.7 |

| 20 | 2.9 |

此电路使用1 MHz LBW;因此,AD8065的145 MHz GBP引起的相位滞后可忽略不计 (GBP/LBW = 145)。

AD8065还充当一个缓冲器,用以降低VCO输入电容的影响。

HMC512 VCO

ADF4002 PLL将100 MHz参考频率锁定至HMC512 VCO频率。HMC512 的主要频率范围为9.6 GHz至10.8 GHz。本电路中,RFOUT/2用于输出信号 (fOUT) 以及反馈到混频器的RF信号。RF输出 (fOUT) 和混频器之间需要高反向隔离性能,以使LO到RF泄漏更小。选择一个带半频率输出的VCO。

宽环路滤波器带宽会让环路滤波器带宽内的高频VCO噪声通过。在环路滤波器带宽之外,VCO噪声占主导地位。因此,为实现该电路的低相位噪声优势,必须使用低噪声VCO。HMC512在100 kHz时的噪声低至−110 dBc/Hz,并具有半频率输出,因此它是理想的VCO选择,适合本电路中产生5.0 GHz至5.4 GHz输出的需要。

本振和ADL5801混频器

转换环路的混频器选择必须满足如下要求:

- 在所需频率范围中工作

- LO功率水平与LO源匹配

- 高RF至LO隔离度

- 低噪声系数

ADL5801 满足上述要求。

图5显示了ADL5801混频器和本振的框图。一般而言,诸如ADL5801(10 MHz至6000 MHz)之类的有源混频器可提供所需的宽带操作、35 dB至40 dB的端口间隔离,并支持−6 dBm至0 dBm的典型LO驱动。LO泄漏会降低输出信号的频谱纯度。低LO驱动加上端口间隔离可使LO到RF和LO到IF泄漏更小。

本振提供100 MHz步长的输出频率粗调功能,其相位噪声非常低。对于本电路评估,LO功能由R&S SMA100等工作台信号发生器提供。

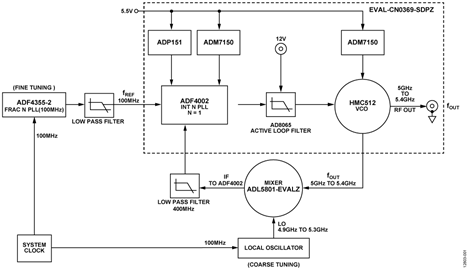

转换环路设计与性能

此转换环路的核心是EVAL-CN0369-SDPZ板。图6所示为EVAL-CN0369-SDPZ的框图,其采用ADF4002 PLL、AD8065有源环路滤波器和HMC512 VCO。有源环路滤波器的组成元件如此图所示。 ADIsimPLL 用来设计该有源环路滤波器。

ADIsimPLL软件还用来设计转换环路PLL的环路滤波器。

利用ADIsimPLL设计转换环路的简单办法是用等效VCO代替VCO/混频器/滤波器模块。如果所用VCO利用KV = 150 MHz/V将频率从5.0 GHz调谐到5.4 GHz,并且用户将其与4.9 GHz至5.3 GHz本振混频,则PLL看到的是VCO利用KV = 150 MHz/V将频率从400 MHz调谐到100 MHz。

图7显示了ADIsimPLL仿真相位噪声及对应的原理图(使用ADF4002),并且指示PLL环路锁定在100 MHz,相位噪底增幅极小。

转换环路:实测相位噪声结果与独立PLL

利用图1所示配置,fOUT rms抖动测量结果小于50 fs,如表2所示。

在表2中,fREF是EVAL-CN0369-SDPZ的参考输入,来自ADF4255-2评估板。fREF为转换环路提供精调。本振为ADL5801-EVALZ混频器评估板的LO,为转换环路提供粗调。fOUT为ADL5801-EVALZ混频器评估板的LO,为转换环路提供粗调。fOUT为来自EVAL-CN0369-SDPZ的VCO/2 RF输出。

| fREF(MHz | 本振 (MHz) | fOUT频率 (MHz) | fOUTRMS 抖动 (fs) |

| 100.00 | 5300.00 | 5400.00 | 43 |

| 100.00 | 5200.00 | 5300.00 | 39 |

| 100.00 | 5100.00 |

5200.00 | 43 |

| 101.01 | 5100.00 |

5201.11 | 43 |

图8为来自转换环路的fOUT的相位噪声曲线。为显示转换环路的精密调谐性能,图8中使用的参考 (fREF) 输入为101.011 MHz。

图8中的fOUT rms抖动测量结果小于39 fs(从1 kHz积分到30 MHz)。

ADF4355-2用作独立PLL来产生类似的频率时,fOUT rms抖动测量结果在200 fs到250 fs之间,如表3所示。

对于表3所示数据,fREF 为EV-ADF4355-2SD1Z评估板的低噪声REFIN源。fOUT为EV-ADF4355-2SD1Z的RFOUTA(+)。RFOUTA(−) 连接到一个50 Ω端接电阻。

| fREF (MHz) | fOUT 频率 (MHz) | fOUT RMS 抖动 (fs) |

| 100.00 | 5400.00 | 202 |

| 100.00 | 5300.00 | 220 |

| 100.00 | 5200.00 |

243 |

| 100.00 | 5201.11 |

222 |

电路评估与测试

本电路采用EVAL-CN0369-SDPZ电路板、 EV-ADF4355-2SD1Z评估板和ADL5801-EVALZ评估板。两片EVAL-SDP-CS1Z系统演示平台(SDP-S)板配合EVAL-CN0369-SDPZ电路板和EV-ADF4355-2SD1Z评估板使用。这两片板具有120引脚的对接连接器,支持快速完成设置并评估电路性能。连接到EVAL-CN0369-SDPZ电路板的SDP-S板配合整数N分频评估软件使用,以对ADF4002片内寄存器进行编程。

连接到EV-ADF4355-2SD1Z板的SDP-S板配合ADF4355-2评估软件使用,以对ADF4355-2片内寄存器进行编程。

如需获得EVAl-CN0369-SDPZ板的全套文档,包括原理图、布局文件和物料清单,请参阅CN-0369设计支持包。

开始使用

有关软件安装和测试设置,请参阅EVAL-CN0369-SDPZ用户指南(UG-806)。

设备要求

需要以下设备:

- 带USB端口且运行Windows® XP、Windows Vista(32位)或Windows 7(32位)的PC

- EVAL-CN0369-SDPZ电路评估板

- EV-ADF4355-2SD1Z 评估板

- 两片 EVAL-SDP-CS1Z SDP-S板

- Integer-N v7 和ADF4355评估软件

- 电源:5 V、5.5 V和12 V

- 两个RF信号源(R&S SMA100或同等器件)

- 频谱分析仪(Agilent FSUP或同等设备)

- TTE 400 MHz低通滤波器(或同等器件)

- Mini Circuits 100 MHz低通滤波器(或同等器件)

功能框图

功能框图参见图1。测试设置的框图如图9所示。

设置与测试

设置设备后,使用标准RF测试方法测量电路的相位噪声和相位抖动。