概览

设计资源

评估硬件

产品型号带"Z"表示符合RoHS标准。评估此电路需要下列选中的电路板

- EVAL-AD7091RSDZ ($83.49) 12-Bit ,1 MSPS SAR ADC and Driver with Total Power Dissipation Less than 5 mW

- EVAL-SDP-CB1Z ($134.00) Eval Control Board

优势和特点

- 12位、1MSPS数据采集

- 单电源

- 5mW功率

参考资料

-

MT-101:去耦技术2013/11/5PDF954 kB

-

MT-036:运算放大器输出相位反转和输入过压保护2013/3/27PDF1006 kB

-

MT-031: Grounding Data Converters and Solving the Mystery of "AGND" and "DGND"2009/3/20PDF144 kB

-

CN0247:12位、1 MSPS、单电源、低功耗数据采集系统2014/3/28PDF351 kB

电路功能与优势

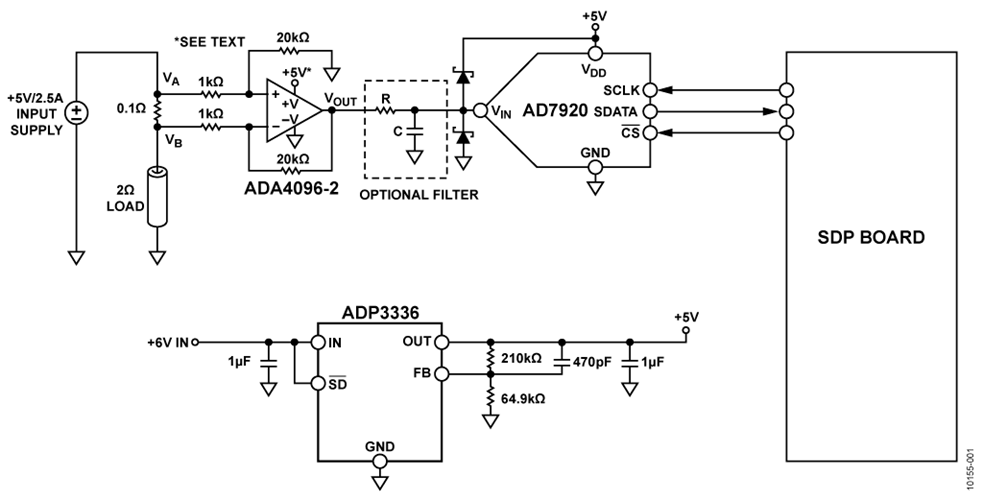

图1中的电路是超低功耗数据采集系统,使用了AD7091R 12位、1 MSPS SAR ADC和 AD8031 运算放大器驱动器,电路的总功耗低于5 mW,采用3 V单电源供电。

所选器件的低功耗和小封装尺寸使得这种组合成为业界较领先的便携式电池供电系统解决方案,在这种系统中功耗、成本和尺寸极为关键。

当VDD引脚为3 V时,AD7091R的电源电流典型值仅为350μA,远低于目前市场上的任何ADC竞争产品。这意味着典型功耗约为1 mW。

AD8031仅需800μA的电源电流,电源电压为3 V时的典型功耗为2.4 mW,在10 kHz模拟输入信号下以1 MSPS的速率进行采样时,系统总功耗低于5 mW。

电路描述

针对模拟信号,大多数SAR ADC需要合适的输入缓冲器以获得优质性能。当内部采样保持开关从保持切换到采样时,缓冲器可将信号源与ADC输入产生的瞬变相互隔离。驱动ADC的缓冲器必须从该瞬变中恢复,并在ADC采集时间之内建立至所需精度。这在信号源具有高阻抗,并且低失真和高信噪比极为关键的应用中尤为重要。因此,选择合适的缓冲器运算放大器便成为该设计中极为重要的一个环节。

AD7091R是一款12位、快速、超低功耗、单电源供电ADC,集成2.5 V内部基准电压源。该器件可采用2.7V至5.25V电源供电。AD7091R的吞吐速率可达1MSPS。当输入信号为10kHz、采样速率为1MSPS时,该器件的总功耗约为2.3 mW。

在无需1MSPS采样频率的应用中,这一数字将下降,因为AD7091R的功耗与吞吐速率成正比,如表1所示。

可通过降低转换器的吞吐速率而进一步降低功耗。表1显示当电源为3 V且器件工作在普通模式下,AD7091R的典型功耗与吞吐速率的关系。

表1表示激活关断模式后可减少的功耗。当AD7091R工作在较低的吞吐速率时,关断模式对于大幅度降低电源需求极为有效。

AD7091R采用小型3 mm×2 mm、10引脚LFCSP或3 mm ×5 mm、10引脚MSOP封装。两款封装与同类竞争解决方案相比,大幅度节省了空间。

AD8031是一款低功耗轨到轨输入/输出运算放大器,是非常适合AD7091R的驱动放大器。 AD8031采用2.7V至1 V电源供电,支持通过一个供电轨驱动两个IC。AD8031带宽为80MHz,压摆率为30V/μs,达到0.1%精度的建立时间为125 ns。

当采用单电源工作时,AD8031的输出可达负供电轨的20mV以内。若需要0V输入下的线性度,则AD8031需要一个额外的负电源(参考指南MT-035)。

图1显示了简化电路图。使用100 nF和10μF陶瓷电容可对IC电源引脚实现良好的接地去耦。将这些电容放置于尽可能靠近两个IC的电源引脚的位置。

切记,该ADC的模拟输入信号不能超过供电轨300 mV以上。如果信号超过此电平,内部ESD保护二极管将呈正偏,并开始向基板内传导电流。二极管的最大导通电流为10 mA,该电流以下不会导致不可恢复的器件损坏。可通过在VIN和AD7091R的电源供电轨之间连接一对肖特基二极管达到保护的作用,如 指南MT-036 中所描述。

AD7091R集成了一个内部2.5 V基准电压。针对REFIN/REFOUT引脚的良好去耦可达到指定的性能。REFIN/REFOUT电容的典型值为2.2μF。注意可通过外部加载内部基准电压。

若使用了外部基准电压,则该电压范围必须为2.7V至VDD,并且必须连接REFIN/REFOUT引脚。调节器旁路(REGCAP)去耦电容的典型值为1μF。

施加于VDRIVE输入的电压控制串行接口的逻辑电平电压。将该引脚连接至逻辑系列的电源电压,该电源电压与AD7091R数字输出相连。可将VDRIVE设为1.8 V至VDD范围内的值。VDRIVE去耦电容的典型值为100nF,与10μF并联。

若需忙碌指示功能,可在VDRIVE和SDO引脚之间连接一个100kΩ的上拉电阻。

用于缓冲AD7091R模拟输入的AD8031被配置成一个单位增益缓冲器。在运算放大器的输出级后面连接一个单极点RC滤波器,以降低带外噪声。RC滤波器的截止频率设为660kHz。然而,根据系统吞吐速率的要求,该参数可能有所不同。对于AD7091R未工作在最大吞吐速率下的系统,可降低滤波器的截止频率。取决于模拟信号的输入幅度和失调,可将AD8031运算放大器配置成提供增益、衰减和电平转换,以匹配ADC模拟输入范围的输入信号摆幅。

| 模式 |

IDD |

IDRIVE |

IAMP (µA) |

总电流 (µA) |

总功耗 (mW) |

| 关断 |

550 nA |

36 nA |

766 |

767 |

2.3 |

| 静态(上电、输入接地、无时钟) |

21 µA |

81 nA |

766 |

787 |

2.4 |

| 工作(上电、10 kHz输入、1 MSPS采样) |

368 µA |

406 µA |

766 |

1540 |

4.6 |

| 工作(上电、输入接地、1 MSPS采样) |

344 µA |

35 µA |

766 |

1145 |

3.4 |

| 工作(上电、输入接地、1 kSPS采样) |

57.8 µA |

18.9 µA |

766 |

843 |

2.5 |

注意,采样时转换开始脉冲宽度 = 20 ns,VDD =VDRIVE = 3 V.

图2和图3表示电路的积分非线性(INL)和微分非线性(DNL)曲线。注意INL和DNL低于±1 LSB。

图4表示针对8192个样本计算的FFT数据;采样速率为1MSPS,模拟输入频率为10 kHz。SNR为70.44 dBFS。

该电路必须构建在具有较大面积接地层的多层印刷电路板(PCB)上。为实现优质性能,必须采用适当的布局、接地和去耦技术(请参考 指南MT-031、 指南MT-101以及CN-0247设计支持包中展示 AD7091R评估板布局)。

根据应用和传感器的具体要求,可以更改AD7091R和AD8031周围的器件值。例如,可配置缓冲器以提供增益和失调,并且RC滤波器的截止频率可根据采样频率和输入频率而变化。

有关完整的文档包,包括原理图、电路板布局以及物料清单(BOM), 请参考https://www.analog.com/CN0247-DesignSupport

电路评估与测试

为了评估和测试 AD7091R与本电路笔记所述电路,我们开发了评估板 EVAL-AD7091RSDZ 。有关详细的原理图和用户指南,请参考 EVAL-AD7091RSDZ文档。图5显示测试设置的功能框图。

设备要求

为测试该电路,需要如下设备:

- EVAL-AD7091RSDZ评估板(包括软件和9 V直流壁式电源适配器)

- EVAL-SDP-CB1Z 系统演示平台电路板

- 一个低失真信号发生器,如Agilent 81150A或Audio Precision System Two 2322

- 带USB 2.0端口的PC,运行Windows® XP、Windows Vista或Windows 7(32位或64位)

- 电源:9 V直流壁式电源适配器(包括在评估板中,外部3 V / 50 mA直流电源

设置

连接任何硬件之前,确保 EVAL-AD7091RSDZ评估板上的连接位置如下:

- LK1:位置A(选择 AD8031作为输入缓冲器)

- LK2:位置A(输入J5连接至输入缓冲器)

- LK5:位置A(使能外部VDRIVE 源)

- LK6:位置B(使能外部 VDD 源)

之后,根据评估板文档中所述连接硬件并安装软件。

测试

请参考评估板文档,查看如何运行本电路笔记中所述各种测试的完整描述。