概要

設計リソース

評価用ボード

型番に"Z"が付いているものは、RoHS対応製品です。 本回路の評価には以下の評価用ボードが必要です。

- EVAL-CFTL-6V-PWRZ ($23.01) Wall Power Supply for Eval Board

- EVAL-CN0187-SDPZ ($67.68) Crest Factor, Peak, and RMS RF Power Measurement Circuit Optimized for High Speed, Low Power, and Single 3.3 V Supply

- EVAL-SDP-CB1Z ($134.00) Eval Control Board SDP

デバイス・ドライバ

コンポーネントのデジタル・インターフェースとを介して通信するために使用されるCコードやFPGAコードなどのソフトウェアです。

機能と利点

- クレスト・ファクタ、ピーク、RMS RF 電力の測定

- 広い任意の周波数 : 450MHz ~ 6GHz

- 低電力RFモニタを最適化

製品カテゴリ

マーケット & テクノロジー

使用されている製品

参考資料

-

CN0187 Software User Guide2018/10/18WIKI

-

MT-081: RMS-to-DC Converters2015/02/14PDF230 K

-

High Frequency Log Amps2015/02/14PDF144 kB

-

MT-101: Decoupling Techniques2015/02/14PDF954 kB

-

MT-073: High Speed Variable Gain Amplifiers2015/02/14PDF177 kB

-

MT-031: データ・コンバータのグラウンディングと、「AGND」および「DGND」に関する疑問の解消2009/03/20PDF144 kB

-

Design and Operation of Automatic Gain Control Loops for Receivers in Modern Communication Systems2003/10/10PDF129 kB

-

CN-0187: 高速、低消費電力、3.3 V単電源の条件に最適なクレスト・ファクタ、ピーク、RMS RF電力の測定回路2011/07/26PDF651 kB

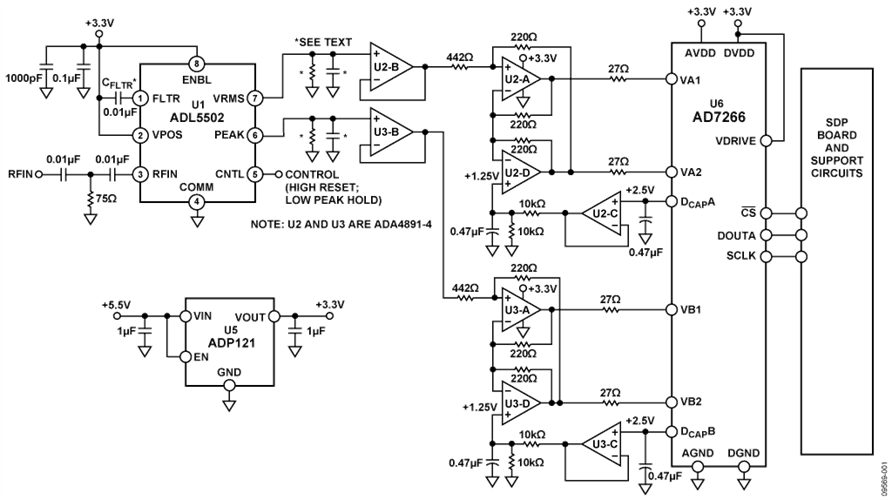

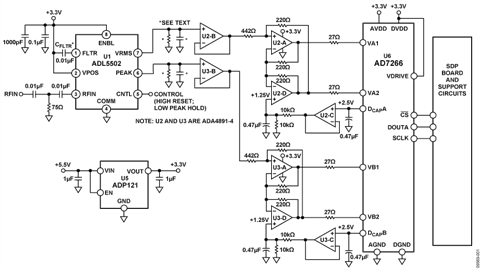

回路機能とその特長

図1に示す回路は450MHz ~ 6GHzの任意の周波数でのピークとrms電力を約45 dBの範囲で測定します。測定結果はノイズを避けるために差動信号に変換され、シリアル・インターフェースでリファレンス内蔵の12ビットSAR・ADCの出力からデジタル・コードとして出力します。簡単な2ポイント・キャリブレーションがデジタル領域で実行されます。

ADL5502は変調信号のクレスト・ファクタ(CF)を高精度に決定する、エンベロープ検出と組み合わせた真のRMS(true rms)電力検出器です。このデバイスは、10MHz以上のエンベロープ帯域幅で450MHz~6GHzの周波数範囲の高周波レシーバ/トランスミタ・シグナル・チェーンで利用できます。サンプリング・レートが低いADCでもピーク・ホールド機能があるので、エンベロープの短いピークでも取り込むことができます。合計消費電流はわずか3 mA@ 3 Vです。

ADA4891-4は高速、クワッド、CMOSオペアンプで、低価格にもかかわらず高性能になっています。消費電流は3Vでたった4.4 mA/アンプです。このアンプは、真の単電源動作能力を備えており、入力電圧範囲は負側レールの下側300 mVまで拡張されています。出力段もレールtoレールになっており、出力電圧は各レールから50mV以内まで振れ、最大のダイナミック・レンジが得られます。低歪みでセトリング時間が速いので、このアプリケーションに最適です。

AD7266は、単電源2.7 V~5.25 Vで動作する、デュアル、12ビット、高速、低消費電力の逐次比較型ADCで、最大2 MSPSのサンプリング・レートが特長です。AD7266は2個のADCを備えており、それぞれ前段に3チャンネルのマルチプレクサと、30MHz超の入力周波数を処理できる低ノイズ広帯域トラック&ホールド・アンプが接続されています。消費電流は3 Vでわずか3 mAです。AD7266はまた2.5 Vリファレンスを内蔵しています。

この回路は ADP121から出力する+3.3 V 単電源で動作します。ADP121は、2.3 V~5.5 Vで動作し、最大150 mAの出力電流で、低静止電流、低ドロップアウト(LDO)のリニア・レギュレータです。150 mA負荷でのドロップアウト電圧は135 mVと低いため効率が向上するとともに、広い入力電圧範囲にわたって動作可能になります。最大負荷時の静止電流が30μAと小さいADP121はバッテリ駆動のポータブル機器に最適です。

ADP121には、1.2 V~3.3 Vの範囲の各種出力電圧が用意されています。この製品は、小型1μFのセラミック出力コンデンサで、安定動作するように最適化されています。ADP121は、最小のボード面積で優れた過渡性能を提供します。

短絡回路防止とサーマル過負荷保護回路は、悪条件での破損を防止します。ADP121 は小型の5 ピンTSOT または4 ボール0.4mm ピッチのハロゲン・フリーWLCSP パッケージに収納されており、多様なポータブル・アプリケーションに適応できるようにフットプリントが最小になっています。

(簡略化した回路:全ての接続及びデカップリングは示されていません。)

回路説明

測定するRF信号をADL5502に入力します。RF入力端子でADL5502の入力インピーダンスと並列に1つの75 Ω の終端抵抗を 接続する事により広帯域の50 Ω マッチングが得られます。狭周波数帯域の使用により、より精度の高い抵抗性マッチングまたはリアクタンス・マッチングが得られます(ADL5502データシートの RF入力インターフェース・セクションを参照)

ADL5502に内蔵のフィルタ用コンデンサにより2乗した状態でのの平均値が得られますが、出力に多少の残留ACが残ります。W-CDMA または CDMA2000のようなピークto平均比の高い信号の場合はADL5502 のVRMS・DC出力にAC残留電圧が出る可能性があります。波形のこれら低周波成分の影響を減少させるためには、多少の追加のフィルタリングが必要です。ADL5502に内蔵の平方領域フィルタ・コンデンサは 1ピン (FLTR) と 2ピン (VPOS)の間にCFLTRコンデンサを接続する事により強化されます。VRMS出力にコンデンサを追加する事により残留ACをさらに減らす事ができます。内蔵の100 Ω出力抵抗と追加の出力コンデンサの組み合わせによりローパスフィルタを形成し、VRMS出力の出力リップルを削減します(詳しくはADL5502データシートのthe Selecting the Square-Domain Filter and Output Low-Pass Filterセクションを参照してください)。

波形のピークを測定するために、コントロール・ライン(CNTL)を1次的にロジック・ハイに設定する必要があります(>1 µSの間リセット・モード)そしてその後ロジック・ロー(ピーク・ホールド・モード)に戻します。この処理により、ADL5502は既知の状態に初期化されます。ピークを測定するためにデバイスを設定する時、入力rms電力とクレスト・ファクタ(CF)が変化しそうもない期間にピーク・ホールド・モードをトグロする必要があります。

もしADL5502 がピーク・ホールド・モードで、CFが“ハイ”から“ロー”に変化するかまたは入力電力が“ハイ”から“ロー”に変わると、異常なピーク測定値が表示されます。ADL5502はピーク・ホールド・モードが駆動していて、入力電力またはCFが高かった時生じた最高のピーク値を単純に出力し続けます。もしCNTLをリセットしなければ、PEAK出力は信号の新しいピークを反映しません。

ADL5502は約3 mAのVRMS出力電流を供給する能力があります。出力電流は内蔵の100 Ω 直列抵抗を通して供給されます;従って負荷抵抗はすべてこの内蔵抵抗と電圧デバイダを形成する事になります。ADL5502の VRMS出力の出力振幅を維持するために、高い抵抗性負荷を駆動する事をお勧めします。もしアプリケーション上で低抵抗負荷を駆動する必要がある場合は(公称変換ゲインを大きくしたい場合も同様に)バッファ回路が必要です。

PEAK出力は2 pF負荷を駆動するように設計されています。ADL5502 のPEAK出力が駆動する容量負荷を小さくして、出力応答時間を損なわないようにする事をお勧めします。容量負荷が大きい場合の影響は得に立下り遷移時のエンベロープに追従する時見られます。エンベロープが立下り遷移の時、負荷容量は内蔵の1.9 kΩ負荷抵抗を通して放電します。もしさらに大きな容量負荷が避けられない場合は、その追加のコンデンサに対応するためにPEAK出力とグランドの間にシャント抵抗を接続して速く放電させる事ができます。このようなシャント抵抗はまたADL5502の動作電流を大きくするのでその値は500Ω以下にする必要があります。

回路の代表的な実測性能特性を図2~5 に示します。

ターン・オン時間とパルス応答は平方領域フィルタ(CFLTR) とVRMS出力に接続した出力にシャントされるコンデンサの大きさに大きく影響されます。図6(ADL5502データシートから引用)は出力フィルタ容量0.1uFで、平方領域フィルタ容量(CFLTR)が無い場合のRFINピンに印加したRFパルスに対する出力応答の図です。立下りエッジは得に出力にシャントされるコンデンサの容量に影響されます。

出力にシャントされるコンデンサの容量と並列に抵抗を接続して、イネーブルとパルス応答の立下りエッジを改善する事ができます。追加抵抗は出力フィルタ容量の放電を助けます。この方法によりパワーオフ時間は短くなりますが、負荷抵抗を追加する事によりまた出力は低下します(ADL5502データシートのOutput Drive Capability and Bufferingセクションを参照してください)。図7(ADL5502データシートから引用)は並列1 kΩ抵抗を追加した事により得られた改善を示します。

ADL5502のrms出力 と PEAK出力はユニティ・ゲイン・バッファを通過します。そしてこのユニティ・ゲイン・バッファはシングル・エンド出力を差動信号に変換する相互結合回路を駆動します。AD7266 に内蔵の+2.5 Vリファレンス(DCAPAピン と DCAPBピンを介して)は他のユニティ・ゲイン・バッファと分圧器を通ります。 これにより回路の同相電圧が+1.25 Vに設定されます。

AD7266はrms出力とPEAK出力の同時サンプルを実行し、データを1 µs応答時間以内に転送します。このデータは、1つのシリアルデータ・ラインで送信されます。傾きとインターセプトはデバイスごとに変わるので、高精度を実現するには基板レベルのキャリブレーションを実施する必要があります。一般的に、キャリブレーションは、ADL5502に2つの入力電力レベルを供給し、対応する出力電圧を測定することにより実施されます。キャリブレーション・ポイントは一般的に、デバイスのリニア動作範囲以内で選ばれます。最大適合直線は次の式を使って変換ゲイン(または傾き)とインターセプトを計算する事により特性化されます。

ここで:

VINはRFINのrmsです。

VVRMSはVRMSでの出力電圧です。

一度ゲインとインターセプトが計算されれば、実測した出力 電圧に基づいて(未知の)入力電力を計算できる式を記述す る事ができます。

![]()

理想の(既知の)入力電力の場合には、実測データの法則適 合性誤差を次のように計算する事ができます。

図8と図9は25°C(ADL5502がキャリブレーションされる温度)でのVRMS誤差とPEAK誤差の図です。誤差がゼロではない事に注目してください。なぜならADL5502はその動作領域以内でさえ完璧には理想のリニア公式に従わないからです。しかし、キャリブレーション・ポイントでの誤差は定義によりゼロに等しくなります。

VRMS出力とPEAK出力の特性(傾きとインターセプト)が分かった時、CFの計算が完了します。任意の波形のクレスト・ファクタの測定、計算は3段階で行います。最初に、未知の信号を RF入力に供給し、対応するVRMSレベルを測定します。このレベルは図10に VVRMS-UNKNOWNとして示されています。VVRMS-UNKNOWN と式3 を使ってRF 入力(VIN)を計算します。

次に、VIN を使ってPEAKのCWリファレンス・レベル(VPEAK-CW)を計算します(すなわち、入力波形がCW信号の場合観察される出力電圧)

![]()

最後に、PEAKの実際の大きさ(VPEAK-UNKNOWN)を測定します。そこで、CFを次のように計算する事ができます。

![]()

ここでVPEAK-CW は VPEAK-UNKNOWNと比較するリファレンス・ポイントとして使用されます。もし両方のVPEAK値が等しければ、図11にCWで示すようにCFは0 dBになります。(ADL5502データシートから引用)。ダイナミック・レンジ全体に渡り、計算したCFは0 dBライン付近を保ちます。同様に、CFが3 dB、6 dB、 9 dB の複雑な波形についても、計算値は正確に各々のCFレベルの付近を保ちます。

この回路あるいは任意の高速回路の性能は適正なPCBレイアウトに大きく依存します。PCBレイアウトの中には電源バイパス、(必要に応じて)特性インピーダンス・ライン、部品配置、信号配線、電源とグラウンド・プレーンが含まれます(しかし限定はされません)。(PCB レイアウトに関するより詳しい情報については、チュートリアルMT-031 と、チュートリアルMT-101(英語), そしてAnalog Dialogue 高速プリント回路基板 レイアウトの実務ガイドをご参照ください) この回路ノートのための完全な設計支援パッケージは https://www.analog.com/CN0187-DesignSupportに載っています。

回路の評価とテスト

この回路は回路基板(EVAL-CN0187-SDPZ)とシステム・デモ用プラットホーム(SDP) 評価基板のEVAL-SDP-CB1Zを使用します。2つの基板には、回路の性能の迅速な設定と評価を可能にする120ピン適合コネクタが使用されています。回路基板(EVAL-CN0187-SDPZ)は(このノートに記述されているように)評価対象の回路を含みます。そして回路基板(EVAL-CN0187-SDPZ)からデータを取り込むために、SDP評価基板をCN0187 評価ソフトウエアと共に使用します。

必要な装置

- USBポートがありWindows® XPまたはWindows Vista®(32-bit)または Windows® 7 (32-bit)対応のPC

- 回路評価基板(EVAL-CN0187-SDPZ)

- 評価基板(EVAL-SDP-CB1Z SDP)

- 評価ソフトウエア(CN0187)

- 電源電圧:+6 V または+6 V ”ACアダプタ”

- RF信号源

- SMAコネクタ付き同軸RFケーブル

評価開始にあたって

CN0187評価ソフトウエア・ディスクをPCのCDドライブに入れて評価ソフトウエアをロードしてください。”マイ コンピュタ”を使用して、評価ソフトウエア・ディスクを含むドライブを見つけ、Readmeファイルを開いてください。Readmeファイルに含まれているインストラクションに従って、評価ソフトウエアをインストールし、使用してください。

機能ブロック図

回路ブロック図についてはこの回路ノートの図1を、そして回路図については“EVAL-CN0187-SDPZ-SCH”pdfファイルをご覧ください。このファイルは CN0187 DesignSupport Packageに含まれています。

セットアップ

回路基板(EVAL-CN0187-SDPZ)の120ピン・コネクタを評価(SDP)基板(EVAL-SDP-CB1Z)の“CON A” と表示されたコネクタに接続してください。120ピン・コネクタの末端にある穴を利用して2つの基板をしっかり固定するためにナイロン製ハードウエアを使用する必要があります。適切なRFケーブルを使用し、SMA RF入力コネクタを介してRF信号源を回路基板(EVAL-CN0187-SDPZ)に接続してください。電源を”supply off”の状態で、+6 V電源を基板の“+6 V” と “GND”と表示されているピンに接続してください。もし+6 V用"ACアダプタ"があれば、基板のバレル・ジャック・コネクタに接続して+6 V電源電圧の代わりに使用する事ができます。SDP基板と共に提供するUSBケーブルをPCのUSBポートに接続してください。注:この時にはまだUSBケーブルをSDP基板上のミニUSBコネクタに接続しないでください。

テスト

回路基板(EVAL-CN0187-SDPZ)に接続した+6 V電源(またはACアダプタ)に電源を供給してください。評価ソフトウエアを立ち上げ、PCからのUSBケーブルをSDP基板上のUSBミニ・コネクタに接続してください。アナログ・デバイセズのシステム開発プラットフォーム・ドライバがデバイス・マネージャにリストされていれば、ソフトウエアはSDP基板と通信する事ができます。

一度USB通信が確立されれば、SDP基板を使用して回路基板(EVAL-CN0187-SDPZ)からのシリアル・データの送信、受信、取り込みを行う事ができます。

回路ノートのデータはRohde & Schwarz のSMT-03 RF信号源とAgilent E3631A電源を使用して生成されました。信号源は図に示した周波数に設定しました。そして入力電力をステップ状に加え、1 dB単位でデータを記録しました。

データ取り込みのための評価ソフトウエアの使用方法に関する情報と詳細はCN0187評価ソフトウエアのReadmeファイルに載っています。

SDP基板に関する情報はSDP ユーザー・ガイド(英語)に載っています。