Overview

Design Resources

Design & Integration File

- Schematic

- Bill of Materials

- Gerber Files

- Assembly Drawing

- Allegro Layout File

- LTspice Simulation Circuit

Evaluation Hardware

Part Numbers with "Z" indicate RoHS Compliance. Boards checked are needed to evaluate this circuit.

- EVAL-ADICUP3029 ($60.92) Ultralow Power Cortex-M3 Arduino Form Factor Development Board

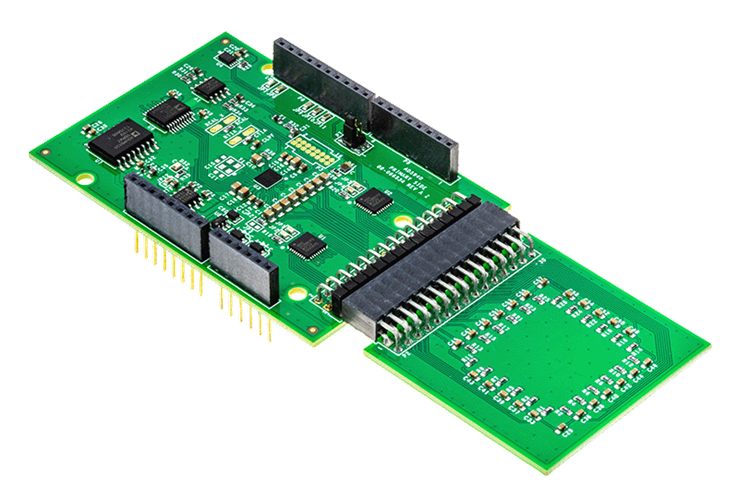

- EVAL-CN0565-ARDZ ($189.75) Electrical Impedance Tomography Measurement System

Device Drivers

Software such as C code and/or FPGA code, used to communicate with component's digital interface.

Features & Benefits

- Up to 24 Input Electrodes, Software Selectable

- 2-wire or 4-wire Electrode Configuration Supported

- Real and Imaginary Measurements up to 200 kHz

- Open Source Image Recreation Algorithms

- Isolated Power and Digital Domains from the Host

- Arduino Form Factor Compatible

Documentation & Resources

-

CN0565 User Guide9/28/2023WIKI

-

CN0565: Electrical Impedance Tomography Measurement System (Rev. A)9/28/2023PDF758 K

Circuit Function & Benefits

Electrical impedance tomography (EIT) is a type of imaging in which an image is constructed from multiple impedance measurements taken between various points across the surface of a specimen. Compared with other imaging techniques such as X-ray, ultrasound, or computerized axial tomography (CAT) scan, EIT is considerably lower cost, lower power, radiation-free, and easily adapted to portable, wearable, and continuous monitoring applications. While EIT is typically lower resolution than X-ray, ultrasound, or CAT scan, it finds broad application in medical imaging, often augmenting other methods. EIT can be as effective as other imaging methods in certain pulmonary function measurements.

EIT images are constructed by placing an array of electrodes across the surface of a sample. A pair of electrodes is then excited with a current, and the resulting voltage is measured between a second pair of electrodes. A series of measurements is taken across the sample, with the exact sequence dependent on the imaging technique. From these measurements, a calculation determines the internal impedance profile, from which a two- or three-dimensional (2D or 3D) image is produced.

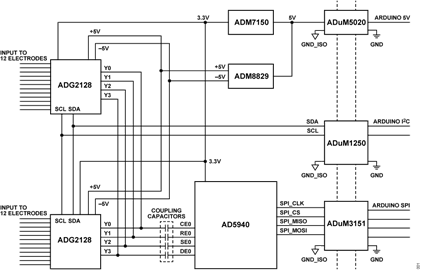

The circuit shown in Figure 1 is a 24-electrode EIT measurement system for measuring the impedance profiles of various materials. The electrode configuration is arbitrary; excitation can be applied to any two electrodes, and measurements taken across any two electrodes. Excitation frequency is adjustable between 0.015 Hz and 200 kHz, allowing the measurement of frequency-dependent effects.

The design features complete power and signal isolation from the host controller, essential for medical, bioimpedance analysis (BIA), and certain industrial applications. The module uses an Arduino compatible form factor, and the software example is based on the industry-standard industrial input/output (IIO) framework for easy integration into end-user systems.

Circuit Description

ELECTRICAL IMPEDANCE TOMOGRAPHY

In its simplest form, EIT is implemented by placing an array of electrodes across the surface of a sample and exciting pairs of electrodes with a current signal while measuring the voltages induced on other electrodes. From these measurements, a calculation determines the sample's internal impedance profile and uses this input to create a 2D or 3D image.

Figure 2 shows a typical EIT system. An array of 8 electrodes is placed around the test object, and an AC current at a certain frequency is injected into a pair of forcing electrodes (F+ and F-). The resultant voltage between a pair of sense electrodes (S+ and S-) is measured and stored. The sequence continues to the next pair of electrodes until all required inputs to the impedance calculation are collected. The impedance readings are then mapped to an EIT image showing the sample's internal impedance profile.

IMPEDANCE MEASUREMENT

Multiple, independent impedance measurements must be taken in order to create a tomographic image. The electrical techniques for measuring DC resistance and AC impedance are well established; conceptually, a circuit element is excited with a current, and the resulting voltage is measured.

In general, impedance measurements can be performed with either two electrodes or four electrodes, shown in Figure 3.

Bioimpedance measurements have additional considerations; medical devices must conform to the IEC 60601 standard, which limits the amount of DC and AC voltage that can be applied to the human body. Furthermore, electrodes have their own impedance that can vary considerably from unit to unit, contact to a sample, and over time.

2-Wire Impedance Measurement

The simplest form of impedance measurement uses two connections to the unknown sample, shown in Figure 4.

A voltage excitation signal is applied across the unknown impedance (ZUNKNOWN) in series with a current limiting resistor (RLIMIT). The voltage across the electrodes (VZUNKNOWN) is measured, which does not include the drop across the limiting resistor. At the same time, current flow through the unknown impedance (IZUNKNOWN) is converted to a voltage by a transimpedance amplifier (TIA).

In practice, the 2-wire method is not practical for impedance measurements in medical applications. While the impedances in these applications are typically high enough that the lead resistance is insignificant, the electrode impedance appears in series with the measured impedance. Also in tomography applications, multiple sense measurements at other locations on the sample may be required for a given pair of force electrodes.

4-Wire Impedance Measurement

Figure 5 shows how the 4-wire impedance measurement technique overcomes the electrode impedance problem by using separate force and sensing electrodes. Any voltage drop across the force electrodes drops out of the calculation, similar to the drop across RLIMIT. The IN+ and IN- sense inputs are high-impedance, so drop across the sense electrodes and their corresponding RLEAD is negligible.

ANALOG FRONT END

The core of the CN0565 is the AD5940 high precision, impedance, and electrochemical front end. Table 1 shows the two operation modes of AD5940's digital-to-analog converter (DAC).

| Low Bandwidth Operation | High Bandwidth Operation | |

| DAC | low power, dual-output DAC | high-speed DAC |

| Operation | generates the bias voltage for the low power transimpedance amplifier and the bias voltage for the potentiostat amplifier | generates a high frequency, AC excitation signal for highspeed transimpedance amplifier designed to convert high bandwidth current signals |

| Excitation Frequency Range | < 200 Hz | > 200 Hz |

| Application Examples | electrodermal activity measurements | body impedance measurements, battery impedance measurements |

The AD5940 includes a flexible switch matrix that can select the electrodes, high speed DAC excitation amplifier, and the high speed TIA inverting input, as well as an external calibration resistor.

Figure 6 shows the AD5940 configured for a 4-wire impedance measurements, including 0.47 μF DC-blocking capacitors.

Excitation Signal

The CN0565 includes a high speed DAC and waveform generator to provide a precision AC voltage source. A digital waveform generator produces a sine wave, square wave, or trapezoid pattern which is routed to the 12-bit, high speed DAC and excitation amplifier, which then drives the electrodes. The impedance under test is connected between the counter electrode pin (CE0) and reference electrode input pin (RE0). An internal differential sense configuration inside the AD5940 guarantees the accuracy of the voltage source by connecting CE0 and RE0 back into the excitation buffer. The excitation signal amplitude and frequency are programmable up to ±607 mV and 200 kHz, respectively.

Current Limit

The CN0565 includes a current limit resistor, which limits the amount of AC current that enters the sample. To conform to IEC 60601 standards for medical applications, the maximum allowable AC current is 500 μA at 50 kHz and 600 μA at 60 kHz. When calculating the RLIMIT resistor value, the maximum output voltage from the AD5940 is 1.2 Vp-p (0.4243 VRMS). Set the maximum allowable AC current to 80% of maximum, or 400 μARMS. Calculate the current limit using Equation 1:

As such, a 1 kΩ RLIMIT is selected and is connected to the CE0 pin on the AD5940. The 0.47 μF CISOx has an impedance of 6.8 Ω at 50 kHz and is ignored in this calculation.

Isolation Capacitors

The IEC 60601 standards set 10 μA as the maximum DC current allowed to enter the human body. The DC current of the CN0565 is guaranteed to be zero due to the addition of isolation capacitors. A value of 0.47 μF is selected for the isolation capacitors because 0.47 μF is a sufficiently large capacitance that is also available in small packages suitable for wearable electronics. See the EDA section of AN-1557 application note for details on capacitor size calculations.

While the AD5940 excitation frequency can be programmed as low as 0.015 Hz, at low frequencies the impedance of the isolation capacitor is high enough to attenuate the excitation current. This reduces the signal-to-noise ratio (SNR) of the impedance measurement, resulting in noisy readings. Figure 7 shows the impedance of two 0.47 μF in series vs. excitation frequency and can be used to estimate the lowest practical frequency that can be used for a given sample impedance. For example, using a guideline that the drop across the isolation capacitor should be less than or equal to the drop across the sample, an excitation frequency of 150 Hz will be suitable for impedances as low as 4515 Ω.

High Speed TIA Gain Resistor and ADC Input Range

To achieve an accurate, low-noise impedance measurement, the voltage and current measurements should exercise a large fraction of the analog-to-digital converters (ADC) input range. The sense lead voltages are measured directly, and the ADC input range of 900 mV peak accommodates the 600 mV peak DAC output voltage. Note that an infinite impedance (open circuit) would result in the full DAC voltage at the ADC input. The current measurement is scaled by the transimpedance amplifier's RTIA, which can be set to one of ten values between 50 Ω and 160.1 kΩ.

With the excitation set to maximum (600 mV), the value of the minimum impedance can be calculated using Equation 2:

where:

ZMIN is the minimum impedance in the force path.

RTIA is the gain resistor value of the transimpedance amplifier.

Note that the impedance includes the lead resistance, isolation capacitors, and RLIMIT, as all of these reduce the magnitude of the excitation current.

The LTspice simulation shown in Figure 8 is a conceptual model of the AD5940, isolation capacitors, switch resistance, and can be used to estimate an optimal excitation amplitude and RTIA value for any application. Figure 9 shows the TIA output voltage for a given resistor value and excitation frequency.

Crosspoint Switch

The CN0565 includes two ADG2128 8x12 analog crosspoint switches, which allow force and sense electrodes to be assigned arbitrarily. The switch resistances are less than 35 Ω, and has a typical capacitance of 18.5 pF. The switches are powered from a ±5 V bipolar supply, allowing a ±5 V common-mode range of the electrodes with respect to isolated circuit ground.

As shown in Figure 10, the four Y input/output of the two ADG2128 switches are routed to the four analog pins of the AD5940. The first 12 electrode connections (E0 to E11) are connected to the input/output nodes of the first ADG2128, and the second set of 12 electrodes are connected to input/output nodes of the second ADG2128.

INPUT MEASUREMENT

The AD5940 uses a high speed, high precision TIA to convert the current from the electrode into a voltage measured by the ADC at a speed of 800 kSPS. The TIA is internally biased to 1.1 V, centering the output in the ADC's full scale range.

A discrete Fourier transform (DFT) is performed on the ADC data for the current and voltage values, and is configurable up to 16,384 points. The magnitude and phase of the voltage and current are then calculated from the real and imaginary outputs of the DFT in Equation 3 and Equation 4, respectively. The AD5940 then calculates the real and imaginary parts and the unknown impedance is derived using Equation 5:

where:

ZUNKNOWN is the unknown impedance of the specimen under test.

VMAG is the magnitude of the voltage across the ZUNKNOWN.

IMAG is the magnitude of the current through the ZUNKNOWN.

rv and iv are the real and imaginary components from the voltage DFT measurements.

ri and ii are the real and imaginary components from the current DFT measurements.

RTIA is the value of the high speed TIA gain resistor in Ω.

POWER ARCHITECTURE

Figure 11 shows the complete power tree of the CN0565. The host platform board provides 5 V to the ADuM5020 isolated DC-to-DC converter, producing an isolated 5 V, 500 mW output voltage. The isolated 5 V output is used as input to the whole section of the circuit responsible for the actual impedance measurement and processing.

The isolated 5 V is fed into the ADM7150 low dropout linear regulator, producing a regulated 3.3 V with 120 mA output. The 3.3 V is used to power the AD5940 as well as provide the digital power supply to the ADG2128 crosspoint switches.

The isolated 5 V rail is also used as input to the AD8829 voltage inverter, which produces a dual supply, ± 5 V for the two ADG2128 analog crosspoint switches.

ISOLATION

The entire measurement circuit is galvanically isolated via the ADuM5020 DC-to-DC converter, ADuM1250 I2C isolator, and ADuM3151 7-channel digital isolator for serial peripheral interface (SPI) with aux channels. No explicit stitching capacitance is included, for a total isolated capacitance of 18 pF between grounds.

The minimum creepage on the CN0565 is 20 mils due to layout constraints, providing a basic isolation of 150 V. When designing a board to meet a specific regulatory standard, refer to the standard for creepage requirements, and refer to the Safety and Regulation for Digital Isolation for agency certifications.

SYSTEM PERFORMANCE

The fidelity of a tomography image is dependent on several factors including the accuracy of electrode placement, the imaging mode, and fundamentally, the accuracy of the impedance measurements themselves. The 20% typical RTIA tolerance directly affects the measurement and must be calibrated. An external calibration resistor between RCAL0 and RCAL1 pins provides an accurate reference. During calibration, a software routine sets the multiplexer to connect RCAL between the excitation buffer and TIA input, and an excitation signal is applied. Calibration values are measured, calculated, and stored, removing the RTIA error from subsequent impedance measurements.

Figure 12 and Figure 13 show the post-calibration measurement error for various resistances and capacitances at a typical excitation frequency of 20 kHz.

IMAGE RECONSTRUCTION ALGORITHMS

From the collected data, the image of the electric impedance distribution may be constructed by use of certain reconstruction algorithms. In EIT, the conductivity distribution of the unknown object is estimated from boundary voltages induced by different current patterns with the aid of various image reconstruction algorithms. The CN0565 example software can perform three image reconstruction algorithms: back-projection (BP), Jacobian calculations (JAC), and Graz consensus reconstruction EIT (GREIT).

With back-projection, reconstructed images can be simply understood as a superposition of boundary measurements. JAC algorithm preserves sharp edges, while GREIT uses training data to generate images with more uniform amplitude response.

Figure 14 shows a sample EIT image using different reconstruction techniques.

Sensing Area

The CN0565 supports up to 24 electrodes and various impedance measurement methods are supported. Figure 15 shows the neighboring method, whereby the current is applied through neighboring electrodes and the voltage is measured successively from all other adjacent electrode pairs. Lines of equipotential are shown, and the measured impedance is a weighted average of the red shaded area.

Common Variations

Circuit Evaluation & Test

This section describes the setup and procedure for evaluating the EVAL-CN0565-ARDZ. For complete information on the circuit evaluation setup, refer to the CN0565 User Guide.

EQUIPMENT NEEDED

- EVAL-CN0565-ARDZ circuit evaluation board

- EVAL-ADICUP3029 development platform

- Host PC (Windows)

- Micro-USB cable

SETUP AND TEST

- Connect the EVAL-CN0565-ARDZ to the EVAL-ADICUP3029 via the Arduino headers.

- Connect the impedance test board to the main EVAL-CN0565-ARDZ board via the 30-pin, 100-mil headers.

- Power the boards by connecting the micro-USB cable into P10 on the EVAL-ADICUP3029 and then plug the other end of the cable to the host PC, as shown in Figure 16.

- The DS2 in the EVAL-CN0565-ARDZ must turn green to indicate power.

- Install Python and the pyadi-iio library which includes CN0565 hardware support and example scripts.

- Ensure the version of Python is supported in pyadi-iio.

- Load the CN0565 firmware to the EVAL-ADICUP3029 by copying the pre-built .hex file directly into the DAPLink drive.

- Ensure that the DAPLink is visible in the file explorer to indicate a proper connection between boards.

- Drag and drop the CN0565.hex file to the DAPLink. The DAPLink will automatically disconnect and connect again, indicating a successful upload.

- Open a command terminal and navigate to the working directory where the example script is saved by entering:

cd <folder address>

Execute the script by typing the following command into the terminal window.

python cn0565_prod_tst.py

The script will measure the impedance test board values and the output should look similar to Figure 17.

For detailed instructions on how to run the impedance measurement for a single pair, electrode tomography and for the graphical user interface (GUI) demo by using a phantom or a petri dish, see the CN0565 User Guide.