デジタル無線レシーバー設計の基礎(無線入門)

概要:本稿で、デジタル無線レシーバーを設計する基礎的な方法を紹介します。データ・コンバータや無線技術に関する数多くの進歩によって、複雑なレシーバーの設計が大幅に単純化できるようになりました。ここで、このようなレシーバーの感度と選択度を計算する方法を説明します。これすべての側面を網羅的に説明するのでなく、このような設計に必要とされる数多くの手法や計算の基本を解説するものです。

無線機の設計とアーキテクチャに関する数多くの進歩により、無線機設計の分野は今や急速に変化しつつあります。これらの変化によって、信頼性と精度の低いアナログ部品をデジタル部品に切り替えることで、サイズ、コスト、複雑さの削減が可能となり、製造上の進歩がもたらされています。これらの実現には半導体の設計や製造における数多くの進歩が必要でしたが、それらは過去数年間で達成されました。進歩したデバイスの例には、より集積度の高いミキサー、LNA、高性能のSAWフィルタ、低コストの高性能ADC、プログラマブルなデジタル・チューナおよびフィルタなどがあります。この記事では、無線システムの全体設計に関わる課題の概要と、これらのデバイスと無線システム全体のインターフェースを取る方法を示します。

無線機とは何か

従来、無線機とはアンテナとその背後にあるものすべてを接続する「箱」であると考えられてきましたが、多くのシステム設計は2つの分離したサブシステムに分割されます。すなわち、無線機とデジタル・プロセッサです。この分割における無線機の役割は、目的の信号をダウンコンバートしてフィルタリングを行い、情報をデジタル化することです。また、デジタル・プロセッサの役割は、デジタル化されたデータを取り込んで、必要な情報を取り出すことです。

理解しておくべき重要な点は、デジタル・レシーバーとデジタル無線機(変調)は同じものではないということです。実際のところ、デジタル・レシーバーは、AMやFMなどすべてのアナログ信号の受信において非常に大きな役割を果たします。デジタル・レシーバーは、任意のアナログまたはデジタル変調標準を含むあらゆるタイプの変調の受信に使用できます。更に、デジタル・プロセッサのコアはデジタル・シグナル・プロセッサ(DSP)なので、ソフトウェアを通じて無線レシーバー自体の多くの要素を制御することができます。したがって、これらのDSPはすべて同じハードウェアを使い、ユーザの分割方法に基づいて、アップグレードや新しい機能を使ってプログラムし直すことができます。しかしこれは、それ自体で丸々1つの検討事項となるもので、この記事の対象ではありません。

この記事の対象は無線機であり、その性能をどのように予測し、設計するかということです。ここでは以下の事項について検討します。

- 有効ノイズ電力

- カスケード・ノイズ指数

- ノイズ指数とADC

- 変換ゲインと感度

- ADCのスプリアス信号とディザ

- 3次インターセプト・ポイント(IP3)

- ADCクロック・ジッタ

- 位相ノイズ

- RFセクションのIP3

シングルキャリアとマルチキャリア

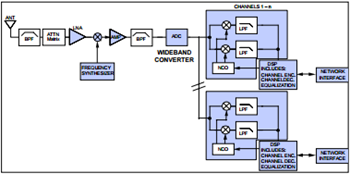

検討対象となる無線機には、2つの基本的なタイプがあります。1つはシングルキャリアと呼ばれるもので、もう1つはマルチキャリアと呼ばれるものです。その名前が示唆するところは明らかですが、その機能はさほど明確ではありません。シングルキャリア・レシーバーは伝統的な無線レシーバーで、IF段にあるアナログ・フィルタで選択度が決まります。マルチキャリア・レシーバーは帯域内のすべての信号を1つのRF/IFアナログ・ストリップで処理し、A/Dコンバータに続くデジタル・フィルタ内で選択度が決まります。この種のレシーバーの利点は、複数のレシーバーを同じ周波数帯の異なる周波数に合わせて調整するアプリケーションの場合に冗長回路を省略できるので、システムを小型化してコストを削減できることです。代表的なアプリケーションとしては、セルラ基地局やワイヤレス・ローカル・ループ基地局があります。もう1つのアプリケーションが監視用レシーバーで、通常はスキャナを使用して複数の周波数をモニタします。このアプリケーションでは、シーケンシャル・スキャンを行わずに多くの周波数を同時にモニタリングすることが可能です。

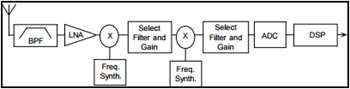

代表的なシングルキャリア・レシーバー

代表的なマルチキャリア・レシーバー

デジタル無線レシーバー実装の利点

デジタル無線レシーバーの設計について詳しく検討する前に、まず、いくつかの技術的利点について検討しておく必要があります。これらの利点には、オーバーサンプリング、プロセス・ゲイン、アンダーサンプリング、周波数プランニング/スプリアス配置などがあり、その多くは、従来の無線レシーバー設計では実現できなかった技術的利点を提供します。

オーバーサンプリングとプロセス・ゲイン

ナイキスト基準は、所定の信号に必要なサンプル・レートをコンパクトな構成で決定します。多くの場合、最も高い周波数成分の2倍のサンプル・レートをナイキスト・レートと呼びます。このことから、70MHzのIFサンプリング・アプリケーションでは140MSPSのサンプル・レートが必要なことが暗示されます。使用する信号が70MHzを中心として5MHzしか占有していない場合、140MSPSでのサンプリングは無駄と言えます。これに対し、ナイキスト基準の場合に必要なのは、信号の帯域幅の2倍でサンプリングすることです。したがって、使用する信号の帯域幅が5MHzの場合は、10MHzでのサンプリングが妥当です。これ以上はオーバーサンプリングと呼ばれます。オーバーサンプリングにより、受信したS/N比の実質的な増加がデジタル領域で可能になるので、非常に重要な機能です。

オーバーサンプリングと対照をなすのが、アンダーサンプリングです。アンダーサンプリングは、実際の信号周波数の半分よりもはるかに低い周波数でサンプリングすることを言います(アンダーサンプリングについては後述)。したがって、オーバーサンプリングとアンダーサンプリングは同時に行うことが可能です。前者は帯域幅に関して定義され、後者は対象となる周波数で定義されるからです。

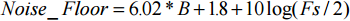

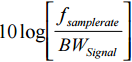

デジタル化のプロセスでは、信号のサンプリング・レートが速いほどノイズ・フロアは低くなります。ノイズが、より広い周波数範囲に広がるからです。合計積分ノイズは一定ですが、より広い周波数帯に広がるため、ADCの後段にデジタル・フィルタがある場合は利点となります。ノイズ・フロアは次式で表されます。

この式はコンバータ内の量子化ノイズのレベルを表し、ノイズとサンプル・レートFs間の関係を示します。したがって、サンプル・レートを2倍にするごとに、実効ノイズ・フロアは3dBずつ改善されます。

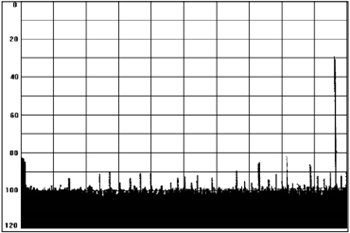

デジタル・フィルタリングは、下の図に示すように不要なノイズとスプリアス信号をすべて除去して、必要な信号だけを残す効果があります。

デジタル・フィルタリング後の代表的ADCスペクトル

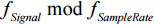

上の図に示すように、ADCのS/N比は大幅に改善されます。実際、S/N比は次式を使うことによって改善できます。

これからわかるように、サンプル・レートと信号帯域幅の比が大きいほどプロセス・ゲインは大きくなり、実際に30dBのゲインを達成できます。

アンダーサンプリングと周波数変換

前述のとおり、アンダーサンプリングとは、実際の信号周波数の半分よりもはるかに低い周波数でサンプリングすることを言います。例えば、13MSPSでサンプリングされる70MHzの信号は、アンダーサンプリングの一例です。

アンダーサンプリングはミキシングとよく似た機能を提供するので、極めて重要です。信号をアンダーサンプリングすると、その周波数がベースバンドまたは第1ナイキスト・ゾーンにエイリアスされ、あたかも最初からベースバンド内にあったかのように見えます。例えば、上の例に示した70MHzの信号を13MSPSでサンプリングすると、5MHzの位置にエイリアスが現れます。これは次式により数学的に記述できます。

この式は、第1および第2ナイキスト・ゾーンに現れる周波数を提示します。ADCはすべての情報を第1ナイキスト・ゾーンにエイリアスするので、この式から得られる結果については、fSampleRate/2よりも上かどうかをチェックする必要があります。条件にあてはまる場合は、fSampleRateから結果を引くことによって、その周波数を第1ナイキスト・ゾーンに折り返す必要があります。

信号がどのようにベースバンドにエイリアスされるのかということと、そのスペクトルの方向を下の表に示します。サンプリング(エイリアシング)のプロセスはミキシング(乗算)とは異なりますが、結果は非常によく似ています。ただし、サンプル・レートに関しては周期的です。もう1つの現象はスペクトル反転です。ミキサーの場合と同様、上側および下側サイドバンドの反転のように、一部の結果はサンプリング・プロセスで反転します。下の表は、どのケースでスペクトル反転が生じるかも示しています。

| 入力信号 | 周波数範囲 | 周波数シフト | スペクトル検出 |

|

第1ナイキストゾーン

|

DC - FS/2 | 入力 | ノーマル |

|

第2ナイキストゾーン

|

FS/2 - FS | FS - 入力 | 反転 |

|

第3ナイキストゾーン

|

FS - 3FS/2 | 入力 - FS | ノーマル |

|

第4ナイキストゾーン

|

3FS/2 - 2FS | 2FS - 入力 | 反転 |

|

第5ナイキストゾーン

|

2FS - 5FS/2 | 入力 - 2FS | ノーマル |

周波数プランニングとスプリアス配置

無線アーキテクチャを設計する際の最も大きい課題の1つが、IF周波数の配置です。また、この問題を複雑にしているのが、駆動アンプやADCが不要な高調波を発生させ、それがデータ変換時のデジタル・スペクトルに偽信号として現れる傾向があることです。アプリケーションが広帯域か否かに関わらず、サンプル・レートとIF周波数を慎重に選べば、必要信号だけを選択してすべての不要信号を除去できるAD6620のようなデジタル・チューナ/フィルタを使用することによって、これらのスプリアスを無害な位置に置くことができます。入力周波数範囲とサンプル・レートを慎重に選ぶことで、駆動アンプとADCの高調波を帯域外に置くことができるので、これは非常に有効な方法です。オーバーサンプリングは、広範囲の高調波スペクトルを無害な帯域に置いて、問題を単純化するだけです。

例えば、第2高調波と第3高調波が特に高いことが確認された場合は、サンプル・レートに関するアナログ信号をどの範囲にするかを慎重に選ぶことで、これらの第2および第3高調波を帯域外に置くことができます。エンコード・レートが40.96MSPSで信号帯域幅が5.12MHzの場合は、IFを5.12MHz~10.24MHzの範囲にすれば、下の表に示すように第2および第3高調波を帯域外に置くことができます。この例は極めて単純なものですが、様々なアプリケーションに合わせて応用することができます。

これからわかるように、第2および第3高調波は対象周波数帯から離れており、基本波成分に干渉することはありません。第2および第3高調波が互いにオーバーラップしていること、および第3高調波がFS/2付近にエイリアスとして現れていることに注意してください。これを表にすると、以下のようになります。

| エンコード・レート: | 40.96 MSPS |

| 基本波: | 5.12~10.24MHz |

| 第2高調波: | 10.24~20.48 MHz |

| 第3高調波: | 15.36~10.24MHz |

周波数プランニングのもう1つの例を、アンダーサンプリングの場合について示します。アナログ入力信号の範囲をDC~FS/2とした場合は、アンプとフィルタの組み合わせで必要な仕様の性能を発揮しなければなりません。しかし、信号が第3ナイキスト・ゾーン(FS~3FS/2)内に置かれている場合、すべての高調波がパスバンド・フィルタの範囲外になるので、システム仕様が求める高調波性能をアンプが満たす必要はなくなります。例えば、パスバンド・フィルタの範囲がFS~3FS/2だとします。第2高調波の範囲は2FS~3FSで、これはパスバンド・フィルタの範囲から大きく外れています。したがって、ADCが対象周波数における基本的仕様を満たしていれば、課題はフィルタの設計に移ります。このように比較的高いIF周波数でも、SAWやLCRなどの技術を使用すれば多くの複雑なフィルタを容易に実現できるので、多くのアプリケーションでは、この選択は有効なトレードオフです。この手法で駆動アンプの高調波性能要求は緩和されますが、相互変調性能を犠牲にすることはできません。

この手法を利用して、高調波が対象ナイキスト・ゾーンの外になるようにすれば、上に示すように高調波を簡単に除去することができます。しかし、依然としてADC自身が高調波を発生させる場合は、前述の手法により、帯域幅の未使用部分に高調波がくるようにサンプル・レートとアナログ周波数を慎重に選んで、これをデジタル的に除去することができます。

レシーバー性能の予測

以上のことを念頭に、無線機の性能をどのように決定すればよいのか、どのようなトレードオフが起こり得るのかを考えます。以下に示すように、伝統的な無線設計の多くの手法が使用できます。これから行う検討において、マルチチャンネル無線とシングルチャンネル無線にはいくつか違いがあるので、まずこれらについて述べます。ただし、ここでの検討はすべての側面を網羅しているわけではなく、触れていない部分も多いことに留意してください。また、この件に関する詳細は、記事末尾の参考文献欄に示す資料を参照してください。更にこの記事で検討するのは、DSPに送られるデータだけです。多くのレシーバーでは固有の方法を使用し、ノイズ除去やヘテロダイン除去を追加して更に性能の向上が図られています。

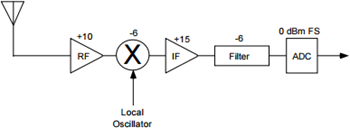

以下の検討では、上に示す一般的なレシーバー設計を使用します。ここではアンテナから検討を開始して、最終段にあるデジタル・チューナ/フィルタを最後に検討します。その先はデジタル・プロセッサで、これはこの記事の対象範囲外です。

分析はいくつかの仮定に基づいて行います。まず、レシーバーはノイズ制限されているものとします。つまり、帯域内に性能を制限するスプリアスは存在しないことになります。また、LOとIFは、これを実現できるように選択できるものとします。この仮定は妥当な範囲です。さらに、ADC内で発生するスプリアスは、多くの場合、ディザを適用するか、オーバーサンプリングと信号配置を適切に行うことによって除去できるので、通常は問題になりません。これについては後述します。場合によってはこのような仮定が現実的でないこともありますが、性能限界のベンチマークとして使用し得る適切な開始点とすることができます。

第2の仮定は、レシーバーのフロント・エンドの帯域幅をナイキスト帯域幅とすることです。ここで実際に割り当てられた帯域幅は5MHzだけですが、ナイキスト帯域幅を使用することで途中の計算を単純化できます。したがって、サンプル・レートが65MSPSの場合のナイキスト帯域幅は32.5MHzになります。

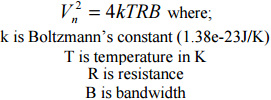

有効ノイズ電力

分析を開始するには、アンテナ・ポートにおけるノイズを考える必要があります。正しくマッチングされたアンテナは、表面上は抵抗のような挙動を示すので、マッチングが取られた入力端子のノイズ電圧は、以下の式で求めることができます。

したがって、ソース(この場合はアンテナ)からの有効電力は次のようになります。

これに先の式を代入すると、次のように単純化されます。

したがって実際には、この場合のソースからの有効電力は、抵抗値がゼロ以外の有限値の場合、インピーダンスと無関係になります。

これは、この例におけるレシーバーとの比較の基準点になるので、重要な点です。ある段のノイズ指数に言及する際、「kTノイズよりx dB高い」という言い方をよくしますが、これがその表現のゆえんです。

以下に述べるように、このノイズは、レシーバー内の段を進むにつれ、その段のノイズ指数分だけ悪化します。最終的には、そのチャンネルのチューニングとフィルタリングが行われる際にノイズの多くが除去され、対象チャンネル内にもともと存在するノイズだけが残ります。

カスケード・ノイズ指数

ノイズ指数は、無線機の受信チェーンの信号にどれだけのノイズが加わるかを記述するのに使われる性能指数です。通常、この値はdBで指定されますが、ノイズ指数の計算時は数値の比(対数ではない)が使われます。この非対数値はノイズ係数と呼ばれ、通常はFで表されます。この値は次のように定義されます。

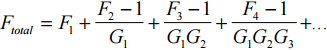

無線機内の各段にノイズ指数が割り当てられれば、これらを使って、それらの段のカスケード性能を求めることができます。入力ポートを基準とする合計ノイズ係数は、次式で計算できます。

上の式に含まれるFは各直列段のノイズ係数で、Gはその段のゲインです。この時点でのノイズ係数やゲインは、いずれも対数ではありません。この式を適用した場合、アンテナ・ポートまでのすべての部品のノイズが反映されます。したがって、前のセクションで導いた有効ノイズは、このノイズ指数によって直接悪化することがあります。

例えば、有効ノイズが−100dBm、計算したノイズ指数が10dB、変換ゲインが20dBの場合、出力における合計等価ノイズは−70dBmになります。

これらの式を適用するときは、考慮すべき点がいくつかあります。まず、受動部品については、ノイズ指数がその損失に等しいものとします。次に、直列の受動部品は、式を適用する前に合計することができます。例えば、挿入損失がそれぞれ3dBのローパス・フィルタが2個直列に接続されている場合は、これらをまとめて損失6dBの1個の素子と見なすことができます。最後に、多くのミキサーには、メーカーが指定したノイズ指数がありません。仕様が定められていない場合は挿入損失を使用できますが、デバイスにノイズ指数が指定されている場合は、それを使用します。

ノイズ指数とADC

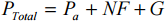

ADCにはノイズ指数を割り当てることができますが、多くの場合は別の方法を使用するほうが簡単です。ADCは電圧デバイスですが、ノイズ指数は実際にはノイズ電力に関わるものです。したがって、多くの場合は、ADCへのアナログ・セクションでノイズ指数に関する計算を行ってから、それをADCでの電圧に変換するほうが簡単です。ADCのノイズは入力基準電圧に変換します。次いで、アナログ・セクションとADCのノイズをADC入力位置で合計し、合計有効ノイズを求めます。

このアプリケーションでは、12ビットADCであるAD9042やAD6640のようなADCを選択しました。これらの製品は、最大65MSPSでサンプリング可能です。このレートは全帯域のAMPSデジタル化に適しており、GSM 5xリファレンス・クロック・レートに対応可能です。これは、AMPS、GSM、CDMAアプリケーション用としては十二分な性能です。データシートでは、S/N比の代表値は68dBとなっています。したがって、次のステップは、ADCノイズによるレシーバー内でのノイズ劣化を求めることです。この場合も、最も簡単なのはS/N比とレシーバーのノイズをrms電圧に変換し、その後に加算して合計rmsノイズを求める方法です。ADCの入力範囲がピークtoピークで2Vの場合、次のようになります。

この電圧は、ADC、熱、量子化によるすべてのノイズを表しています。ADCのフルスケール・レンジは707Vrmsです。

ADC等価入力ノイズを計算したら、次はレシーバー自体で発生するノイズを計算します。レシーバーの帯域幅をナイキスト帯域幅と仮定したので、サンプル・レートが65MSPSの場合の帯域幅は32.5MHzです。有効ノイズ電力の式から、アナログ・フロント・エンドのノイズ電力は134.55E–15ワット(−98.7dBm)です。これはアンテナにおけるノイズであり、変換ゲインによって増幅され、ノイズ指数によって悪化します。変換ゲインが25dBでノイズ指数が5dBの場合、ADC入力回路に加わるノイズは次のようになります。

これが50Ωに加わります(134.9e–12ワット)。ADCの入力インピーダンスは約1000Ωなので、標準の50Ω IFインピーダンスをこれに整合させるか、ADCインピーダンスを減らす必要があります。合理的な妥協案は、並列抵抗を使って200Ω程度の範囲まで減らしてから、1:4のトランスを使って残りを整合させることです。このトランスは、不平衡入力をADCに必要な平衡信号に変換する他、ある程度の電圧ゲインを提供する役割も果たします。インピーダンスが1:4の比率で上昇するので、このプロセスでは電圧ゲインも2になります。

この式から、50Ωの場合の電圧の2乗値は6.745e–9、200Ωの場合は26.98e–9となります。

これでADCおよびRFフロント・エンドのノイズがわかったので、2乗値の合計の平方根を求めることによって、システム内の合計ノイズを計算でき、合計電圧は325.9μVとなります。これがレシーバーのノイズとADCノイズによるADC内の合計ノイズで、これには量子化ノイズが含まれています。

変換ゲインと感度

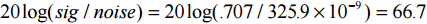

このノイズ電圧はADCの全体性能にどのような影響を与えるのでしょうか。ここでは、レシーバーの帯域幅内に存在するRF信号は1つだけとします。この場合、S/N比は次のようになります。

これはオーバーサンプリング・アプリケーションなので、実際の信号帯域幅はサンプル・レートよりはるかに狭くなり、デジタル・フィルタを通過した後はノイズが大幅に減少します。フロント・エンドの帯域幅はADCの帯域幅と同じなので、ADCノイズとRF/IFノイズは共に同じ率で改善されます。多くの通信規格が狭いチャンネル帯域幅をサポートしているので、ここでは30kHzのチャンネルと仮定します。したがって、プロセス・ゲインは33.4dBです。更に、オリジナルでは66.7dBだったS/N比が100.1dBになります。過大なノイズはフィルタで除去されるのでS/N比が増大し、これがプロセス・ゲインとなります。

図13.同電力の8個のキャリア(搬送波)

これがマルチキャリア無線の場合は、ADCのダイナミック・レンジを他のRFキャリアと共有する必要があります。例えば、同電力のキャリアが8個ある場合、ピークtoピーク信号を考えるときは、各信号が合計範囲の1/8以下でなければなりません。しかし、通常、レシーバー内の信号は互いに同位相ではないので(リモートがフェーズロックされていないため)、各信号が揃うことは全くないとは言えないまでも、極めて稀です。したがって、必要電力は本来必要とされる18dBよりはるかに小さくなります。実際には、任意の同一時点で揃う信号は2つまでであり、それらの信号は変調された信号なので、ヘッド・ルーム用に予約されるのは3dBだけです。信号が揃ってコンバータがクリップすることもあり得ますが、これが起こるのは、オーバードライブ状態がクリアされるまでのほんのわずかな時間だけです。シングルキャリア無線の場合、ヘッド・ルームは必要ありません。

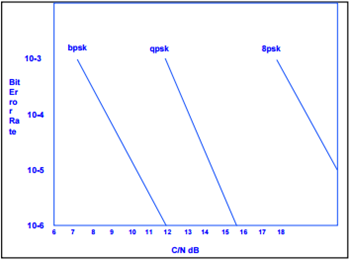

変調方法に応じ、適切な復調を行うには最小限のC/N比が必要です。方式がデジタルの場合は、以下に示すようにビット・エラー率(BER)を考慮する必要があります。10dBの最小C/N比が必要だとすると、維持できるS/N比が10dB未満になるほど入力信号レベルを小さくすることはできません。そのため、この場合の信号レベルは現在のレベルから90.1dB低下します。ADCのフルスケール・レンジは+4dBm(200Ω)なので、ADC入力における信号レベルは−86.1dBmです。RF/IFパスのゲインが25dBの場合、アンテナにおけるレシーバーの感度は−86.1dB − 25dB = −111.1dBmとなります。より高い感度が必要な場合は、RF/IF段のゲインを上げることができます。ただし、ノイズ指数はゲインと無関係ではなく、ゲインを大きくすると追加ゲイン段のノイズ性能にも悪影響が出ます。

ADCのスプリアス信号とディザ

ノイズに制限された例は、レシーバーの実際の制限を適切に示すものではありません。SFDRなどのその他の制限では、S/N比やノイズの場合よりも制約が多くなります。いま、A/DコンバータのSFDR仕様が−80dBFSまたは−76dBm(フルスケール = +4dBm)であるとします。また、キャリア(搬送波)と干渉波の比C/I比(C/N比とは別の値)の許容値が18dBであるとします。これは、最小信号レベルが−62dBFS(−80 + 18)あるいは−58dBmであることを意味します。アンテナでは、これは−83dBmです。したがって、以上により、SFDR(シングルトーンまたはマルチトーン)は、ノイズが実際の制限値に達するかなり前に、レシーバーの性能を制限します。

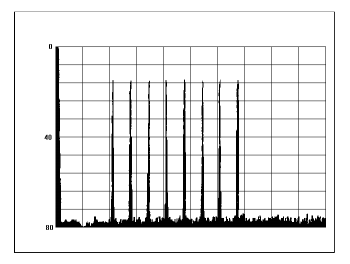

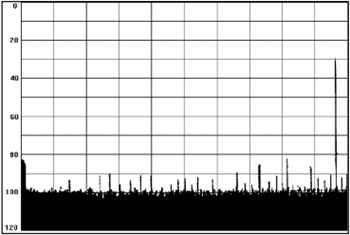

しかし、ディザと呼ばれる手法を用いればSFDRを大幅に改善できます。アナログ・デバイセズのアプリケーション・ノートAN410に示すように、帯域外ノイズを追加すると、SFDRを改善してノイズ・フロアに近付けることができます。ディザの量はコンバータにより異なりますが、この手法は、性能を制限しているのがスルー・レートなどのACの問題ではなく静的DNLである限り、すべてのADCに応用できます。アプリケーション・ノートに示されているAD9042では、追加ノイズの量は−32.5dBmあるいは21コードrmsにすぎません。以下に示すように、ディザ前後のプロットを見れば、どのように改善されるかを理解できます。簡単に言うと、ディザは、ADC内で発生するコヒーレントなスプリアス信号を捉えて、これをランダム化することによって機能します。スプリアスのエネルギーは保存されなければならないので、スプリアスはディザによって単純に追加ノイズとしてコンバータのフロアに現れます。これは、ディザ前後のプロットで、コンバータの平均ノイズ・フロアのわずかな増加として確認できます。したがって、帯域外ディザを通じて行われるトレードオフは、内部生成されたスプリアス信号を文字どおりすべて除去できる一方で、コンバータの全体的なS/N比にわずかな影響があるという点です。実際の影響は、ノイズを限定した例と比べた場合の感度低下が1dB未満で、前に示したSFDRを限定した例よりもはるかに良好な値です。

ディザを使用しないADC

ディザを使用したADC

このセクションを終わる前に、ディザに関する2つの重要な点を指摘しておきます。まず、マルチキャリア・レシーバーではチャンネル同士の相互の関連性は期待できません。この場合は、複数の信号が、受信チャンネルに対してしばしばセルフ・ディザとして機能します。これは多くの場合にあてはまりますが、信号強度が低下したときにディザを追加して不足を補わなければならないこともあります。

第2に、アナログ・フロント・エンドが関与するノイズだけでは、ADCのディザリングには不十分です。上の例では、最大限のSFDR改善を実現するために32.5dBmのディザが加えられています。これに対し、アナログ・フロント・エンドが関与するノイズ電力は−68dBmだけで、最適性能を実現するために必要な量にははるかに及びません。

3次インターセプト・ポイント(IP3)

コンバータのSFDRの他に、RFセクションはレシーバーのスプリアス性能にも影響を与えます。これらのスプリアスはディザなどの手法には影響されないので、受信性能を著しく低下させることがないように対処する必要があります。受信チェーン内の信号レベルはレシーバーの設計を通じて増大するので、3次インターセプトは重要な基準です。

広帯域RF部品にはどのようなレベルの性能が必要かを理解するために、ここで、恐らく最も要求の厳しいレシーバー・アプリケーションであるGSMの仕様を再確認します。

GSMレシーバーは、電力レベルが−13dBm~−104dBmの信号を復元できなければなりません。また、ADCのフルスケールが0dBmで、レシーバーのフィルタとミキサーを通じた損失が12dBであるものとします。更に、複数の信号を同時に処理するので、AGCは使用しません。このためRF感度が低下し、弱い信号を取りこぼしてしまうおそれがあります。この情報に基づいて計算を行うと、RF/IFゲインは25dB(0 = −13 − 6 − 6 + x)となります。

3次入力インターセプトに関する検討

25dBのゲイン要求は上記のように配分されます。システム全体としては他にも追加的な要素が存在しますが、この検討の目的には上記で十分です。これを見ると、−13dBmにおけるフルスケールGSM信号では、ADC入力が0dBmになります。ただし、最小GSM信号が−104dBmの場合、ADCの信号は−91dBmになります。この点から、上記の検討を使用して、ノイズ性能とスプリアス性能に関するADCの適合性を判断することができます。

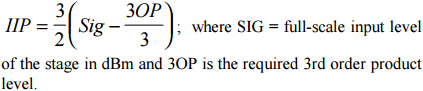

これで、必要とされるこれらの信号およびシステム・ゲインを使い、−13dBmのフルスケール信号で駆動した場合のアンプとミキサーの仕様が検討可能になりました。信号フルスケールに関する3次積を解くには、次式を使用します。

100dBを超える全体のスプリアス性能が必要なら、フロント・エンド・アンプに関してこの式を解くことで、このアンプの3次歪み(入力換算)特性にはIIP > +37dBmが必要なことがわかります。ミキサー入力では信号レベルが10dB上昇するので、ここでの信号レベルは−3dBmとなります。ミキサーの仕様は出力で規定されるので、信号レベルは6dB低下して−9dBmとなります。したがってミキサーについてはOIP > +41dBmが必要です。ミキサーはその出力位置で仕様が指定されるので。最終ゲイン段(IFアンプ)入力では信号が−9dBmになります(ミキサー出力と同じ)。そのためIFアンプではIIP > +41dBmが必要です。これらの仕様が満たされていれば、性能は次のようになります。

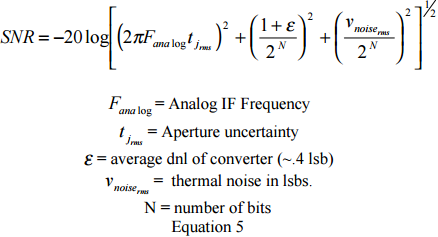

ADCクロック・ジッタ

良好な無線性能に不可欠な動的仕様の1つが、ADCクロック・ジッタです。低ジッタであることは優れたベースバンド性能にとって重要なことですが、アンダーサンプリング・アプリケーションなどに見られるように、より高い周波数の信号(より高いスルー・レート)でサンプリングを行うと、その効果が増大します。ジッタ仕様が不十分な場合の最終的な影響は、入力周波数の増大と共にS/N比が低下することです。アパーチャ・ジッタとアパーチャ不確定性という言葉はしばしば同じ意味で使われますが、このアプリケーションでも同じ意味で使用します。アパーチャ不確定性とは、エンコード・プロセスにおけるサンプル間の差です。アパーチャ不確定性には3つの除去できない効果があり、その第1はシステム・ノイズの増加、第2がサンプリングされた信号自体の実際の位相における不確定性、そして第3がシンボル間干渉です。必要なノイズ性能を実現するには、IFサンプリング時のアパーチャ不確定性を1ps未満とする必要があります。位相精度とシンボル間干渉に関して言えば、アパーチャ不確定性の影響は大きくありません。IFが250MHzのときの値が1ps rmsという最も条件の厳しいシナリオにおける位相の不確定性、あるいは誤差は、0.09ºrmsです。これは、GSMのような要求の厳しい仕様でも十分に受け入れられる値です。したがって、この分析では、焦点をアパーチャ不確定性による全体的ノイズへの影響に置きます。

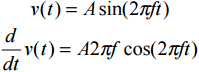

サイン波における最大スルー・レートはゼロ交差時に生じます。この点におけるスルー・レートは、t = 0で求められるサイン関数の1次微分によって定義されます。

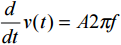

t = 0におけるコサイン関数の値は1で、式は次のように単純化されます。

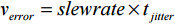

スルー・レートの単位はV/sで、信号が入力信号のゼロ交差点を通って立ち上がる速さを表します。サンプリング・システムでは、リファレンス・クロックが入力信号をサンプリングするために使われます。サンプル・クロックにアパーチャ不確定性があると、誤差電圧が生じます。この誤差電圧は、入力スルー・レートにジッタを乗じることによって求めることができます。

単位を分析することによって、この式から得られる結果はボルト単位であることがわかります。通常、アパーチャ不確定性は秒rmsで表されるので、誤差電圧はVrmsになります。この式を更に詳しく検討すると、アナログ入力周波数が高くなるにつれて、rms誤差電圧もアパーチャ不確定性に比例して大きくなることがわかります。

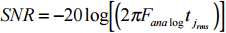

IFサンプリング・コンバータでは、クロックの純度が極めて重要です。ミキシング・プロセス同様、入力信号はローカル発振器、または今の場合はサンプリング・クロックによって逓倍されます。時間の乗算は周波数領域の畳み込みなので、サンプル・クロックのスペクトルは、入力信号のスペクトルによって畳み込みが行われます。また、アパーチャ不確定性はクロック上の広帯域ノイズなので、サンプリングされたスペクトル中にも広帯域ノイズとして現れます。さらに、ADCはサンプリング・システムなので、スペクトルが周期的で、サンプル・レートに従って繰り返されます。したがって、この広帯域ノイズはADCのノイズ・フロア性能を低下させます。アパーチャ不確定性によって制限されたADCの理論的S/N比は、次式で求められます。

この式を使い、201MHz、ジッタが.7ps rmsのアナログ入力に対する値を求めると、理論的S/N比は61dBに制限されます。ここで留意すべきなのは、これは別のミキサー段を使用した場合でも必要とされたはずの条件と同じだということです。したがって、非常に高いダイナミック・レンジとアナログ入力周波数を必要とするシステムでは、エンコード・ソースも、ジッタが非常に小さいものを使用する必要があります。標準的なTTL/CMOSクロック発振器モジュールを使用するときは、ADCも発振器も0.7ps rmsであることが確認されています。低ノイズのモジュールであれば、より低い値を実現できます。

全体的なシステム性能を考える場合は、より一般的な式を使用できます。この式は前の式に基づくものですが、熱ノイズと微分非直線性の影響が含まれています。

これは単純な式ですが、データ・コンバータを使用した場合のノイズ性能について多くの示唆を与えてくれます。

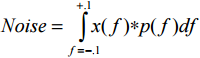

位相ノイズ

シンセサイザの位相ノイズはエンコード・クロックのジッタに似ていますが、レシーバーに対する影響がわずかに異なります。しかし全体として見た場合、それほど大きな違いはありません。ジッタと位相ノイズの主な違いは、ジッタはサンプル・クロックを中心とした均等な密度の広帯域問題であるのに対し、位相ノイズはローカル発振器を中心に不均等に分布しているという点です。位相ノイズは、得られるトーンから遠ざかるほど改善されます。ジッタ同様、位相ノイズも小さいほうが良いのは言うまでもありません。

ローカル発振器は入力信号とミキシングされるので、LOのノイズは必要な信号に影響を与えます。ミキサーの周波数領域プロセスは畳み込みです(ミキサーの時間領域プロセスは乗算)。ミキシングの結果として、LOの位相ノイズは、隣接する(アクティブな)チャンネルからのエネルギーがノイズ・フロアの上昇という形で目的のチャンネルに組み込まれる、という結果をもたらします。これは相互ミキシングと呼ばれます。代替チャンネルがフル・パワー信号によって占有されているときに未使用チャンネル内のノイズ量を求めるには、以下の分析を行います。

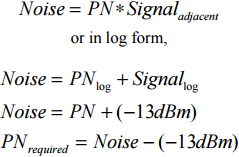

繰り返しますが、GSMは要求が厳しい仕様なので、ここに示すものはあくまで一例です。この場合は次式が成り立ちます。

ここで、Noiseは位相ノイズによって生じる目的チャンネルのノイズ、x(f)は非対数形式で表される位相ノイズ、p(f)はGMSK関数のスペクトル密度関数です。この例では、GSM信号電力−13dBmであるものとします。また、LOの位相ノイズは周波数によらず一定であるものとします(ほとんどの場合、位相ノイズはキャリア・オフセットと共に減少します)。これらの仮定の下にチャンネル帯域幅に対して式を積分すると、式を単純化できます。x(f)が一定(PN − 位相ノイズ)だと仮定していて、フルスケールGSMチャンネルの積分電力が−13dBmなので、式は次のように単純化されます。

目標は位相ノイズを熱ノイズより小さくすることなので、ミキサーにおけるノイズは、アンテナにおけるノイズと同じ−121dBm(200kHzでのアンテナにおけるノイズ − Pa = kTB)であると仮定できます。したがって、LOの位相ノイズは、オフセットが200kHzのときに−108dBm未満でなければなりません。