概要

設計リソース

設計/統合ファイル

- Schematic

- Bill of Materials

- Gerber Files

- PADS Files

- Assembly Drawing

評価用ボード

型番に"Z"が付いているものは、RoHS対応製品です。 本回路の評価には以下の評価用ボードが必要です。

- EVAL-CN0290-SDPZ ($243.64) Extending the Low Frequency Range of a High Performance Phase Locked Loop

- EVAL-SDP-CS1Z ($66.32) Eval Control Board

デバイス・ドライバ

コンポーネントのデジタル・インターフェースとを介して通信するために使用されるCコードやFPGAコードなどのソフトウェアです。

機能と利点

- 低周波数の範囲を拡大したフェーズ・ロック・ループ

- 局部発振周波数:最小10MHz、基準周波数:最小100MHz

- 低歪みと低位相ノイズ

マーケット & テクノロジー

使用されている製品

参考資料

-

AN-586: 高速A/DコンバータのためのLVDSデータ出力 (Rev. 0)2006/09/22PDF207 kB

-

AN-30: Ask the Applications Engineer - PLL Synthesizers2004/12/06PDF184 kB

-

Fundamentals of Phase Locked Loops (PLLs)2015/02/14PDF407 kB

-

MT-101: Decoupling Techniques2015/02/14PDF954 kB

-

MT-031: データ・コンバータのグラウンディングと、「AGND」および「DGND」に関する疑問の解消2009/03/20PDF144 kB

-

CN-0290: 高性能フェーズ・ロック・ループの低周波数の範囲を拡大する2013/09/24PDF311 kB

回路説明

周波数シンセサイザADF4106を使って、局部発振器の機能を必要とするRFレシーバ、トランスミッタ、シグナル・アナライザ、データ・ジェネレータなどのRFアプリケーションのアップ・コンバージョンとダウン・コンバージョンの部分に、局部発振器の機能を実装することができます。このシンセサイザに外部のループ・フィルタと電圧制御発振器(VCO)を組み合わせることで、フェーズ・ロック・ループ(PLL)が実現します。

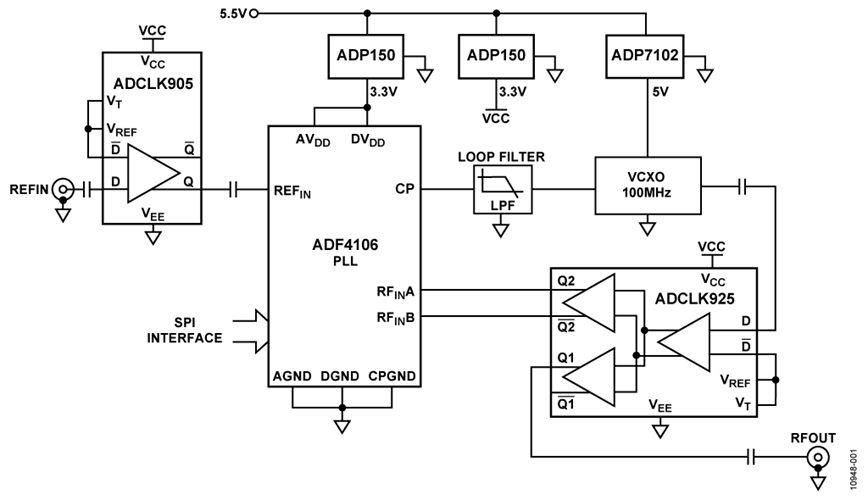

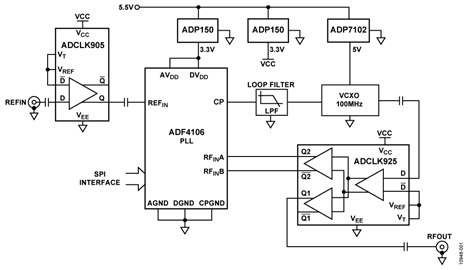

ADF4106はチャンネル・ステップ・サイズが整数NのインテジャーN PLLです。これはRF周波数の出力範囲が最大6GHzの使い易いデバイスで、標準−223dBc/Hzの低位相ノイズ(正規化された位相ノイズフロア)に対し規定されています。低ノイズで単一周波数のクロック・アプリケーションにADF4106を使ったフェーズ・ロック・ループのブロック図を図1に、簡略回路図を図2に示します。

低位相ノイズのフェーズ・ロック・ループの簡略回路図

低ノイズの10MHzリファレンス・ソースをADCLK905でバッファし、ADF4106 PLLのREFINにAC結合します。VCOは、出力がADCLK925の50Ω入力負荷にAC結合された、低ノイズの100MHzサイン波VCXOです。VCXOとADCLK925の間のインターフェースは、両方のデバイスが負荷と信号レベルの条件という点で整合がとれているため、非常にシンプルです。1:2バッファADCLK925の出力段は、RFOUT信号の供給とPLLに必要なRF帰還信号の供給を行います。

ADF4106 PLLには専用の3.3V低ノイズLDO ADP150から給電し、2つのクロック・バッファ(ADCLK905、ADCLK925)にはもう1つのADP150を使って給電します。ADP150の出力電圧ノイズはわずか9μV rmsで、これによりPLLとクロック・バッファの両方の位相ノイズを小さくできます。

低ノイズのVCXOには低ノイズの5Vリニア電圧レギュレータADP7102から給電し、VCOプッシュの影響を低減します(電源除去に相当)。

リファレンス入力クロック・バッファ

ADF4106の条件を満たすため、PLLのREFINとRFINの入力段のクロック・バッファは付加ジッタが小さく、動作周波数でのスルーレートが十分で、信号振幅が適切でなければなりません。

ADCLK905/ADCLK925は、広い入力スルーレート範囲で、付加されるランダム・ジッタが最小になるように特別に設計された、超高速のECLクロック/データ・バッファです。これらはフルスイングECL(エミッタ結合ロジック)出力ドライバを備え、伝搬遅延が95psでランダム・ジッタが60fsです。これらのデバイスの立上がり/立下がり時間(20%から80%/80%から20%)は60ps(typ)で、約8000V/µsのスルーレートに相当します。

ADCLK905は10MHzのREFIN周波数ソースをバッファするのに使用します。多くのアプリケーションで10MHzの基準周波数が一般的です。利用できる信号振幅の大きさによっては、スルーレートがADF4106の最小スルーレート条件の50V/µsecを満たさない場合があります。たとえば、10MHz、0dBmサイン波のスルーレートはわずか20V/µsです。

10MHzのソースのスルーレートを上げるため、REFINのクロック・バッファとしてADCLK905を選択しました。ADCLK905は付加ジッタが小さいことから、REFINのクロック・バッファによって生じる付加ジッタはごくわずかです。PLLの帯域内のリファレンス・ノイズは減衰されないため、リファレンス・ノイズを小さく抑えることが部品選択の大きな要素になります。ADCLK905の付加ジッタが60fsと小さいことがこれに該当します。50Ω環境では、入出力のマッチングが性能に大きな影響を与えます。ADCLK905の入力バッファは、両方のD入力に50Ωの終端抵抗を内蔵しています。これらの50Ω抵抗の間のセンター・タップVTは、相補D入力とVREFピンに外部で接続します。これらのピンをセラミック・コンデンサでデカップリングします。

ADCLK905のPECL出力段はVCC − 2 Vに終端した50Ωに800mVを直接駆動します。終端はそれぞれのADCLK905出力への1本の終端抵抗で行います。VCC = 3.3 Vの場合、グラウンドに対し150Ωを接続することを推奨します。

出力は伝送ラインを駆動するように設計されており、各出力ピンが負荷インピーダンスにマッチングしている必要があります。ADCLK905のQ出力は、ADF4106のREFINの高インピーダンス入力にAC結合する前に、50Ω負荷にAC結合します。使用しない相補Q出力は同じ負荷で終端する必要があります。

RF入力クロック・バッファ

ADCLK925を使って低ノイズのVCXOからの100MHzのRFINをバッファします。RFINに必要な最小スルーレートは320V/µsecです。ADCLK925はRFIN入力に必要なスルーレートを備えています。ADCLK925は付加ジッタが小さくPLL位相ノイズ性能に、ほとんど影響しません。ADCLK925の1:2の出力段は、スプリッタやマッチング部品を必要とせずに、PLLへの帰還を簡素化します。

PECLの出力段はVCC − 2Vに終端した50Ωに800mVを直接駆動します。これは、図2に示すように、追加の電源を必要とせずに1本の150Ω抵抗をグラウンドに接続することによって行います。ADF4106のRFIN入力段は最大信号レベルが±600mVに規定されています。30Ωの直列抵抗が、ADCLK925の出力振幅をこの値以下に抑えます。ADCLK925の出力はADF4106 の50Ωの差動入力にAC結合し、ADCLK925のもう一方の出力は同様に終端してRFOUT信号を供給します。

PLLの設計と性能

ADIsimPLL™ソフトウェアを使って、REFINが10MHzでRFINが100MHzという低い周波数を必要とするPLLのループ・フィルタを設計しました。このループ・フィルタの帯域幅は818Hzで位相マージンは45°です。

ADIsimPLLによる位相ノイズのシミュレーション結果を図3に示します。この図から、ADF4106のPLLループが低周波数でロックし、位相ノイズの増加を最小限に抑えることが分かります。

PLLシステムの位相ノイズの実測値を図4に示します。

シミュレーション結果

位相ノイズ・プロットの実測値

ループ・フィルタ部品の開発に用いられるADIsimPLLソフトウェアを使って、回路の性能をシミュレーションすることもできます。 ADIsimPLLでは、REFINとRFIN入力から供給される信号のスルーレートと信号振幅が適切であると仮定します。ADIsimPLLにより、ADF4106 PLLで使用するリファレンス・ソースをモデル化することができます。このセットアップに対するリファレンス・ソースはR&SのSMA100信号発生器です。シングルエンドの10MHz、0dBmリファレンス入力信号の位相ノイズを、10Hzと1MHzのオフセットでの測定値を使ってモデル化しました。AgilentのFSUPスペクトラム・アナライザを使って、これらのオフセットでのリファレンスの位相ノイズを測定しました。ADIsimPLLを使ってVCO性能をシミュレーションするためには、表1に示すように、データシートに記載されたADCLK925の位相ノイズとCVSS-945 VCXO(Crystek Crystals, 12730 Commonwealth Drive, Fort Myers, Florida 33913)の位相ノイズを統合する必要があります。

| Phase Noise Offset | ADCLK925 (dBc/Hz) | VCXO (dBc/Hz) | Total (dBc/Hz) |

| 10 Hz | −140 | −86 | −86 |

| 1 MHz | −158 | −172 | −157 |

10Hzのオフセットでの統合1/f位相ノイズは−86dBc/Hzです。ADCLK925のデータシートに記載された10Hzオフセットでの値、−140dBcは、統合1/f位相ノイズにほとんど影響を与えません。

1MHzのオフセットでの統合位相ノイズは−157dBc/Hzです。

ADCLK925データシートの1MHzのオフセットでの位相ノイズは–161dBc/Hzです。これは差動で測定されているため、シングルエンド出力を使用する場合には、データシートの測定ノイズフロアを3dBだけ調整する必要があります。VCXOの位相ノイズ、 −172dBc/Hzは統合位相ノイズにほとんど影響を与えません。

測定結果とシミュレーション結果の比較

位相ノイズと位相ジッタのシミュレーション結果と測定結果を表2に示します。位相ノイズは100Hz、2kHz、および100kHzのオフセットでの測定値です。位相ジッタは100Hz~30MHzの範囲の位相ノイズを積分したものです。このシミュレーションでは、ADIsimPLLプログラムがポイント・フロア・モデルを使ってリファレンスとVCOを求めます。この結果、ADIsimPLLのモデルは1/fノイズとノイズフロアでは非常に近い値になりますが、搬送波から中間のオフセットでは数dBの差が生じることがあります。

| Parameter | Simulated | Measured |

| PN Offset of 100 Hz (dBc/Hz) | −113 dBc/Hz | −114 dBc/Hz |

| PN Offset of 2 kHz (dBc/Hz) | −126 dBc/Hz | −122 dBc/Hz |

| PN Offset of 100 kHz (dBc/Hz) | −156 dBc/Hz | −156 dBc/Hz |

| Phase Jitter (100 Hz to 30 MHz) | 208 fs | 276 fs |

バリエーション回路

ADCMP553のような単電源のPECL/LVPECLコンパレータは、スルーレートが10V/µsec未満の信号でREFINが動作する必要があるアプリケーションに使用することができます。ADCMP553はADCLK905/ADCLK925と同様の出力段を使ってREFIN/RFIN入力を駆動しますが、コンパレータの入力は必要な信号振幅に対応する同相電圧で50Ωの信号源インピーダンスから駆動する必要があります。

高速CMOSコンパレータADCMP600のような他のバッファを使ってREFIN回路のスルーレートを上げることができますが、対象となるアプリケーションに対して付加ジッタを評価する必要があります。部品を追加することはいくらかのノイズ増加を生じ、帯域内位相ノイズと位相ノイズによるジッタを大きくする可能性があります。

これは、位相ノイズ性能の低下が許容範囲内のアプリケーションでは使用可能です。

クロック・バッファADCLK9xxファミリーは付加ジッタが非常に小さいデバイスですが、低スルーレートの信号入力では、この仕様が劣化します。この劣化の評価についてはADCLK9xxのデータシートを参照してください。

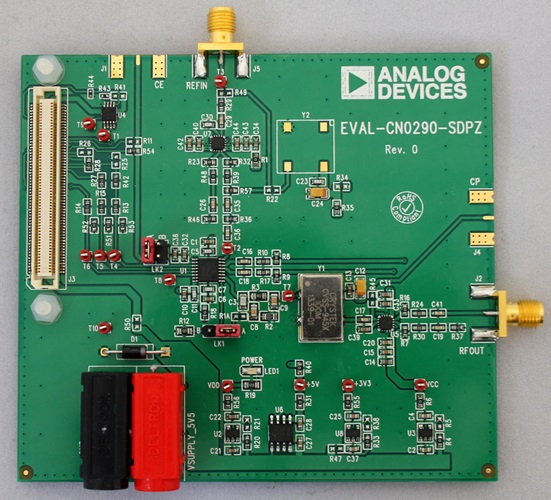

EVAL-CN0290-SDPZ回路ボードの写真を図5に示します。

回路の評価とテスト

この回路は、EVAL-CN0290-SDPZ回路ボードとEVAL-SDP-CS1Zシステム・デモンストレーション・プラットフォーム(SDP-S)評価ボードを使用します。これら2つのボードは120ピンの嵌合コネクタを備えており、回路の迅速なセットアップと性能評価が可能です。EVAL-CN0290-SDPZボードには、この回路ノートで説明されている回路が搭載されています。SDP-S評価ボードは、インテジャーNの評価用ソフトウェアと併用してADF4106の内蔵レジスタを設定します。

必要な装置

- USBポート付きPCおよびWindows® XP、Windows Vista®(32ビット)またはWindows® 7 (32ビット)

- EVAL-CN0290-SDPZ回路評価ボード

- EVAL-SDP-CS1Z SDP評価ボード

- インテジャーNのバージョン7以上の評価用ソフトウェア

- 電源電圧:+5.5 V

- RF信号源(R&SのSMA100または相当品)

- スペクトラム・アナライザ(AgilentのFSUPまたは相当品)

- SMAコネクタ付き同軸RFケーブル

評価開始にあたって

ソフトウェアのインストールとテスト・セットアップについては、UG-582ユーザー・ガイド(英語)を参照してください。設計サポート・パッケージ(www.analog.com/CN0290-DesignSupport)には回路図、レイアウト・ファイル、部品表が含まれています。詳細については、ADF4106、ADCLK905、およびADCLK925のデータシートを参照してください。

機能ブロック図

ブロック図についてはこの回路ノートの図1を、簡略回路図については図2を参照してください。テスト・セットアップのブロック図を図6に示します。

セットアップとテスト

装置をセットアップした後、標準のRFテスト方法を使用して回路の位相ノイズと位相ジッタを測定してください。