概要

設計リソース

設計/統合ファイル

- Schematic

- Bill of Materials

- Gerber Files

- PADS Files

- Assembly Drawing

評価用ボード

型番に"Z"が付いているものは、RoHS対応製品です。 本回路の評価には以下の評価用ボードが必要です。

- EVAL-CN0273-EB1Z ($81.21) High Speed FET Input Instrumentation Amplifier with Low Input Bias Current and High AC Common-Mode Rejection

機能と利点

- FET入力計装アンプ

- 広い帯域幅

- 小さいPCB面積

マーケット & テクノロジー

使用されている製品

参考資料

-

計装アンプの設計ガイド 第3版2006/01/02

-

MT-068: Difference and Current Sense Amplifiers2016/05/13PDF244 kB

-

MT-101: Decoupling Techniques2015/02/14PDF954 kB

-

MT-061: Instrumentation Amplifier (In-Amp) Basics2015/02/14PDF125 kB

-

MT-031: データ・コンバータのグラウンディングと、「AGND」および「DGND」に関する疑問の解消2009/03/20PDF144 kB

-

MT-064: In-Amp DC Error Sources2009/02/03PDF97 kB

-

MT-063: Basic Three Op Amp In-Amp Configuration2009/02/03PDF68 kB

-

CN-0273: 低入力バイアス電流で高AC同相除去比の高速FET入力計装アンプ2017/02/27PDF219 K

回路機能とその特長

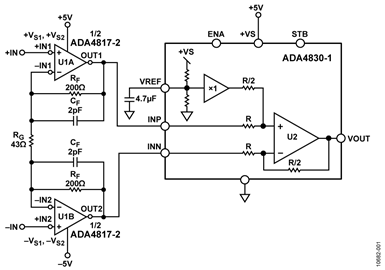

図1に示す回路は、帯域幅が広く(35MHz)AC同相除去比CMRが優れた(10MHzで55dB)、利得が5の高速FET入力計装アンプです。この回路は、RF、ビデオ、光信号検出、高速計測など、高入力インピーダンスで高速の計装アンプを必要とするアプリケーションに最適です。高いCMRと広い帯域幅により広帯域差動ライン・レシーバとしても最適です。

ほとんどのディスクリート計装アンプでは、高いCMRを実現するためにマッチング(値が一致)した高価な抵抗ネットワークを必要としますが、この回路では、マッチングした抵抗を内蔵したディファレンス・アンプを使って、性能向上、コスト低減、プリント回路ボード(PCB)レイアウト面積の最小化を図っています。

図1に示す複合計装アンプ回路は以下の性能を備えています。

- オフセット電圧:4 mV(max)

- 入力バイアス電流:2pA(typ)

- 入力同相電圧:−3.5V~+2.2V(max)

- 入力差動電圧:±3.5V/G1(max)(G1は初段のゲイン)

- 出力電圧振幅:0.01V~4.75V(typ)(150Ω負荷)

- 帯域幅(-3dB):35MHz(typ)(G = 5)

- 同相除去比:55dB(typ)(10MHz)

- 入力電圧ノイズ:10nV/√Hz(typ)(100kHz RTI)

- 高調波歪み:−60dBc(10MHz、G = 5、VOUT = 1 Vp-p、RL = 1 kΩ)

全機能内蔵の計装アンプのほとんどはバイポーラ・プロセスまたは相補型バイポーラ・プロセスで製造され、50Hzまたは60HzでのCMR値が高い低周波数アプリケーション用に最適化されています。しかし、ビデオ・システムやRFシステムにおいて、高速信号の増幅や不要な高周波信号の同相除去を行なう広帯域計装アンプの必要性が高まっています。

超高速で広帯域幅の計装アンプが必要な場合、一般的な方法として、初段に高入力インピーダンスの2つのディスクリート・オペアンプを使って差動入力信号のバッファと増幅を行い、2段目にディファレンス・アンプとして1個のアンプを構成することで、差動/シングルエンド変換を実現します。この構成は、一般的に3オペアンプ計装アンプとして知られています。この方法では、良好なCMRを得るのに、比較的高価で高精度にマッチングした4本の抵抗が必要です。マッチングの誤差は最終出力に誤差を生じます。

図1に示す回路は、高速ディファレンス・アンプ集積回路ADA4830-1を使用することによりこの問題を解決しています。レーザー・トリミングされた薄膜抵抗は非常に高精度にマッチングしているので、この比較的高価で高精度にマッチングした4本の外付け抵抗は不要です。

さらに、高速のデュアル・オペアンプADA4817-2を入力段アンプとして使用することにより、複合計装アンプで回路の総合ゲインが2.5のときに最大80MHzの帯域幅を実現できます。

単一の4mm × 4mm LFCSPパッケージのデュアル・アンプADA4817-2と集積化されたディファレンス・アンプADA4830-1でボード面積が大幅に低減されるため、大規模システムの設計コストが抑えられます。

ADA4817-2とADA4830-1のどちらも高い周波数で低ノイズと優れたCMR性能を提供するため、この回路はノイズの多い環境で使用することができます。

回路説明

この回路は、入力ゲイン段に2つのオペアンプ、出力段にディファレンス・アンプを使った従来型の3オペアンプ計装アンプ・トポロジーに基づいています。回路のゲインは5で帯域幅は35MHzです。

FETアンプの入力ゲイン段

FastFETアンプADA4817-2(デュアル)は、ユニティ・ゲインで安定した、FET入力の超高速電圧帰還アンプです。このアンプは、アナログ・デバイセズ独自のeXtra高速相補バイポーラ(XFCB)プロセスで製造されているため、超低ノイズとともに非常に高い入力インピーダンスと高速動作を実現できることから、高速動作と高ソース・インピーダンスを必要とするアプリケーションに最適です。

オペアンプADA4817-2はゲイン抵抗RGを共有するように構成されています。この回路の差動入力に対するゲインは1 + 2RF/RGです。入力が同相の場合、ゲイン抵抗RGには電流が流れません。このように、この回路は同相入力に対するバッファとして機能します。したがって、同相入力は実質的に2段目のディファレンス・アンプによって除去されます。

ADA4817-2のユニティ・ゲイン帯域幅積fuは410MHzです。クローズドループ帯域幅は次式で概算できます。

f−3 dB = fU/G1

ここで、G1は初段のゲインです。

この回路では、初段のクローズドループ・ゲインが10のときの−3dB帯域幅は41MHzと推定されます。この値はテスト結果の35MHzの帯域幅に非常に近い値です。

PCボードの寄生容量と容量性負荷によって最初のゲイン段に発振が生じる可能性があります。この問題は、小さい値の帰還抵抗を使用することと、帰還容量を使用することによって軽減することができます。

この回路では、200Ωの帰還抵抗を選択しました。帯域幅を最も平坦にするための帰還コンデンサCFは2pFになりました。

ディファレンス・アンプとCMR

ADA4830-1は、同相電圧範囲が広い高速デファレンス・アンプです。このデバイスは高速かつ高精度で、0.5V/Vの固定ゲインと84MHzの−3dB帯域幅を提供します。内蔵のレーザー・トリミングされた抵抗の代表的なCMRは10MHzで55dBです。

CMRは計装アンプにとって非常に重要な仕様であり、図2に示すように、2段目のディファレンス・アンプに使われる4本の抵抗比のマッチングに大きく依存します。

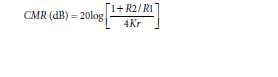

一般に、ワーストケースのCMRは次式で与えられます。

ここで、Krは分数で表した個々の抵抗の許容誤差です。上の式は、公称値が同じ値(許容誤差1%)の4本の抵抗に対するワーストケースのCMRが34dBであることを示しています。単体の抵抗を使用する代わりに、この回路はレーザー・トリミングされた薄膜抵抗を内蔵したモノリシック・ディファレンス・アンプADA4830-1を使用しているので、優れたCMRを実現し、PCB面積を低減します。CMRはDCで65dB、10MHzで55dBになります。

差動電圧と同相電圧に関する検討事項

入力電圧範囲を最大にし、電源条件を緩和するため、回路の初段を±5Vで動作させ、2段目を+5Vで動作させます。最大差動入力範囲はADA4817-2の出力振幅によって決まります。±5Vの電源では、ADA4817-2の出力振幅は±3.5Vです。したがって、最大許容差動入力は±3.5V/G1になります。ここで、G1は初段のゲインです。最大許容差動入力と初段のクローズドループ・ゲインはトレードオフの関係にあることに注意してください。

次に、同相電圧の制約について解析します。ADA4817-2の入力での同相電圧は、−VS to +VS − 2.8V、つまり±5V電源では−5V~+2.2Vの範囲でなければなりません。ADA4817-2の±5V電源での動作時の出力振幅は±3.5Vに制限されます(ADA4817-2のデータシートを参照してください)。このため、回路の負側の入力同相電圧は、ADA4817-2の出力振幅によって−3.5Vに制限されます。したがって、複合回路の許容入力同相電圧範囲は−3.5V~+2.2Vになります。

この回路で高性能を実現するには、優れたレイアウト、グラウンディング、およびデカップリング技術を駆使する必要があります。PCBレイアウトの詳細については、チュートリアルMT-031、チュートリアルMT-101、および技術記事「高速プリント回路ボード・レイアウトの実務ガイド」を参照してください。さらに、ADA4817-2のデータシートとADA4830-1のデータシートにはレイアウトのガイドラインも記載されています。

回路の性能

この複合回路の4つの非常に重要なパラメータであるCMR、−3dB帯域幅、入力換算ノイズ、高調波歪みをテストした結果を図3~図6に示します。

図3は、複合回路のCMRがDCで−65dB、10MHzで−55dBであることを示しています。図4は、ゲインが5で出力負荷が100Ωのときの帯域幅が35MHzであることを示しています。図5は、100kHzでの入力換算ノイズがわずか10nV/√Hz、それより高い周波数では8nV/√Hzのフラットバンド・ノイズであることを示しています。図6は、この回路の全高調波歪みが、VOUT =1 V p-pとRL = 1 kΩのときに10MHzで60dBcであることを示しています。

回路の評価とテスト

この回路は、信号発生器とオシロスコープを使って容易に評価することができます。このボードは、ネットワーク・アナライザを使った従来のアンプ・テスト方法でテストします。全体回路図とPCBレイアウトについては、CN0273設計サポート・パッケージを参照してください。ボードの写真を図7に示します。

図3のCMRRのデータは0Vの差動入力電圧に対して得られたものであることに注意してください。図4の帯域幅のデータと図6の歪みのデータは同相電圧が0Vの平衡型差動ドライブ・ソースを使って得られました。