ADN4693E

製造中マルチポイントLVDSトランシーバ、3.3 V、200 Mbps、全二重、高速、タイプ1レシーバ内蔵

- 製品モデル

- 2

- 1Ku当たりの価格

- 最低価格:$1.92

製品情報

- マルチポイントLVDSトランシーバ

(低電圧、差動シグナリングのドライバとレシーバペア) - スイッチング・レート:

200 Mbps(100 MHz) - 対応するバス負荷:

30 Ω ~ 55 Ω - タイプ1レシーバ・タイプ:

25 mVのヒステリシス - M-LVDS用のTIA/EIA-899 LVDS規格に準拠

- M-LVDSバス上のグリッチ・フリーのパワーアップ/パワーダウン

- ドライバ出力で制御される遷移時間

- コモンモード範囲:

-1 V ~ +3.4 V、

2 Vのグランド・ノイズでも通信可能 - ディスエーブル又は電源オフ時にドライバ出力は高インピーダンス

詳細はデータシートをご参照ください。

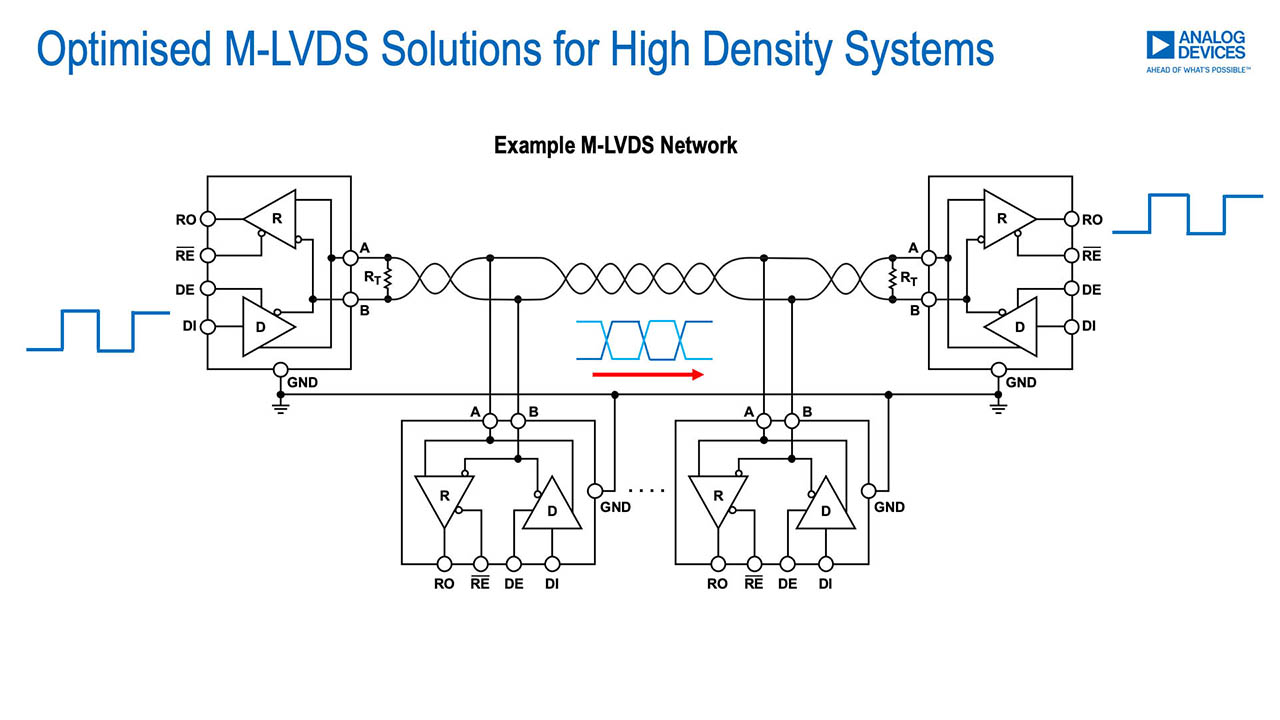

ADN4691E/ADN4693E/ADN4696E/ADN4697Eは、マルチポイント低電圧・差動・シグナリング(M-LVDS)のトランシーバ(ドライバとレシーバのペア)で、最大200 Mbps(100 MHz)まで動作することができます。レシーバは、-1 V ~ +3.4 Vのコモンモード電圧範囲にわたって50 mVもの小さな差動入力でバス状態を検出します。最大±15 kVまでのESD保護がバス・ピンに採用されています。これらの製品は、M-LVDSに関するTIA/EIA-899と、追加のマルチポイント機能が補足されているTIA/EIA-644のLVDSデバイスに関する規格を満たしています。

ADN4691E/ADN4693Eはタイプ1のレシーバで、25 mVのヒステリシスを持つように設計されていますが、その結果遅い変化の信号、あるいは入力の損失が出力発振を引き起こすことはありません。ADN4696E/ADN4697Eは、オフセット・スレショールドを備えたタイプ2レシーバで、バスがアイドルである(バス-アイドル・フェイルセーフ)とき、または入力がオープン(オープン回路フェイルセーフ)であるときの出力状態を保障しています。

これらの製品は、半二重構成(ADN4691E/ADN4696E)の8ピンSOICパッケージ、または全二重構成の(ADN4693E/ADN4697E)14ピンSOICパッケージで供給されます。

アプリケーション

- バックプレーンとケーブルのマルチポイント・データ・伝送

- マルチポイント・クロック分配

- 短いRS-485リンクの低パワー、高速の代替

- ネットワーキングと無線基地局インフラストラクチャ

ドキュメント

データシート 1

ユーザ・ガイド 1

アプリケーション・ノート 3

ビデオ 5

| 製品モデル | ピン/パッケージ図 | 資料 | CADシンボル、フットプリント、および3Dモデル |

|---|---|---|---|

| ADN4693EBRZ | 14-Lead SOIC | ||

| ADN4693EBRZ-RL7 | 14-Lead SOIC |

| 製品モデル | 製品ライフサイクル | PCN |

|---|---|---|

|

9 16, 2015 - 15_0129 Metal Mask Edits to ADN469XE Family of Devices. |

||

| ADN4693EBRZ | 製造中 | |

| ADN4693EBRZ-RL7 | 製造中 | |

これは最新改訂バージョンのデータシートです。