AD9652

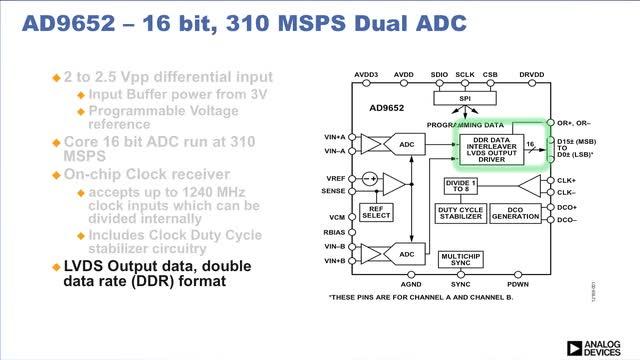

新規設計に推奨A/Dコンバータ、3.3 / 1.8V、デュアル、16ビット、310MSPS

- 製品モデル

- 2

- 1Ku当たりの価格

- 最低価格:$341.47

製品情報

- 高ダイナミックレンジ

- S/N比=75.0dBFS@70MHzv

(AIN=−1dBFS)

- SFDR=87dBc@70MHz

(AIN=−1dBFS)

- 詳細はデータシートをご参照ください。 - 優れたIFサンプリング性能

- S/N比=73.7dBFS@170MHz

(AIN=−1dBFS)

- SFDR=85dBc@170MHz(AIN=−1dBFS)

- フルパワー帯域幅465MHz - オンチップ3.3Vバッファ

- 2V p-p~2.5V p-p(デフォルト)の範囲で入力スパンをプログラム可能 - 整数1、2、4、8分周入力をもつ差動クロック入力レシーバ

(クロック分周器の入力は1.24GHzまで入力可能) - ADCのクロック・デューティ・サイクル・スタビライザを内蔵

- SYNC入力により複数デバイスの同期が可能

- 全消費電力:2.16W

- 電源電圧3.3Vと1.8V - DDR LVDS(ANSI-644レベル)出力

- シリアル・ポートの制御

- 省エネ・パワー・ダウン・モード

AD9652はサンプリング速度が最大310MSPSのデュアル16ビットA/Dコンバータ(ADC)です。AD9652は幅広い入力周波数範囲(最大465MHz)にわたって非常に大きなダイナミックレンジが要求される厳しい高速信号処理のアプリケーションに対応できるように設計されています。非常に優れたノイズフロア性能(−157.6dBFS)と大信号スプリアスフリー・ダイナミック・レンジ(SFDR)性能(85dBFS typ以上)により、大信号の中で微弱な信号を分離する事が可能になります。

デュアルのADCコアは複数段パイプライン・アーキテクチャを採用し、出力誤差補正ロジックを内蔵しています。高性能のオンチップ・バッファと内蔵電圧リファレンスは、ADCの非常に優れたダイナミック性能を保ちながら、外部駆動回路へのインターフェースを簡素化します。

AD9652は整数1、2、4、8クロック分周器を内蔵しているので、ADCのサンプル・クロックを生成するために使われる入力クロック周波数は最高1.24GHzまで対応できます。ADCのクロック・デューティ・サイクルの変動を補償するデューティ・サイクル・スタビライザを備えております。各A/Dコンバータからの16ビット出力データ(オーバーレンジ・ビット付き)は、ダブル・データ・レート(DDR)クロックと同調して、単一のLVDS出力ポートに交互に出力されます。セットアップやコントロールのためのプログラミングには3線SPI互換シリアル・インターフェースを用います。

AD9652は、144ボールCSP BGAを採用し、-40℃~+85℃の工業用温度の範囲で仕様が規定されています。この製品は申請中のU.S.特許によって保護されています。

製品のハイライト

- 310MSPSの16ビットADCを2個内蔵。

- オン・チップ・バッファによりADC駆動インターフェースが簡素化

- 3.3Vと1.8V電源と、LVDS出力に対応するもう1つのデジタル出力ドライバ電源により動作。

- 独自の差動入力により、485MHzまでの入力周波数で優れたSNR性能を維持。

- SYNC入力により複数デバイスの同期が可能。

- レジスタの設定や読み出しは3線、3.3Vあるいは1.8V SPIポートを使用。

アプリケーション

- 軍用レーダーと通信

- マルチモード・デジタル・レシーバ(3G又は4G)

- 試験装置と計測器

- スマート・アンテナ・システム

ドキュメント

データシート 2

ユーザ・ガイド 1

ビデオ 1

サードパーティ・ソリューション 1

デバイス・ドライバ 1

| 製品モデル | ピン/パッケージ図 | 資料 | CADシンボル、フットプリント、および3Dモデル |

|---|---|---|---|

| AD9652BBCZ-310 | 144-Ball CSPBGA (10mm x 10mm) | ||

| AD9652BBCZRL7-310 | 144-Ball CSPBGA (10mm x 10mm) |

| 製品モデル | 製品ライフサイクル | PCN |

|---|---|---|

|

2 11, 2015 - 14_0254 Bump and Assembly Transfer of Select 10x10 and 12x12 Flip Chip Products |

||

| AD9652BBCZ-310 | 製造中 | |

| AD9652BBCZRL7-310 | 製造中 | |

これは最新改訂バージョンのデータシートです。

ソフトウェア・リソース

デバイス・ドライバ 1

評価用ソフトウェア 0

必要なソフトウェア/ドライバが見つかりませんか?

ハードウェア・エコシステム

| 製品モデル | 製品ライフサイクル | 詳細 |

|---|---|---|

| クロックIC 2 | ||

| AD9530 | 新規設計に推奨 | クロック・ジェネレータ、低ジッタ、4 CML 出力、5.4 GHz VCO 内蔵 |

| AD9525 | 新規設計に推奨 | クロック生成器、8チャンネルLVPECL出力、低ジッタ |

| 可変ゲイン・アンプ(VGA) 2 | ||

| AD8375 | 製造中 | VGA、IF段、超低歪み |

| AD8376 | 新規設計に推奨 | VGA、デュアル、超低歪 |

| 差動アンプ 3 | ||

| ADL5566 | 新規設計に推奨 | 差動アンプ、デュアル、4.5GHz 、超高ダイナミックレンジ |

| ADA4938-2 | 新規設計に推奨 | ADCドライバ、差動、超低歪み、デュアル |

| ADA4930-2 | 新規設計に推奨 | 超低ノイズ・ドライバ・アンプ、低電圧 A/D コンバータ向け |

ツールおよびシミュレーション

Virtual Eval(仮想評価、 ベータ版)

Virtual Evalは、ADC、DAC、およびその応用製品評価を支援するウェブベースの設計ツールです。アナログ・デバイセズのサーバ上にあるモデルを使用して、重要な部品の性能特性をわずか数秒でシミュレートします。使用時は、入力トーンや外部ジッタなどの動作条件のほか、ゲインやデジタル・ダウンコンバージョンといったデバイス機能を設定してください。ノイズ、歪み、分解能、FFT、タイミング図、周波数応答プロット、その他さまざまな性能特性を確認することができます。

ツールを開く