AD9119

新規設計に推奨D/Aコンバータ、11ビット、5.6GSPS、RF用

- 製品モデル

- 2

- 1Ku当たりの価格

- 最低価格:$72.36

製品情報

- 最大5.6GSPSまでのDACアップデート・レート

- ダイレクト・RF合成@最大2.8GSPSのアップデート・レート、

-- DC~1.4GHz:ベースバンド・モード、

-- DC~1.0GHz(2倍インターポーレション・モード)

-- 1.4GHz~4.2GHz(ミックス・モード)

- 2倍インター・ポーレーションはバイパス可能

- 優れたダイナミック性能

- DOCSIS3.0ワイドバンドACLP / ハーモニック性能をサポート、

-- 8QAMキャリア:ACLR>65dBc - 詳細はデータシートをご参照ください。

AD9119 / AD9129は、高性能、11 / 14ビットのRF用D/Aコンバータ(DAC)で、最大2.8GSPSまでのデータ・レートをサポートします。DACコアはクワッド・スイッチ・アーキテクチャに基づいており、デュアル・エッジのクロッキング動作が可能で、ミックス・モードまたは2倍のインター・ポーレーション構成で、DACのアップデート・レートを、効率的に5.6GSPSまで増加させることが可能です。高ダイナミック・レンジと広帯域のため、最大4.2GHzまでのマルチキャリアの生成が可能です。

ベースバンド・モードでは、広帯域と高ダイナミック・レンジの組み合わが、CATVのインフラストラクチャ・アプリケーションのための1~158の隣接キャリアをサポートします。2つのオプションの2倍のインターポーレーション・フィルタの選択によって、DACのアップデート・レートを2倍に増加させることで、ポスト再生フィルタを簡素化することが可能です。

ミックス・モード動作では、AD9119 / AD9129は2ndと3rdナイキスト領域でRFキャリアを再生でき、しかも最大4.2GHzまでのダイナミック・レンジを維持します。高性能なNMOS・DACコアは、クワッド・スイッチ・アーキテクチャを特長としており、業界先端のRF合成性能を、出力パワーの損失を最小で、可能としています。出力電流は9.5mA~34.4mAの範囲にわたってプログラムすることができます。

AD9119 / AD9129は、更に簡潔なシステム統合を可能とする幾つかの機能を備えています。デュアル・ポートのソース同期式LVDSインターフェースは、ホストのFPGA / ASICとのデジタル・インターフェースを簡素化します。またインターフェースの正常性をモニタするため、差動のフレーム / パリティ・ビットも含まれています。オンチップの遅延ロック・ループ(DLL)は、異なるクロック領域間のタイミングを最適化するために使われます。

シリアル・ペリフェラル・インターフェース(SPI)は、AD9119 / AD9129を構成したり、リードバック・レジスタのステータスをモニタしたりするために使われます。AD9119 / AD9129は、0.18μmのCMOSプロセスで製造され、+1.8Vおよび-1.5Vの電源で動作します。この製品は、160ボールのチップ・スケール・ボール・グリッド・アレイ・パッケージを採用しています。

製品のハイライト

- 高ダイナミック・レンジで、信号再生帯域幅は最大4.2GHzまでのRF信号合成をサポート

- ダブル・データ・レート(DDR)のLVDSデータ受信を実現するデュアル・ポート・インターフェースは、最大変換レート2800MSPSをサポート

- CMOSプロセスで製造され、ダイナミック性能をさらに高めるため、弊社独自のスイッチング技術を使用

アプリケーション

- ブロードバンド・コミュニケーション・システム

CMTS / VOD、

無線インフラストラクチャ:W-CDMA、LTE、ポイントtoポイント - 計測器、自動テスト装置(ATE)、レーダー、妨害装置

ドキュメント

データシート 1

技術記事 1

| 製品モデル | ピン/パッケージ図 | 資料 | CADシンボル、フットプリント、および3Dモデル |

|---|---|---|---|

| AD9119BBCZ | 160-Ball CSPBGA (12mm x 12mm x 1.4mm) | ||

| AD9119BBCZRL | 160-Ball CSPBGA (12mm x 12mm x 1.4mm) |

| 製品モデル | 製品ライフサイクル | PCN |

|---|---|---|

|

2 11, 2015 - 14_0254 Bump and Assembly Transfer of Select 10x10 and 12x12 Flip Chip Products |

||

| AD9119BBCZ | 製造中 | |

| AD9119BBCZRL | 製造中 | |

これは最新改訂バージョンのデータシートです。

ソフトウェア・リソース

必要なソフトウェア/ドライバが見つかりませんか?

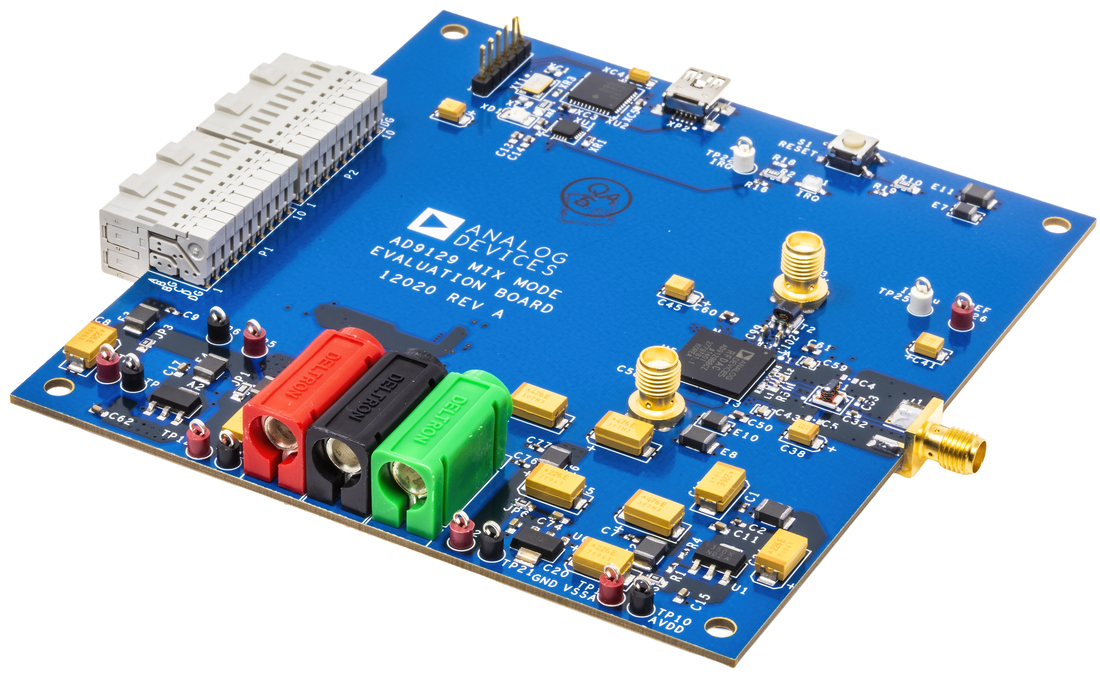

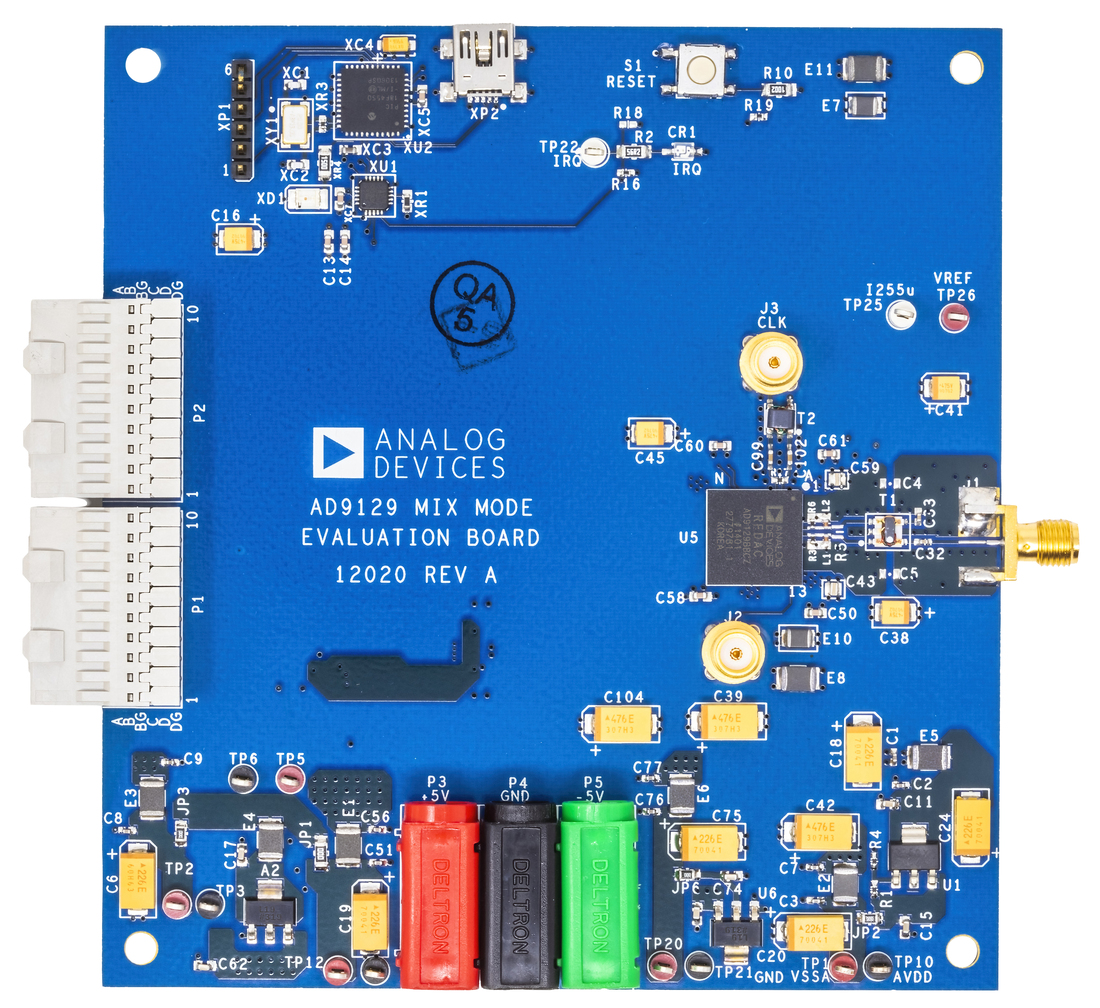

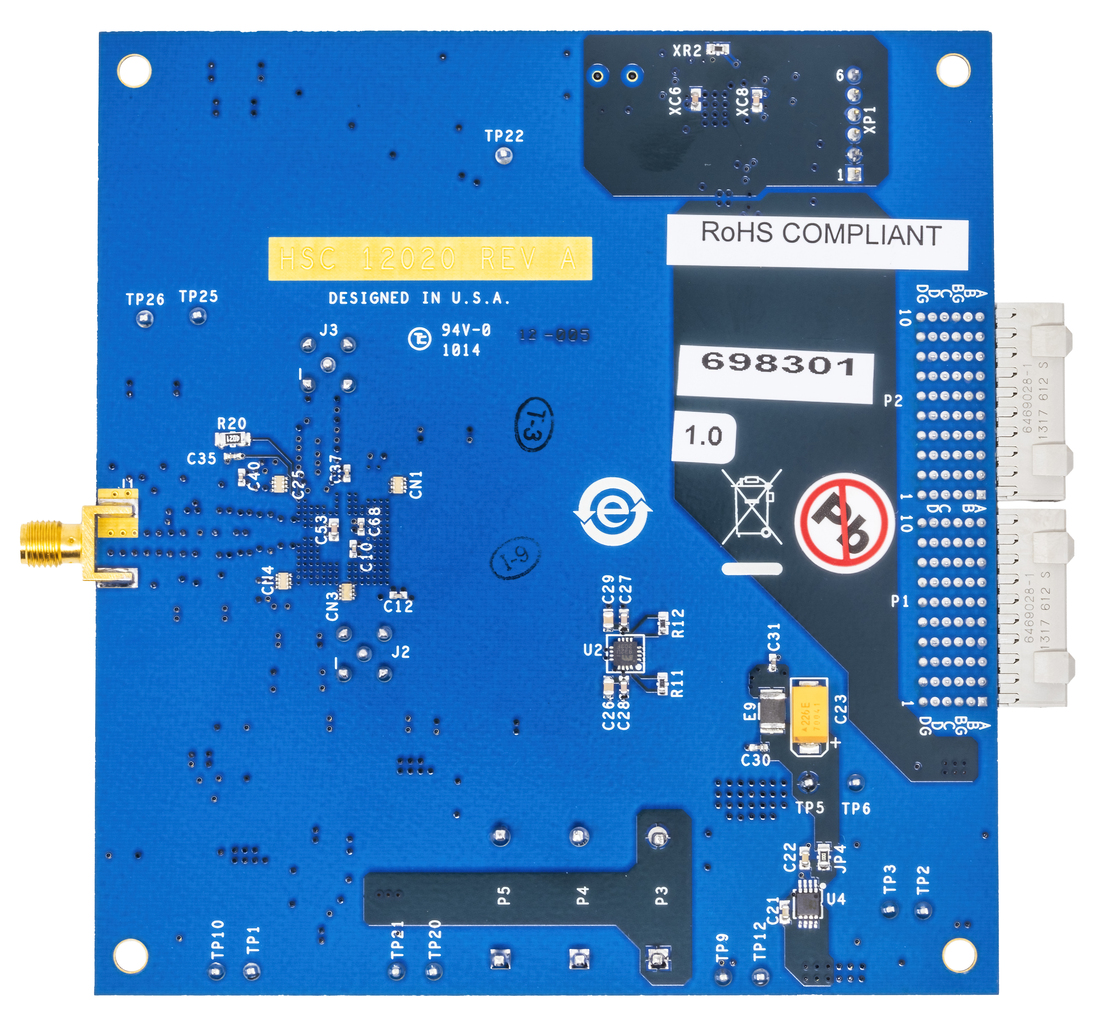

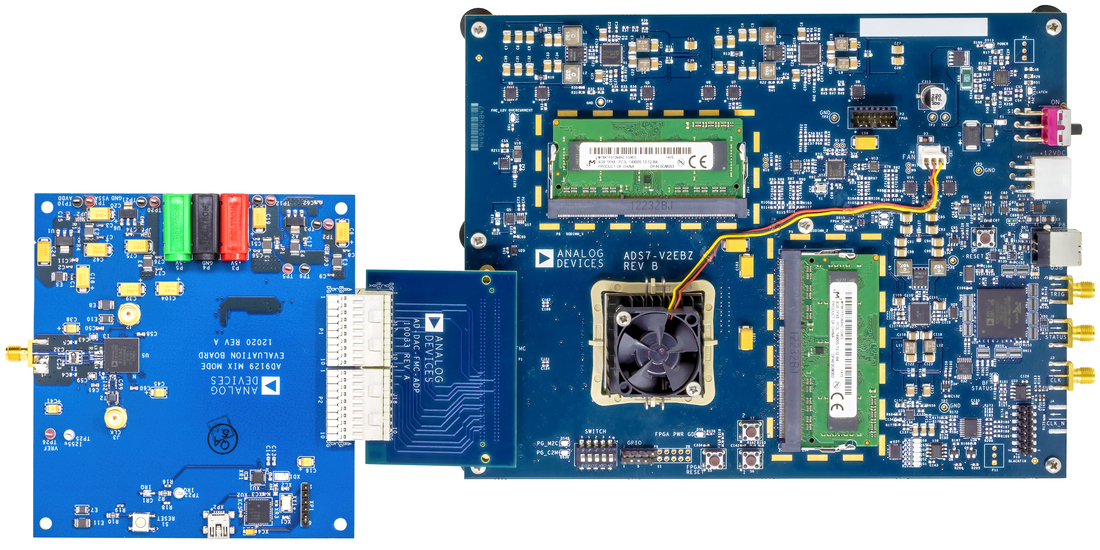

ドライバ/ソフトウェアをリクエストハードウェア・エコシステム

ツールおよびシミュレーション

Virtual Eval - BETA

使用する動作条件でADCおよびDACの性能をシミュレートします。

ツールを開く