Overview

Design Resources

Design & Integration File

- Schematic

- Bill of Materials

- Gerber Files

- PADS Files

- Assembly Drawing

Evaluation Hardware

Part Numbers with "Z" indicate RoHS Compliance. Boards checked are needed to evaluate this circuit.

- EVAL-CN0254-SDPZ ($101.52) Low Cost, 16-Bit, 250 kSPS, 8-Channel, Isolated Data Acquisition System

- EVAL-SDP-CB1Z ($134.00) Eval Control Board

Device Drivers

Software such as C code and/or FPGA code, used to communicate with component's digital interface.

Features & Benefits

- Precision conversion up to 8 channels

- Digital and power galvanic isolation

- Small board area

Product Categories

Markets and Technologies

Parts Used

Documentation & Resources

-

CN0254 Evaluation Board Guide10/22/2018WIKI

-

MT-101: Decoupling Techniques2/14/2015PDF954 kB

-

MT-049: Op Amp Total Output Noise Calculations for Single-Pole System2/14/2015PDF40 kB

-

MT-048: Op Amp Noise Relationships: 1/f Noise, RMS Noise, and Equivalent Noise Bandwidth2/14/2015PDF81 kB

-

MT-047: Op Amp Noise2/14/2015PDF72 kB

-

MT-031: Grounding Data Converters and Solving the Mystery of "AGND" and "DGND"3/20/2009PDF144 kB

-

CN-0254: Low Cost, 16-Bit, 250 kSPS, 8-Channel, Isolated Data Acquisition System12/30/2013PDF394 kB

Circuit Function & Benefits

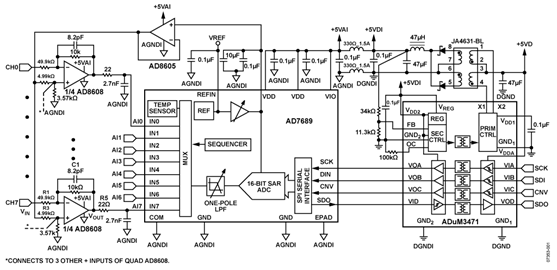

The circuit shown in Figure 1 is a cost effective, highly integrated 16-bit, 250 kSPS, 8-channel data acquisition system that can digitize ±10 V industrial level signals. The circuit also provides 2500 V rms isolation between the measurement circuit and the host controller, and the entire circuit is powered from a single isolated PWM controlled 5 V supply.

Circuit Description

This circuit uses the AD7689 16-bit, 8-channel, 250 kSPS PulSAR ADC along with two AD8608 low cost precision quad op amps to provide the entire signal conditioning and digitizing function in the data acquisition system. The only other op amp required is the AD8605 that is used to buffer the reference voltage from the AD7689.

The AD8605 and AD8608 are low cost single and quad rail-to-rail input and output CMOS amplifiers. The AD8608 inverts, level shifts, and attenuates the ±10 V input signal so that it matches the input range of the ADC, which is 0 V to +4.096 V when using a +4.096 V reference and a +5 V single supply.

The AD8605 acts as an external reference buffer to provide sufficient driving ability for level shifting. The AD8605 and AD8608 feature very low offset voltage, low input voltage and current noise, and wide signal bandwidth, therefore making them good choices for a wide variety of applications. The low current and voltage noise of the AD8608 ensures that the resistor noise is the dominant term in the output noise for high input impedance. In the circuit, the input impedance (equal to R1) is 50 kΩ.

The AD7689 16-bit, 8-channel, 250 kSPS PulSAR ADC contains all the necessary components for the multichannel low power data acquisition system. It includes a 16-bit SAR ADC, an 8-channel low crosstalk multiplexer, a low drift reference and buffer, a temperature sensor, a selectable one-pole filter, and a channel sequencer. The sequencer is useful for continuously scanning channels, and a microcontroller or FPGA is not required to control channel switching. The AD7689 is packaged in a tiny 20-lead 4 mm × 4 mm LFCSP footprint, thereby minimizing cost and printed circuit board (PCB) area. Operation is specified from −40°C to +85°C. Power dissipation with a 5 V supply at 250 kSPS is 12.5 mW (typical).

The ADuM3471 is a quad-channel digital isolator with an integrated PWM controller and transformer driver for an isolated dc-to-dc converter. The ADuM3471 provides the isolated 5 V, 2 W power for the circuit as well as isolates the digital signals at the SPI interface.

Analog Front End Design

Signal levels of up to ±10 V are typical in process control and industrial automation systems. An inverting amplifier with attenuation and level shifting is used in the Figure 1 circuit to convert the ±10 V signal into one that fits the range of the ADC.

The equation of the circuit is as follows:

The signal gain (−R2/R1) of the front end is set to −0.2 so that the range of the signal into the ADC is 4 V peak-to-peak. This fits the input range of 0 V to 4.096 V, which is equal to the reference voltage, VREF.

For a 0 V input signal, the output of the op amp should be at midscale or 0.5 VREF.

Substituting Equation 1 in Equation 2 yields

The common-mode voltage at the input of the op amp is calculated by

For R3/R4 = 1.4 and VREF = 4.096 V, the common-mode voltage of the op amp is 1.7 V.

There are four amplifiers in each AD8608, and the four noninverting inputs are shorted together and connected to a resistor divider, R3/R4. A second divider is used for the second AD8608. To cancel the op amp input bias currents,

The input impedance of the circuit is R1, which should ideally be high. However, a resistor has thermal noise which is proportional to the square root of resistance, and therefore, the system noise performance degrades as this resistor value increases. A simple noise analysis is needed to determine the optimum value.

Based on the Nyquist criteria, the maximum signal frequency component should be less than half of the maximum sample rate. The AD7689 250 kSPS sampling rate yields a Nyquist frequency of 125 kHz. To minimize the attenuation of a signal in this bandwidth, the −3 dB cutoff frequency of the front end is designed to be about 12 times the Nyquist frequency or 1.5 MHz.

The noise model of this circuit is shown in Figure 2. There are three noise sources in this circuit: resistor noise, amplifier voltage noise, and amplifier current noise. The rms value of each noise source is shown in Table 1. See Application Note AN-358, and the MT-047, MT-048, and MT-049 tutorials for more details about op amp noise.

The total rms noise in front of the ADC within the bandwidth of interest should be less than 0.5 LSB so that the input signal can be digitized correctly by the ADC.

The noise from the resistors can be calculated out by the following equation:

where R is in Ω.

The noise performance using the resistor values shown in Figure 1 and a bandwidth of 1.5 MHz is summarized in Table 1.

These uncorrelated noise voltages add in a root-sum-of-squares manner; therefore, the total op amp output rms noise within the 1.5 MHz bandwidth is approximately 21.3 μV. For a 4.096 V reference, the LSB for 16 bits is 62.5 μV. The rms noise of 21.3 μV is less than 0.5 LSB, and the resistor values shown in Figure 1 are suitable for this application.

Note that the largest contributor to the total output noise is the resistor R2, which is 10 kΩ in the circuit. Reducing the value of R2 requires a proportional reduction in R1, which reduces the input impedance.

The input current noise of the AD8608 is so small that it does not become a significant term unless extremely large resistor values are used. The low input current noise and input bias current of the AD8605 and AD8608 make them ideal amplifiers for high impedance sensors such as photodiodes.

The C1 capacitor is added in parallel with R2 to form a single-pole, active low-pass filter. The bandwidth is calculated using Equation 7. Given the 1.5 MHz, −3 dB bandwidth, C1 is about 10 pF. In the circuit, a value of 8.2 pF was chosen considering the parasitic effects of PCB board.

| Noise Source | RMS Noise Density | RTO Factor (Equation) | RTO Factor | Output RMS Density (nV/√Hz) | Output RMS Noise, 1.5MHz Bandwidth (μV) |

| eR1 | 28nV/√Hz | R2/R1 |

0.2 | 5.6 | 6.9 |

| eR2 |

12.6nV/√Hz | 1 |

1 | 12.6 | 15.4 |

| eR3 |

9nV/√Hz | (1+R2/R1)×{R3/(R3+R4)} |

(1+R2/R1)×{R3/(R3+R4)} | 0.5 | 4.5 |

| eR4 |

9nV/√Hz | (1+R2/R1)×{R3/(R3+R4)} |

0.7 | 5.6 | 6.9 |

| en | 6.5nV/√Hz | 1+R2/R1 | 1.2 | 7.8 | 9.6 |

| in+ | 0.01pA/√Hz | (1+R2/R1)×{(R3×R4)/(R3+R4)} | 2.5kΩ | 0.025 | 0.03 |

| in- | 0.01pA/√Hz | R2 | 10kΩ | 0.1 | 0.12 |

Analog-to-Digital Converter (ADC)

The AD7689 is a modern SAR ADC and uses an internal switched capacitor DAC. Because of the SAR architecture, there is no pipeline delay in the conversion process, thereby greatly simplifying multiplexed operation. The equivalent analog input circuit is shown in Figure 3. Small transient currents are injected on the analog input at the sampling frequency, and the external filter network composed of R5 and C2 reduces their effect on the op amp output. In addition, the filter has a bandwidth of 2.7 MHz and reduces noise at the ADC input.

With 4.096 V or 2.5 V selectable reference, the input range of this circuit can be switched between ±10 V and ±6 V without degrading the system resolution.

The internal temperature sensor can be used to monitor the junction temperature of the AD7689 and allows system calibration and temperature compensation in precision applications.

One-Chip Solution for Isolated Power and Digital I/O

The ADuM3471 is a single chip solution for both power and digital I/O isolation. The isolation voltage is 2500 V rms (recognized under UL 1577). The ADuM3471 provides a 4-channel isolated I/O port and an integrated PWM controller and transformer driver for an isolated dc-to-dc converter. Combined with a few external components, the ADuM3471 can provide 2 W isolated power with any regulated voltage from 3 V to 24 V. The necessary external components are one transformer for power energy transmission, two Schottky diodes for full wave rectification, an LC filter for ripple suppression, and two feedback resistors to set the output voltage. See the ADuM3471 data sheet and Figure 1 for more details.

Layout Considerations

The performance of this or any other high speed or high resolution circuit is highly dependent on proper PCB layout. This includes, but is not limited to, power supply bypassing, signal routing, and proper power planes and ground planes. See Tutorial MT-031, Tutorial MT-101, and the article A Practical Guide to High-Speed Printed-Circuit-Board Layout, Analog Dialogue 39-09, September 2005 for more detailed information regarding PCB layout.

A complete design support package for CN-0254 containing schematics, board layout, and BOM is located at https://www.analog.com/CN0254-DesignSupport.

System Performance

Figure 4 shows a plot of the ADC code occurrences for 10,000 samples (1 sec at 1 kSPS) when CH0 through CH7 are shorted to GND on the terminal block of the evaluation board. Note that 95% of the codes fall within 4 LSBs, and the peak-to-peak spread is approximately 7 LSBs. This corresponds to an rms value of approximately 7 ÷ 6.6 = 1.1 LSB.

The ac performance is shown in Figure 5. The sampling rate 250 kSPS is controlled by the system demonstration platform (EVAL-SDP-CB1Z), and the digital signal processing including the signal windowing and FFT is calculated on a PC by the CN-0254 evaluation software. The input sine waveform is a 20 kHz tone provided by a low distortion B&K sine generator, Type 1051.

Common Variations

For applications needing higher sampling rates, the AD7699 samples up to 500 kSPS and is the ideal pin-for-pin replacement for the AD7689.

The AD8615, AD8616, and AD8618 are single/dual/quad precision, CMOS, rail-to-rail input/output op amps with bandwidths up to 20 MHz. They can be used in applications requiring more bandwidth than the AD8605/AD8608 series.

The ADR3412 (1.200 V), ADR3420 (2.048 V), ADR3425 (2.500 V), ADR3430 (3.000 V), ADR3433 (3.300 V), ADR3440 (4.096 V), and ADR3450 (5.000 V) are low cost, low power, high precision CMOS voltage references, featuring ±0.1% initial accuracy, low operating current, and low output noise in a small SOT-23 package. These can be used instead of the AD7689 internal reference, if desired.

The ADuM3470, ADuM3471, ADuM3472, ADuM3473, and ADuM3474 are ideal choices for applications that need isolation for both power and digital I/O. The ADuM120x and ADuM140x families are used for isolated I/O extension. For high data rates, the ADuM344x family supports up to 150 Mbps.

Circuit Evaluation & Test

Equipment Needed (Equivalents Can Be Substituted)

- PC with a USB port and Windows® XP, Windows Vista (32-bit), or Windows 7 (32-bit).

- EVAL-CN0254-SDPZ circuit evaluation board

- EVAL-SDP-CB1Z system demonstration platform evaluation board

- Power supply: 6 V dc, 500 mA

- CN0254 evaluation software

- B&K Sine Generator Type 1051

Getting Started

Load the evaluation software by placing the CN-0254 evaluation software CD in the CD drive of the PC. Using My Computer, locate the drive that contains the evaluation software CD and open the Readme file. Follow the instructions contained in the Readme file for installing and using the evaluation software.

Functional Block Diagram

Figure 6 shows a functional block diagram of the test setup. The EVAL-CN0254-SDPZ-PADSSchematic pdf file contains the detailed circuit schematics for the CN-0254 evaluation board. The CN-0254 Design Support Package including schematics, PCB layout, BOM, and Gerber files can be downloaded at: https://www.analog.com/CN0254-DesignSupport.

Setup and Test

Connect the 120-pin connector on the CN-0254 evaluation circuit board to the CON A or CON B connector on the EVAL-SDP-CB1Z evaluation (SDP) board. Use nylon hardware to firmly secure the two boards, using the holes provided at the ends of the 120-pin connectors. After successfully setting the dc output supply to 6 V output, turn the power supply off. Connect 6 V to CN2. Turn on the power supply and then connect the SDP to the PC by using the USB-to-miniUSB cable.

After setting up the power supply and connecting it to the EVAL-CN0254-SDPZ circuit board, launch the evaluation software. Click Connect so that the software can communicate with the SDP board. The SDP board can be used to send, receive, and capture serial data from the EVAL-CN0254-SDPZ board. The data in this circuit note was generated using a B&K sign generator, Type 1051. Information regarding the SDP board can be found at: www.analog.com/SDP.