TNJ-022:設計開発ストーリー「VGA(可変ゲインアンプ)を使用した広帯域かつ高減衰の可変アッテネータ基板の実現」前編 ~構想から試作基板組み上げまで~

TNJ-022:設計開発ストーリー「VGA(可変ゲインアンプ)を使用した広帯域かつ高減衰の可変アッテネータ基板の実現」前編

著者

石井 聡

2016年09月05日

2016年9月5日公開

はじめに

CQ出版社から「すぐ使えるディジタル周波数シンセサイザ基板[DDS搭載]」という本を2012年9月に上梓しました(図1)。この本に付属するデジタル周波数シンセサイザ基板(アナログ・デバイセズでは「ディジタル」は「デジタル」で統一していますので、この技術ノートでも「デジタル」を用います)はDDS ICのAD9834を利用したものです。私はその執筆・開発プロジェクトの中で、94.5dBの減衰量をもつ30MHz広帯域アッテネータを主に担当しました。

ここでアッテネータ(Attenuator, 以下「ATT」を用います)の機能を実現するために、AD8369というVGA(Variable Gain Amplifier; 可変ゲイン・アンプ)を利用しました。当初は「これで30MHz程度までの48dBステップATTを作ってみますか!」というところでしたが、可能であれば外部に48dBの固定ATTをつけて、全体で95dB程度まで変化させたいという野望がありました。飛び込みや段間の迷結合の心配がありますが、「シールドナシで、どうだろうなあ…」と思うところでした。

すぐ使えるディジタル周波数シンセサイザ基板[DDS搭載]

この技術ノートでは、この94.5dBステップATT回路の実験・試作ネタ(エンジニア的にはこれを「遊び」という場合もあります)をご紹介します。まずは使用したVGA IC AD8369(可変ゲイン・アンプ、デジタル制御、45dB、600MHz )についての概要をご紹介しておきましょう(図2)。

【概要】

AD8369は、高性能のデジタル制御可変ゲイン・アンプであり、セルラ・レシーバ内のIF周波数で使用できるように設計されています。 このデバイスは、パラレルまたは3線式シリアル制御のいずれかに設定できる4ビット・デジタル制御のゲイン制御インターフェースを備えています。ゲイン制御レンジは、全体で45dBになり、3dBの単位で調整可能です。

AD8369は、デジタルIFレシーバでの使用に最適で、70/140/ 190/240/380MHzの一般IF周波数で動作するように完全に仕様規定しています。ゲインの安定性と平坦性は、380MHzで20MHzのチャンネル帯域幅にわたって0.1dB未満です。

VGAで実現するステップATTの構想を開始!

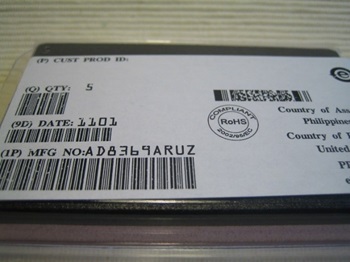

さっそくVGA ICのAD8369ARUZをゲットしました(図3と図4)。あわせて図5の写真は、秋月電子で買ってきた16ポジションのロータリ・スイッチです。16ポジション = 4ビットですから、3dBステップで48dB変化させることができます。

これに48dB固定アッテネータを追加すれば、合計約95dBのテップATTが実現できます。なおAD8369は利得があるので、その利得分を入力で減衰させる必要があります。

図3. 早速入手したAD8369ARUZ(その1:パックいり)

図4. 早速入手したAD8369ARUZ

(その2:パックから出した静電シート上のようす)

ブロック・ダイヤグラムをまず作ってみた

思考を整理し、レベル配分を考え、回路図に落とすために、簡単なブロック・ダイヤグラムを作ってみました。これを図6に示します。

VGAのAD8369プラス、もう一つ48dBの固定ATTをスイッチして、全体で約95dBを実現するというもくろみなのですが、電子スイッチで実現するのがちょっとやっかいだなあとか(アイソレーションとON抵抗の問題)、構想をブレークダウンしながら考えていきました。

(最終的には40dB→48dBになる)

広い減衰可変範囲を実現するには(ご経験を拝聴する)

構想途中に、執筆でご一緒した筆者の方から、「可変ゲイン・アンプといえば、AD8331というアナログ電圧でゲイン制御をするICを使ったことがありますよ。非常に低雑音のプリアンプも内蔵されていて、ゲイン可変範囲が48dBなので、これを2段カスケードにして、100dB以上のゲインと96dBのゲイン調整範囲を稼ぎました」「全段差動なので、GNDの共通インピーダンスに起因する迷結合などはほとんど無くて、100dB以上のゲインでもシールドなしで安定して動作しました」「ネットアナで見ながらAGC電圧を変えると、周波数特性はそのままで、きれいにゲインが上下します。可変アッテネータ・タイプなので、歪みも少ないですしね」というお話をいただきました。ここには2点ポイントがあって、

①「全段差動なので、GNDの共通インピーダンスに起因する迷結合などはほとんど無く」は、(以降にも説明しますが)ダイナミック・レンジが非常に広いため、コモンモード.・差動変換による想定外のフィードスルーが出てしまうという、一般的によく生じる問題があるが、差動回路ではこれが軽減される

②「周波数特性はそのままで、きれいにゲインが上下」は、ゲインを変えると周波数特性が変化するOPアンプと異なり、アンプのゲインは固定で、前段が可変アッテネータになっているため、このような性能が実現できる

ということなのでした。この方のお話には、深い造詣があったわけですね…。

この筆者さんは、100dBのゲインブロックを実現したわけですが、私のほうの設計は入力信号を減衰させることが目的…、なおかつAD8369にはゲインがある…。どんなものかなあとか、上記の附加48dB固定ATT回路の件など、悩み気味でした。

「AD8369が、Rset(抵抗1本)かなんかで、内蔵ポストアンプの利得調整ができるといいなあ」とか思いました。

構想をもとに回路図をひいてみた

ご一緒した筆者さんの「差動で…」というアイディアをいただいて、コモンモードによる外からの飛び込みや段間の迷結合の影響を受けづらい回路を実現しようと考えていました。

最初に考えた原始天地創生(?)回路を図7に示します。だいぶ悩みました…。入力はシングルエンドですが、VGA AD8369へは初段 の固定ATTで差動信号に変換して信号を加え、出力側は差動出力で負荷を駆動しています。

広い減衰可変範囲を実現するには(差動固定ATTの設計を安全サイドで考えた)

減衰量が大きいときにはVGA AD8369出力を差動構成の固定ATT(以降「差動固定ATT」)で、40dB(ところで「なぜ40dBなの?」というのは、実は間違えていたためで、あとで48dB必要ということに気がつきましたが、本編では当面は図7のとおり40dBで説明していきます)減衰させるのですが、「30MHzまで安定して減衰させるためには?」とだいぶ悩みました。週末もプールで泳ぎながら考えていたら、溺れるかと思いました(うそ)。そのため最初は安全策で、このように20dBを2段にしてみました。

なお減衰量が小さいときは、この2段の差動固定ATTをアナログスイッチでバイパスします。

最終的に差動固定ATT出力をOPアンプ(図7には図示していません)で差動-シングルエンド変換します。これによりコモンモードの飛び込みや迷結合を大きく低減させるという算段です。

(素子定数は暫定、また部品番号は付与していない。出力OPアンプは図示していない)

30MHzまで安定に減衰させることの最大の問題は、差動固定ATTをスイッチするアナログスイッチの、オン抵抗とオフリーク(フィードスルー)そして寄生容量です。高速アナログスイッチADG719を使ってはいますが、やはりどんなものか、だいぶ不安でした。最初は「40dB一発では30MHzまでは無理かなあ?」ということ、またあまり時間的、設計コスト的に後戻りできないため、安全策で20dBを2段で考えました。

そこで図7のような厳重な回路にしてみたわけです。とはいっても、20dBを2段だなんて…、アナログスイッチ8個!だなんて「無駄」ですよね。

デジタル・ポテンショメータで出来ないか?とも思いましたが、1kΩ型の低抵抗のものでも数MHzまでの周波数特性であり、使うことができません。

差動固定ATT回路を2段から1段へ簡略化できるものだろうか

心配していた差動固定ATT回路の性能を、NI Multisim(本技術ノートの執筆時点ではADIsimPEではなく、NI Multisimを使っていたため)でスイッチ部分だけシミュレーションして試行錯誤したところ、良好な結果(シミュレーション上では-0.2dB @30MHzという素晴らしい性能が!)が得られましたので、図8のような回路に変更しました。といっても、これから試行錯誤が始まるのでした…。そしてその試行錯誤が「休むに似たり」という結果に終わるのでした…。

以降でこのNI Multisimで検討した経緯を詳しく示していきます。

差動固定アッテネータの周波数特性を解析開始!

VGAご本尊の試作に到達するまえに、心配ネタである、この差動固定ATTの性能解析をしていきました。

その日も出版社から長いメールがきて、見逃してしまうところでしたが、よくよく読むと「1ヵ月後にはファイナル回路図を提出せよ」と…(汗)。ぜんぜん出来てない状況ゆえ、ダチョウ倶楽部モードで「聞いてないよぉ」と回答をしてしまいました(笑)。このように時間も限りがあるわけです。

広いゲイン調整範囲を実現するためにシミュレーションでアタリをつける

さて、ということで30MHz まで安定に動作する40dB(先のように間違いで…。最終的には48dB)の差動固定ATTを作らないといけません。そこでNI Multisimを使って、図9のような回路で特性を検討してみました。差動回路なので、1/2の上半分にして簡素化し、シングルエンドでシミュレーションしています。信号源抵抗は差動470Ω(図8のR9に相当)で、相当するシングルエンドのシミュレーション回路(図9)では235Ωにして最初は設計してみました。

「なぜ470Ωにしたの?」というご質問は当然でしょう(汗)。「そんな感じで…、まあ470が好きだから」とかワケの判らないような理由で選んでいます。回路専門外の方はこのいい加減さには驚くでしょう(汗)。といってもこの選定が問題になってしまったのでした。

図9差動ATT(図8)を1/2にして

シングルエンドでシミュレーションしてみる

図10 40dBのATT状態でシミュレーションしてみた。

30MHzで0.564dBほどダレている

図11 ためしに20dBのATT状態にしてシミュレーションしてみた。

ダレは0.272dBになっているが、2段つなげば40dBで1段の場合と同レベルの特性になってしまう

図10は1段で40dB ATTとしてシミュレーションしてみた結果です。30MHzの位置のマーカを見てください。上側はdy = 0.564dBになっており、この周波数でダレが生じています。下はy1 = -19.8°で結構位相が回っています。

つづいて図11は、図9のR2 = 2200Ω(図8のR12, R18に相当)だったものを220Ωにして1/100(-40dB)から1/10(-20dB)にしてみました。信号源抵抗があるので、ぴったり-20dB、1/10にはなっていないのですが、検討上ということで、まずはこれでやってみました。

30MHzのダレはdy = 0.272dBになっており、40dBと比べて、まあ1/2程度といえるでしょう。位相はy1 = -17°であまり変わらないです。

「20dB一段で0.27dB、2段つなげれば0.54dBであり、これなら1段で40dB取った場合となんら変わらんではないか?!逆に位相特性は悪くなるぞ!」ということになってしまいました。20dB ATTを2段でも性能が出なかったわけです。

ここで「本来は…、特性はもっと向上するはずだ」と直感的に考えました。そのため、「すいません、性能が出ませんでした」と簡単にあきらめるのではなく、「なんでだ?」ともう少し粘って追ってみました。

アナログスイッチの容量が影響を与えていた!

シミュレーションでは図9のR4(図8のR13, R17に相当)の端子電圧を見ていますが、ここで想定される支配的容量要因はR2(図8のR12, R18に相当)両端に接続されるアナログスイッチS1 ADG719(図8のIC2, IC5に相当)のスイッチ端子間オフ時容量(ドレイン・ソース間容量)CDSです。これが影響を与えていることに違いはなさそうでしたが、どのように与えているのか?と考えながら試行錯誤してみました。

シミュレーションはこんなときに便利です。図9のR1 // R2の並列抵抗(S2がオンしているため)とこの容量が、やはりダレを生じさせてしまう原因だと分かりました!

テキトーに選んだ470Ω(回路上ではシングルエンドでR1 = 235Ω)が大きいために、時定数が長めになってしまっていたのでした(涙)。

続いてしつこく試行錯誤のシミュレーション

「R1 // R2の並列抵抗が問題であるなら、図9のR1(図8のR9に相当)を小さくしてみればよいのだ!」「470Ωといわず、AD8369のデータシートで最小規定の200Ω(シングルエンドでR1 = 100Ω相当)にしてみればよいのだ!」と思い至るわけです。

というわけで、シミュレーションしてみました。図12のように、30MHzで利得dy = -0.124dB、位相y1 = -9°という結果になりました(やれやれ)。

乗算D/Aコンバータでも(低周波なら)ATTを実現できる

犬か?ネコか?はいざ知らず、社内を歩いていたら棒に当たり、「乗算型D/Aコンバータ」の製品カタログを見つけました!

10MHz程度の帯域なら、これで精密なレベル制御が出来るATTの実現が可能です。

結構多数の製品が用意されていますので、是非ご活用ください(^_^)。

差動固定ATT…もがけばもがくほど…

「これでよかった、やれやれ」と思ったところで、40dBが間違いだったことに気づき、規定の48dBの減衰量まで持っていってみました。-8dBのため、図9のR2(図8のR12, R18に相当)を2200Ωから5100Ωにしてみました。「を!今度はアナログスイッチの容量でフィードスルーが生じている!(汗)」

R4 = 22Ω(R4は図8のR13, R17に相当)でシミュレーションしてみたのが、図13の結果でありました…(涙)。「まあ後段のOPアンプでダレるから、少しピーキングしてさせてもいいか?」というところではありますが…。

このR4をあまり小さくすると、シャント接続されているアナログスイッチS2のオン抵抗が誤差要因になってきます。とはいえ一応は…、と思い、R4 = 22Ωから18Ωに変えてみた結果を図14に示します。あまりかわらないですね(がっくり)。

本番の48dBに相当するように、R2を大きく(5100Ω)してみると、ピーキングが生じている

R4 = 22Ωから18Ωに変えてみたがあまり変わらない

ここでもアナログスイッチの容量が影響を与えていた!

この原因も、アナログスイッチS1のオフ時容量CDSが原因と推測されます。

このCDSは、図8のIC2およびIC5の5 pin – 6 pin間の容量になります。差動固定ATTが有効な状態では、IC2, IC5の5 pin – 6 pin間はオフとなり、容量成分となります。

アナログスイッチADG719のデータシート上では、スイッチ端子の対地容量(ドレイン容量)として、CD = 7pFと記載があります。CDSとしてどれほどかは未知数ではありますが、同じ程度の大きさと推測していました。

どうやって対処する?! インダクタでやってみよう!

このCDSがアイソレーションを悪化させる要因になるわけですが、「何とかキャンセルできないか?」というのを少し考えました。思いついたアイディアは「インダクタでキャンセルする」というものです。

CD ≒ CDS ≒ 7pFは30MHzで-j760Ω程度です。これを、インダクタを用いて、並列共振構成でキャンセルすると、必要なインダクタンスは4uH程度になります。

ここで「できれば図8のR12, R18(2200Ωから5100Ωに増やしたもの)にシリーズにインダクタを入れて、うまくキャンセルしたい」と考えました。並直列変換の式で計算してみると(計算が間違っていたのかもしれませんが)複素数になったので「ややこしいなあ」ということで、シミュレーションで検討してみました。

回路を図15に示します。このようにR2(図8のR12, R18に相当)にシリーズにインダクタを挿入し、アナログスイッチのCDSをキャンセルさせてみました。

結論を言うと、以降に説明するように、この検討も「休むに似たり」で、最適ではなかったわけなのですが…。

最適なポイントが求められる

図17 パラメータスイープの結果。1, 2, 3, 4, 5uHの5段階でシミュレーション。

2nHでほぼフラット(最後の結論は、これらの検討も「休むに似たり」で最適ではなかった)

パラメータスイープ機能で最適値をみつける

NI Multisimさんに考えさせて答えを求める、というわけではありませんが、図16のように「パラメータスイープ」という機能を用いて、インダクタの大きさを変えていき、それぞれでACシミュレーションしてみる、というアプローチができます。

なおパラメータスイープはAC解析だけではなく、DC動作点解析や過渡解析も可能です(注:ADIsimPEでも同様なシミュレーションは可能です)。

パラメータスイープを実行した結果を図17に示します。1, 2, 3, 4, 5uHの5段階でシミュレーションしています。2nHでほぼフラットになります。

ということで、実際は2.2nHを使うことにしました。しかし、結論としてはこのとおりには上手くいかなかったのでした…。

アナログ・デバイセズのRAQに見るアナログスイッチの正しい使い方

アナログスイッチADG719の現品を入手でき、またVGA AD8369も含めて全体の回路を試作評価するための「パネルdeボード」の基板での検討開始予定のころは、だいぶ寒くなってきた季節でした(ブルブル!)。でもそのころ世間では、皆さんまだコートを着て無い人が多いものでした。私は寒がりなので、そんな時期でもコートなしでは寒くてダメです…。

さてここで小休止として、アナログ・デバイセズのRAQ (Rarely Asked Questions)「アナログ・デバイセズに寄せられた珍問/難問集」というコンテンツにある、アナログスイッチに関連する話題をご紹介します。

重要なディテールの分離(あるいは人魚と酢漬けのニシンの昼食)

その未使用ピンをどうにかしなさい!

アナログIC(1つめは特にADG719などマルチプレクサの話題)の未処理端子についてのお話です。よろしければ是非ご覧ください。

ちなみに図7の回路図では、マルチプレクサADG719の端子はアキ(4ピンや6ピンが未接続)のままでした。一方、図8では高抵抗で接続してあります。「コイツはこのRAQを見て慌てて接続したのだな」などと想いを巡らせぬよう、お願いしたいと思います(汗)。

実際の試作基板(パネルdeボード)で確認してみよう

その後、関係者のオフィスにお邪魔し、中間地点打ち合わせとして、かなり突っ込んだ話し合いをしてきました。終わったあとの雑談では、お仕事のようすとかを聞くことができましたが、技術開発に関わるご努力と情熱に頭の下がる思いでした。このような方々との交流は、技術者として、かけがえのない経験だと思いました。

いよいよ実際の回路で評価開始!

使用する部品はだいたい決まったので、パネルdeボードで試作用のボードの注文をしました。図18は入手した基板です。左奥の彼方には、秋月電子で購入した図5の16ポジションのロータリ・スイッチが見えます。

TSSOPとTSOT用の実装パネルを組み合わせて、こんな感じでできあがります。セールストークではなく、自分で使っても「まさしく選んで繋いで注文するだけ!」で超簡単だと感じます。

図19は一部を実装したようすです。この段階で、初段固定ATTとAD8369の動作確認まで完了できました。初段固定ATTは設計を完全に間違えており(汗)、コモンモードの減衰が全く出来ていませんでした(汗)。試作での確認は大事です…。

図20は全体を実装したようすです。同図の左側に見えるSMAコネクタが入力で、その上側にAD8369があります。その右側が、これまで詳しく説明してきたADG719の差動固定ATT回路です。減衰した信号が右側のSMAコネクタから出力として出てくるようになっています。

前編はここまで!

前編では、構想段階から、周波数特性の改善検討(と言っても、これが「休むに似たり」だったことを、次の後編でご説明していきますが)から、パネルdeボードでの試作基板を組み上げたあたりまで説明しました。

後編では、パネルdeボードの試作基板の特性、最終形となる基板のCAD設計と評価、そして特性の最適化などの話題をご説明していきます。

著者について

1963年千葉県生まれ。1985年第1級無線技術士合格。1986年東京農工大学電気工学科卒業、同年電子機器メーカ入社、長く電子回路設計業務に従事。1994年技術士(電気・電子部門)合格。2002年横浜国立大学大学院博士課程後期(電子情報工学専攻・社会人特別選抜)修了。博士(工学)。2009年アナログ・デバイセズ株式会社入社、現在に至る。2018年中小企業診断士登録。

デジタル回路(FPGAやASIC)からアナログ、高周波回路まで多...

デジタル回路(FPGAやASIC)からアナログ、高周波回路まで多...