概要

設計リソース

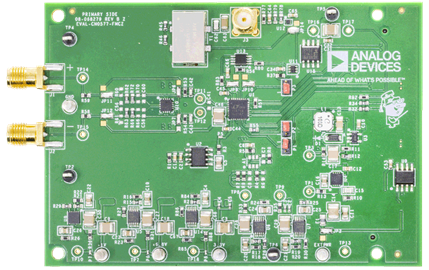

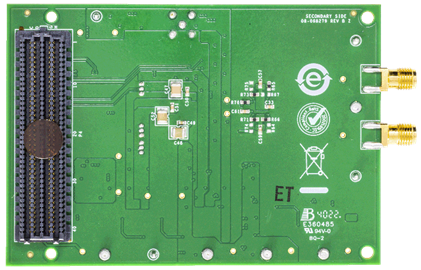

評価用ボード

型番に"Z"が付いているものは、RoHS対応製品です。 本回路の評価には以下の評価用ボードが必要です。

- EVAL-CN0577-FMCZ ($287.50) 18-bit, 15 MSPS, 2 ppm linear Data Acquisition Card

デバイス・ドライバ

コンポーネントのデジタル・インターフェースとを介して通信するために使用されるCコードやFPGAコードなどのソフトウェアです。

FPGA/HDL

機能と利点

- 18ビット分解能、15MSPSデータ・アクイジション・システム

- 任意の電圧入力をサポート

- クロッキングと電源に必要な全ての機能がオンボード

- FPGAインターフェース用FMCコネクタ

参考資料

-

CN0577 User Guide2023/01/25WIKI

-

ラピッド・プロトタイピングを実現するためのソリューション2024/04/15PDF4 M

-

CN0577: シリアル LVDS SAR ADC 用のアナログ・フロント・エンドおよびデジタル・インターフェース (Rev. 0)2023/01/25PDF1 M

回路機能とその特長

フロー・サイトメトリ、光パルス測定、高速制御ループ、高速デジタル歪み補正、イメージ・センサー・デジタイゼーションなどの計測アプリケーションには、それぞれ独自のデータ・アクイジション上の問題があります。このようなアプリケーションでは、多くの場合、高サンプリング・レート、高直線性、低ドリフト、低ノイズ、低遅延を組み合わせることが要求されます。

従来の逐次比較レジスタ(SAR)A/Dコンバータ(ADC)ベースのデジタイザは、低ノイズ性能と低消費電源を提供しますが、サンプリング・レートは通常2MSPS以下です。もう1つの手段は、非常に高速なパイプラインADCを使用して、出力をダウン・サンプリングすることです。この方法は特定のアプリケーションでは有効ですが、パイプラインADCは一般にSAR ADCよりもノイズが多くてドリフトも大きく、さらにパイプライン遅延が数サンプルあります。

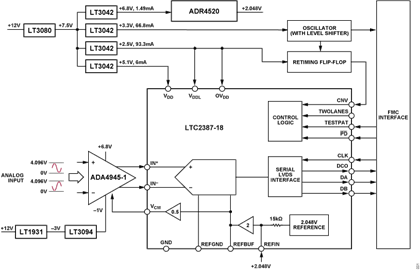

図1に示す回路は18ビット、15MSPS、2ppmのリニア・データ・アクイジション・システムで、入力インピーダンスが1.1kΩと駆動が容易です。アナログ入力範囲はピークtoピークが8.096Vで、シングルエンドまたは差動モードで駆動できるため、様々なアプリケーションに柔軟に対応できます。SN比(SNR)は90dB(代表値)以上、全高調波歪み(THD)は−110dBより良好です。

この回路は、フィールド・プログラマブル・ゲート・アレイ(FPGA)メザニン・カード(FMC)のフォーム・ファクタで、FMCコネクタまたは外部電源から12Vを供給します。デジタル・インターフェースは、シリアル低電圧差動信号(LVDS)を用いているため、入出力条件が最小限に抑えられ、FPGAとの統合が容易です。

独立したデータ・クロック出力により、ホストFPGAのタイミング条件が緩和されます。オンボードの120MHzクロックがFPGAに転送され、CONVERTリタイミング・フリップフロップがFPGAの変換信号からのジッタを低減します。

回路説明

アナログ・フロント・エンド

CN0577のアナログ・フロント・エンド(AFE)の最も重要な特徴は、ADCの厳しい駆動条件を満たしながら、任意の入力駆動方式(シングルエンド、差動、擬似差動)に容易に対応できることです。

LTC2387-18 SAR ADCは、コモンモード電圧がREFBUF電圧の半分に等しい完全差動アナログ入力を必要とし、これにより入力範囲も決まります。CN0577はREFBUF電圧を4.096Vに設定するため、入力範囲は±4.096V、必要なコモンモード電圧は2.048Vとなります。

ADA4945-1 は、LTC2387-18の駆動に最適な低ノイズ、低歪みの完全差動アンプ(FDA)です。オフセット電圧は10μV、ドリフトは100nV/°C、入力電圧ノイズは1.8nV/√Hz(通常消費電力モード、100kHz)です。

LTC2387-18は、入力コモンモード電圧を設定するためのVCM出力を備えています。これは、パッシブ・ネットワークを介するか完全差動アンプのVOCMピンを駆動して行います。VCM出力のインピーダンスは15Ωで、ADA4595-1のVOCMピンのインピーダンスである125kΩを直接駆動できます。

ADA4945-1の入出力ピンはDC結合されており、外付けのACカップリング・コンデンサを介して駆動されると、入力は0Vの差動電圧に自己バイアスされます。ADA4595-1は+6.8Vと−1Vの電源電圧を使用するため、入力範囲が最大化され、出力はADCのフルスケール入力範囲に対応できます。

図2に示すように、ADA4945-1のVOCMピンはLTC2387-18のVCMピンに接続すると、出力は完全差動となります。

入力レンジとコモンモード・レンジ

ADA4945-1はユニティ・ゲインの構成となっていて、LTC2387-18の入力範囲は±4.096Vで固定されているため、この電圧はアナログ・フロント・エンドの入力電圧範囲にもなっています。CN0577は差動、擬似差動、または任意の入力信号を受け付けることができます。

図3~図6に、CN0577の様々な構成における入力信号の能力を示します。

入力コモンモード電圧の限界値は、ADA4945-1の加算ノード(IN+、IN–)における許容コモンモード電圧範囲によって決まり、これは−VS~+VS−1.3Vと仕様規定されています。任意駆動の解析は容易ではないため、目的のアプリケーションでの最も厳しい条件をLTspice®シミュレーション・ソフトウェアを用いて検証する必要があります。

図7に示すLTspice®回路は、入力のコモンモード(VIN_CM)と差動モード(VIN_NORMAL)を独立に駆動できるように構成されており、任意信号を簡単にシミュレートできます。同様に、出力の差動成分(VOUT)とコモンモード成分(VOCM_VERIFY)も個別に検証できるため、不適切な動作を容易に検出できます。

図8は、入力のコモンモードと差動モード、また出力の信号を示しています。

図9は出力のコモンモード電圧を示しています。VCMHとVCMLはLTC2387-18の入力コモンモード電圧の上限と下限で、VOCM_VERIFYはこの間に収まっていなければなりません。

図9でVOCM_VERIFYがVCMHを超える領域があり、それが図8のVOUTのクリッピングと同じ時点に対応していることに注意してください。このシミュレーションは設計支援パッケージからアクセスできます。

入力インピーダンスの計算

有効入力インピーダンスは、信号源がシングルエンドか差動かによって異なります。図10に示すような平衡差動入力信号の場合、入力間(+DINと−DIN)の入力インピーダンスは、式1で表されます。

ここで、

RIN_DIFFは差動入力インピーダンス。

RGはゲイン抵抗。

図11に示すような不平衡シングルエンド入力信号の場合、入力インピーダンスは式2~式4を用いて計算できます。

ここで、

RIN_SEはシングルエンド入力信号に対するインピーダンス。

RG1とRG2はゲイン抵抗。

RF1とRF2は帰還抵抗。

β1とβ2は帰還係数。

出力フィルタ処理

ADA4945-1の出力とLTC2387-18の入力の間には、ADA4945-1のノイズ寄与を最小化し、ADCのサンプリングによる過渡変動から反射される妨害を低減するために、フィルタ・ネットワークを配置する必要があります。多くのアプリケーションでは、単純な1次のローパスRCフィルタで十分です。このフィルタのRC時定数は、アナログ入力がADCのアクイジション時間内にセトリングするのに十分小さいことが重要です。セトリングが不十分であれば、積分直線性(INL)と全高調波歪み(THD)の性能が制限される可能性があるためです。

フィルタ・コンデンサの選定は、容量が大きければノイズが小さくなり、容量が小さければフルスケール誤差が小さくなるというトレードオフを伴います。図12は、サンプリング・レートに基づき、出発点として考慮すべきコンデンサの容量値の範囲を示しています。

CN0577は82pFのコンデンサ(15MSPSでの最適値に近い)と24.9Ωの抵抗を用いて、カットオフ周波数を77.95MHzとしています。FDA(完全差動アンプ)の広帯域ノイズが1.8nV/√Hz、ADCのノイズ密度が17nV/√Hz、フル・パワー帯域幅が200MHzであることを考慮すると、フィルタが全体のノイズに与える影響は最小です。しかし、フィルタはADCのサンプリング・コンデンサ18pFからのサンプリング・グリッチを減衰できることにより、サンプル間のセトリングを完全に確保します。

アナログ・デジタル変換

LTC2387-18は、低ノイズ、高速、18ビット、15MSPSのSAR ADCです。このデバイスは、INLが2ppm、SN比が96dB、THDが−117dBという卓越した性能を備えています。ポスト・フィルタ処理を適用すると、164dBのダイナミック・レンジ(1Hz帯域幅に正規化)が得られます。

LTC2387-18は2つのフェーズで動作します。アクイジション・フェーズでは、サンプリング・コンデンサがアナログ入力ピンのIN+とIN–に接続され、差動アナログ入力電圧をサンプリングします。CNVピンの立上がりエッジで変換を開始します。変換フェーズでは、ADCは逐次比較アルゴリズムによりシーケンス動作し、差動コンパレータを用いて、サンプリングした入力をリファレンス電圧のバイナリ加重分数(例えば、VREFBUF/2、VREFBUF/4、 … 、VREFBUF/262144)と比較します。

ADCがフルスケールのアナログ入力電圧をデジタル化し、制御ロジックがシリアル転送用に18ビットのデジタル出力コードとして用意する結果、LSBサイズが31.25μV(REFBUF = 4.096V)となります。出力データは2の補数形式です。理想的な伝達関数を図13に示します。

アナログ入力は、図14に示す等価回路を用いてモデル化できます。入力にあるダイオードと10Ωの抵抗は、静電気放電(ESD)とオーバードライブから保護します。アクイジション・フェーズでは、各入力は、サンプリング・コンデンサによる約18pF(CSAMPLE)とサンプリング・スイッチのオン抵抗である28Ωを直列接続したものになります。CPARは、主にダイオード接合で形成される2pFオーダーの集中容量です。

電圧リファレンス

LTC2387-18は、0.25%の初期精度と±20ppm/°C(最大)の温度係数を確保した高精度2.048Vのリファレンスを内蔵しています。この2.048V、低ノイズ、低ドリフトのバンドギャップ・リファレンスは、2倍のゲインを持つ内部リファレンス・バッファを駆動し、REFBUFに4.096Vを生成します。REFBUF~REFGND間の電圧差によって、ADCのフルスケール入力範囲が決まります。

内部リファレンスは多くのアプリケーションにとって十分ですが、外部リファレンスを使用すると初期精度を向上させ、ドリフトを低下させることができます。CN0577は、超低ノイズ、高精度の2.048V電圧リファレンスであるADR4520を内蔵しています。このデバイスの初期精度は0.025%、ドリフトは2ppm/°Cです。ノイズは0.1Hz~10Hzで1μVp-p、出力ノイズ密度は1kHzで35.8nV/√Hzです。

REFBUFアンプは、ADCが示す平均負荷が0.5mA~1.6mAの高速トランジェントを駆動するように最適化されています。REFBUF電圧は内部で1/2に分圧され、入力信号のコモンモードを設定するのに使用されるバッファ付きのVCM信号を生成します。

デジタル・インターフェース

CN0577での変換はCNV+入力とCNV–入力によって制御され、これらはLVDS信号で直接駆動できます。また、CNV–をGNDに接続している場合は、0V~2.5VのCMOS信号でCNV+ピンを駆動することもできます。CNV+の立上がりエッジでアナログ入力をサンプリングし、変換を開始します。

CN0577への電源投入後、またはパワーダウン・モード終了後の最初の2サイクルの変換データは無効です。その後の変換結果は、変換間隔がLTC2387-18のデータシートに記載の仕様に適合している限り、正確です。サンプリング中、アナログ入力信号が完全にセトリングされていない場合、CN0577のノイズ性能はCNV+の立上がりエッジにおけるジッタの影響を受けます。このような場合は、クリーンで低ジッタの信号によってCNV+の立上がりエッジを駆動します。なお、CN0577はCNV+の立下がりエッジのジッタの影響を受けにくくなっています。ジッタの影響を受けにくいアプリケーションでは、CNVをFPGAから直接駆動できます。

CN0577は、最大変換時間が63nsになるように調整された内部クロックを備えています。代表的なアクイジション時間は27.7nsで、15MSPSのスループット性能を実現します。

またCN0577は、1レーンまたは2レーン出力モードの高速LVDSデジタル・インターフェースを備えており、アプリケーションごとにインターフェースのデータ・レートを最適化できます。LVDSには、CLK±、DCO±、DA±の3ペアが必要です。4番目のLVDSペアであるDB±はオプションです(図15参照)。

変換はCNV+の立上がりエッジで開始します。変換が完了すると、最上位データ・ビットがDA±に出力されます。その後、CLK±入力に9クロック・パルスのバーストを印加することにより、データがシフト・アウトされます。DA±上のデータは、CLK±のエッジ毎に更新されます。CLK±のエコーがDCO±に出力されます。DA±とDCO±のエッジはアライメントされているので、FPGAでDA±をラッチするのにDCO±を使用できます。単一変換のタイミングを図16に示します。

現在の変換が完了した後、次の変換が終了する前にデータはクロック・アウトされる必要があります。データのクロック・アウトが可能な有効時間のウィンドウを図17に示します。次の変換が開始されても、データは引き続きクロック・アウトできることに注意してください。

高いサンプリング・レートでは、必要なLVDSインターフェースのデータ・レートが400Mbpsを超えることがあり、タイミング制約が複雑になります。2レーン出力モードでは、必要なクロック周波数が半分になります。2レーン入力ピンをハイに接続すると、オプションのLVDS出力DB±がイネーブルになり、データは一度に2ビットずつDA±とDB±から出力されます。DB±出力をイネーブルにすると、OVDDからの電源電流が約3.6mA増加します。2レーン・モードでは、CLK±に5クロック・パルスが必要です(図18参照)。

クロック・アーキテクチャ

CN0577のクロック・ツリーを図19に示します。オンボードの120MHz電圧制御水晶発振器は、CN0577とFPGAのクロック供給に使用されます。この超低ノイズ発振器は、10kHzオフセットでの位相ノイズが−162dBc/Hz(代表値)、チューニング電圧範囲が0V~3.3V、周波数プリング範囲が28ppm~55ppmです。さらにこの水晶発振器のRMSジッタは、100MHzキャリアで50fs~100fsです。

クロックは再タイミング・フリップフロップとFPGAに送られます。ADG3241 レベル・シフタは、クロックの3.3Vロジック・レベルを再タイミング・フリップフロップが必要とする2.5Vレベルに変換します。ADN4661は、3.3VクロックをLVDS信号に変換し、この信号はFMCコネクタのグローバル・クロック接続に送られます。

外部クロック

CN0577を他の回路に同期させる場合、またはより厳しい周波数精度や周波数ドリフト性能が必要な場合は、外部クロックを外部クロック・コネクタに印加できます。外部クロックの周波数がオンボードの120MHzクロックより大幅に高いか低い場合は、FPGAのタイミング制約を含めて回路全体を見直します。

外部クロック回路には、ACカップリングを備え、立上がり時間と立下がり時間のバランスを調整するための単一の高速インバータも含まれています。このデバイスの伝搬遅延時間は2.4ns(代表値)で、高い出力ドライブ能力がありながら、広いVCCの動作範囲で自己消費電力を低く維持します。

再タイミング・フリップフロップ

FPGAはリファレンス・クロックにジッタを付加します。多くの場合、付加されるジッタの量は仕様化されていないか未知であり、SN比を大幅に低下させる可能性があります。CN0577は立上がりエッジ・トリガのD型フリップフロップを内蔵しており、低ジッタで再タイミングされたCNVエッジをLTC2387-18に供給します。

このデバイスは、1.65V~5.5V VCCの電源電圧で動作し、最小セットアップ時間は1.7ns、最小ホールド時間は0.3nsです。

変換を開始するには、FPGAがフリップフロップのCLRピンにハイ・レベルを供給します。この信号の立上がりエッジには大きなジッタがある可能性があります。リファレンス・クロックの次の立上がりエッジで、フリップフロップのD入力からQ出力にロジック・ハイが伝搬され、低ジッタのCNVエッジがLTC2387-18に供給されます。

パワー・ツリー

CN0577は、FMCコネクタのFPGA側の12V電源ピンから電源が供給されます。パワー・ツリーは、システム・レベルの電源アーキテクチャ設計ツールであるLTpowerPlanner™を用いて設計されました。図20に、このボードの詳細な電源アーキテクチャを示します。

このボードの12V電源は、まずレギュレータの前段にあるLT3080(単一抵抗で調整可能な1.1Aの低ドロップアウト(LDO)レギュレータ)によって電圧を低下させます。このステージでは、12V電源を7.5Vに低下させ、ボード全体に発熱を分散させます。この電圧は4つのLT3042 LDOに供給され、6.8V、5.1V、3.3V、2.5Vの各レールを生成します。

LT1931(1.2MHzの反転DC-DCコンバータ)は−3Vレールを生成し、それがLT3094 (低ドロップアウト負レギュレータ)に供給され、−1Vレールを生成します。

ボードの総消費電力は、15MSPSで約2.25Wです。

レイアウト時の考慮事項

プリント基板(PCB)のレイアウトは、シグナル・インテグリティを維持し、最適な性能を実現するために非常に重要です。LTC2387-18の下の内層1層目には、クリーンなグランド・プレーンを配置した多層基板を使用することを推奨します。基板上の個々の部品と様々な信号の配線も注意深く配置する必要があります。さらに、入力信号と出力信号を対称に配線することを推奨します。

ADCのグラウンド・ピンは、複数のビアを用いてPCBのグランド・プレーンに直接はんだ付けしなければなりません。さらに、ADCの入力ピンと出力ピン下のグランド・プレーンとパワー・プレーンは、望ましくない寄生容量を避けるために取り除く必要があります。望ましくない寄生容量は、基板における歪みと直線性の性能に影響を与える可能性があります。敏感なアナログ部とデジタル部は基板上で分離し、電源回路はアナログ信号経路から遠ざけます。

CNV±やCLK±のような高速スイッチング信号、およびデジタル出力DA±とDB±は、ADCへのノイズ結合を防ぐために、アナログ信号経路の近くを走らせたり、アナログ信号経路を横切らないようにする必要があります。

LVDS信号は基板上で100Ωの差動伝送ラインとして配線し、レシーバーでは100 Ωの抵抗で終端する必要があります。同様に、この基板で使用されている完全差動アンプと電圧リファレンスは、寄生的影響を避けるために出力パターンの長さを最小にする必要があります。相補信号のレイアウトを対称的にすることで、これらのデバイスの性能を最大化し、バランスのとれた性能が得られます。

また、デバイスの電源電圧変動除去比(PSRR)を維持するために、基板上に搭載されているLT3042およびLT3094 LDOの出力に、少なくとも4.7μFの高品質セラミック・バイパス・コンデンサを追加する必要があります。

図21は、LTC2387-18とADA4945-1の近くに配置したCN0577の基板レイアウトを示しています。

バリエーション回路

The LTC2387-16 は低ノイズ、高速、16ビット15MSPSのSAR ADCで、LTC2387 SARファミリとピン互換性があります。目的のアプリケーションが16ビット分解能しか必要としない場合、このリファレンス・デザインのLTC2387-18 ADCの代わりに使用できます。

ADAQ23878 は、LTC2387-18およびADA4945-1と同等の機能を提供するμModule®データ・アクイジション・ソリューションです。デジタル・インターフェースも互換性があります。

より高い精度やより低いドリフト性能が必要な場合は、REFINを外部2.048Vリファレンスで直接オーバードライブできます。LTC6655 (2.048V)は、内部リファレンスをオーバードライブする場合にLTC2387-18と共に使用するのに適しています。LTC6655の初期精度は0.025%(最大)、温度係数は2ppm/°C(最大)で、高精度アプリケーション向けとなっています。REFINピンの近くに2.7μF~10μFのセラミック・コンデンサでLTC6655をバイパスすることを推奨します。

回路の評価とテスト

このセクションでは、EVALCN0577-FMCZを評価するための一般的なセットアップの概要を説明します。ハードウェアとソフトウェアのセットアップの完全な手順については、CN0577ユーザ・ガイドを参照してください。

必要な機器

- EVAL-CN0577-FMCZ

- ZedBoard(AES-Z7EV-7Z020-G)

- 12V電源

- ホストPC

- MicroSDカード(16GB以上)

- アナログ・デバイセズKuiper Linuxイメージ

- LANケーブル

- SMAケーブル

- XLR-SMAアダプタ・ケーブル

- オーディオ・アナライザ(Audio Precision© APX525)

- 高精度直流電源/キャリブレータ(Krohn-Hite 523または同等品)

開始にあたって

以下の手順を実行して、評価用の設計をセットアップします。

- PC、Mac、またはLinuxのホストにIIOオシロスコープ・アプリケーションをダウンロードしてインストールします。

- アナログ・デバイセズのKuiper LinuxイメージをmicroSDカードに書き込みます。

- microSDカードをEVAL-CN0577-FMCZ用に設定します。

- microSDカードをZedBoardに挿入します。

- EVAL-CN0577-FMCZをFMCピン・コネクタを介してZedBoardに接続します。

- ZedBoardに12V電源ジャックを接続します。

- ZedBoardからホスト・コンピュータにLANケーブルを接続します。

- XLR-SMAアダプタ・ケーブルを用いて、EVAL-CN0577-FMCZをオーディオ・アナライザに接続します。

- EVAL-CN0577-FMCZのグラウンドをオーディオ・アナライザに接続します。

- オーディオ・アナライザのUSBケーブルをPCに接続します。

- IIOオシロスコープ・ソフトウェアを実行し、その結果のADCデータとFFTデータをキャプチャします。

テスト結果

定格スループットでのADCの周波数応答、歪み、ノイズをテストするのに高速フーリエ変換(FFT)技術を使用します。歪みの少ないサイン波を印加し、FFTアルゴリズムを用いてデジタル出力を分析することにより、ADCのスペクトル成分を基本波以外の周波数について調べることができます。LTC2387-18は、AC歪み測定とノイズ測定の両方のテストにより限界値が確保されています。図22に、CN0577のFFT性能を示します。

図23は、SN比、THD、SFDRをテストするための、EVAL-CN0577-FMCZとオーディオ・アナライザの適切な接続を示しています。

コモンモード電圧が2.048V、ADCサンプリング・レートが15MSPSで、40kHzの差動入力信号を4.096Vp-pの振幅で与えた場合、測定された最小の平均SN比は82.6dB、THDは−84dBです。図24は、異なるサンプリング・レートおよび周波数の入力信号におけるCN0577の代表的な性能を示しています。

図25は、ノイズをテストするための、EVAL-CN0577-FMCZと高精度DC電源の適切な接続を示しています。

図26は、CN0577の代表的なDCヒストグラムを示しており、REFINは2.048V、サンプル周波数は15MSPSとしています。

図27は、5MSPSと15MSPSの2つの異なるサンプリング・レートにおける、理想電圧とそれに対応する電圧入力の間の誤差を示しています。