概要

設計リソース

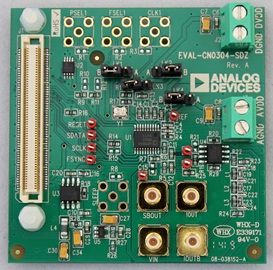

評価用ボード

型番に"Z"が付いているものは、RoHS対応製品です。 本回路の評価には以下の評価用ボードが必要です。

- EVAL-CN0304-SDZ ($106.93) Low Power DDS Waveform Generator

- EVAL-SDP-CB1Z ($134.00) Eval Control Board

デバイス・ドライバ

コンポーネントのデジタル・インターフェースとを介して通信するために使用されるCコードやFPGAコードなどのソフトウェアです。

AD9834 - Microcontroller No-OS Driver

AD983x GitHub no-OS Driver Source Code

AD9834 IIO Direct Digital Synthesis GitHub Linux Driver Source Code

機能と利点

- 75MHzの低消費電力DDS

- 最大18MHzの出力周波数

- 7次エリプティック・フィルタ

製品カテゴリ

マーケット & テクノロジー

使用されている製品

参考資料

-

CN-0304: 低消費電力DDS波形発生器2017/02/22PDF306 K

回路機能とその特長

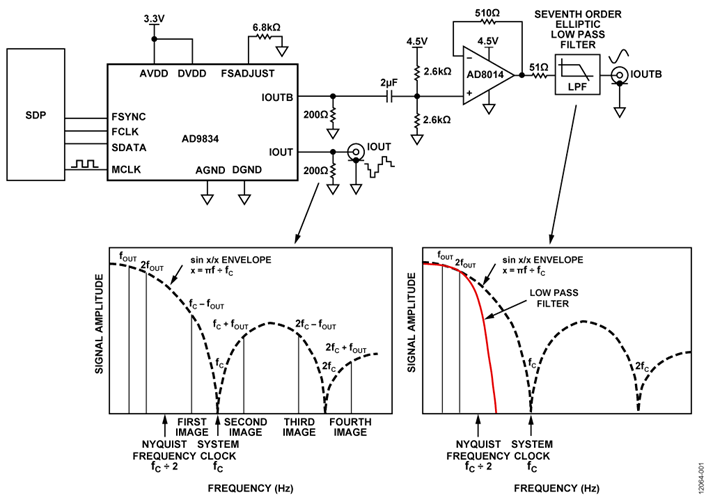

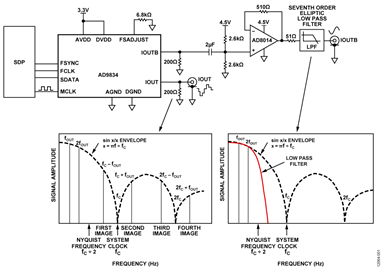

図1に示す回路は、75MHzの低消費電力(合計25mW)ダイレクト・デジタル・シンセシス(DDS)波形発生器です。出力バッファとアンチイメージング・フィルタによってスペクトル性能が改善されるので、最大18MHzのサイン波、三角波、方形波の出力を必要とする周波数発生やクロック駆動のアプリケーションに適しています。

低消費電力のDDSデバイスはサンプリング処理したデータを扱うデバイスなので、後段に適切なアンチイメージング・フィルタを接続してスペクトル・イメージを除去する必要があります。しかし、推奨する200Ω負荷には最大約4mAの出力電流が流れるため、DDS出力にバッファとして最適な低消費電力で低歪みのオペアンプを接続することにより、高品質の50Ωフィルタに対する低インピーダンス駆動源を実現します。

DDS、出力バッファ、7次エリプティック・ローパス・フィルタの組合わせにより、高品質のスペクトル性能を実現します。

(簡略回路図:全接続の一部およびデカップリングは省略されています。)

回路説明

AD9834は、75MHzの全機能を内蔵した低消費電力(20mW)DDSです。このデバイスは、最大37.5MHzの出力周波数で最大4mAの真および相補電流を出力するように設計されています。

AD8014は、−3dB帯域幅が400MHz、スルーレート4000V/µs、セトリング・タイムが24nsの高速電流帰還アンプです。これは低歪みであるうえ、電圧ノイズと電流ノイズが非常に小さいデバイスです。AD8014は低消費電力(+4.5V時に5.2mW)、低価格で30mAの電流駆動能力があるので、AD9834の出力のバッファとして最適です。回路はAD9834が+3.3Vで、AD8014が+4.5Vで動作します。DDSはSPIインターフェースを使って動作します。この回路はDDSブロック、バッファ・ブロック、ローパス・フィルタ・ブロックの3つのブロックで構成され、回路の総消費電力は約25mWです。

DDSの電圧出力

フルスケール調整(FSADJUST)電圧と外付け抵抗RSETにより、フルスケールDAC電流の大きさが決まります。FSADJUST電圧の公称値は1.15V、RSET抵抗の代表値は6.8kΩです。

AD9834のフルスケール電流は次のとおりです。

この回路は、200 Ωの規定負荷と最大フルスケール電流を使用し、DACのコンプライアンス電圧範囲を超えない電圧出力を実現します。

VOUT = 3 mA × 200 Ω = 0.6 V

ボードには2つの電流出力IOUTとIOUTBがあります。IOUTはフィルタを通していない出力で、IOUTBはフィルタを通した出力です。

バッファ・アンプ

DDSの出力では電流とコンプライアンス電圧範囲が制限されているので、ローパス・フィルタがより大きな駆動能力を得るためにバッファが必要になります。さらに、バッファはDDSブロックとフィルタ・ブロックを分離し、負荷が付いたDDSの出力インピーダンス200Ωを終端されたフィルタを駆動するのに必要な値50Ωに変換します。この回路ノートでは、AD9834の出力バッファとして低消費電力の高性能電流帰還型オペアンプAD8014を使用します。AD8014は、−3dB帯域幅が400MHz、スルーレート4000V/µs、セトリング・タイム24nsの高速電流帰還アンプで、30mA以上の出力電流を駆動します。電流帰還型オペアンプAD8014の帰還抵抗によってオペアンプの帯域幅を設定します。

図2に510 Ωの帰還抵抗を示します。このオペアンプは単極性の電源で動作するので、クリッピングを防ぐために出力の中心を電源電圧の中点にする必要があります。分圧器のポイントAは正弦波信号に対する2.25VのDCオフセットを提供し、2.25V ± 0.3Vの出力振幅を与えます。単電源アプリケーションでのオペアンプの適切なバイアス方法については、アプリケーション・ノート「AN-581 Biasing and Decoupling Op Amps in Single Supply Applications」を参照してください。電流帰還アンプの詳細については、チュートリアル「MT-034 Current Feedback (CFB) Op Amps」を参照してください。

7次エリプティック・ローパス・フィルタ

図1に示されているように、アンチイメージングによる再構成ではサンプリング・システムに固有のイメージ周波数を減衰させる必要があります。

再構成フィルタとして、カウアー(エリプティック)、チェビシェフ、バターワース、ベッセルの4種類の基本的なフィルタを使用することができます。これら4種類の基本的なフィルタの応答曲線を図3に示します。

同じ次数では、エリプティック・フィルタのロールオフ・レートが他の3つに比べて大きいので、再構成フィルタに最適です。この回路ノートでは、−3dB帯域幅が18MHzの7次エリプティック・フィルタを使用しました。

部品の選択

フィルタを実現するのに使用される抵抗、コンデンサ、インダクタは受動部品であり、高い周波数を扱うため、以下の条件を満たす必要があります。

- 寄生容量と寄生インダクタンスが小さいこと。

- 応答の実測値が設計値に近くなるように許容誤差が小さいこと。

- 温度範囲が広いこと。

- 寄生容量と寄生インダクタンスを最小限に抑えるために小型であること。

これらは、フィルタ応答の実測値をフィルタ応答のシミュレーション値に近づけるための条件の一部にすぎません。

さまざまなアプリケーションに対する受動部品の選択の詳細については、「Basic Linear Design: Chapter 10, Passive Components」を参照してください。

フィルタの設計と性能

7次エリプティック・フィルタを図4に、フィルタの周波数応答のシミュレーション値と実測値を図5に示します。使用したソフトウェアはAdvanced Design System(ADS)のバージョン2012.08です。実際のフィルタ部品とメーカーについては、CN0304設計サポート・パッケージ(https://www.analog.com/CN0304-DesignSupport)の部品表を参照してください。

フィルタ応答はAgilent E5061Bネットワーク・アナライザを使って測定しました。−3dB帯域幅は18MHzです。信号源と負荷終端による通過帯域の減衰量は約6dBです。

回路の性能をチェックするため、AD9834を15MHzの出力周波数に設定し、75MSPSのクロックでDDS出力のスペクトルを測定しました。フィルタを通していない出力とフィルタを通した出力をそれぞれ図6と図7に示します。

図6のフィルタを通していないスペクトルに生じる不要なイメージが、図7では大幅に低減されています。60MHzでの最も大きなイメージ・スプリアスは、フィルタを通していない出力に比べて約52dB抑制されています。これは、60MHzでのフィルタの減衰量の実測値に相当します。

AD9834の600mVp-pの出力はフィルタによって約6dB減衰し、sin x/xのロールオフによってさらに1dB減衰します。このため、50Ω負荷への出力は約268mVp-p(94.7mVrms)になります。これは0.179mW(−7.5dBm)に相当します。

DDSに対するの再構成フィルタ設計の詳細については、アプリケーション・ノート「AN-837 DDS-Based Clock Jitter Performance vs. DAC Reconstruction Filter Performance」を参照してください。

この回路は、大きな面積のグランド・プレーンを持つ多層PCボード上に構築する必要があります。最大限の性能を得るためには正しいレイアウト、グラウンディング、デカップリング技術が必要です。(チュートリアル「MT-031 データコンバータのグランディングとAGND/DGNDの不可解さの解決」と、チュートリアル 「MT-101 デカップリング技術」を参照してください。)

回路図、レイアウト、部品表などが完備された設計サポート・パッケージについては、https://www.analog.com/CN0304-DesignSupportを参照ください。

バリエーション回路

DDSの代替デバイスはAD9838です。AD9838はより低消費電力(11mW)でAD9834と同じ機能を持ちますが、16MHzの低いクロック・レートで動作します。

この回路ノートで使用したバッファは電流帰還アンプAD8014です。この代替デバイスはADA4860-1です。 ADA4860-1は低価格、高速(−3dB帯域幅が800MHz)、低消費電力(5V時に22.5mW)の電流帰還型オペアンプですが、790V/µsの低いスルーレートで動作します。

バッファには電圧帰還(VFB)アンプを使用することもできます。VFBアンプの利点はノイズが小さく、帰還部品の選択の自由度が大きくなることです。AD8057は、帯域幅とスルーレートが一般的な電流帰還アンプと同じ値の電圧帰還アンプです。AD8057は、−3dB帯域幅が325MHz、28MHzまでのゲイン平坦度が0.1dB、スルーレートが1000V/µsのデバイスです。

もう1つの代替デバイスはADA4897-1です。ADA4897-1はユニティ・ゲインで安定動作をし、広帯域ノイズが小さく、レールtoレール出力の高速電圧帰還アンプであり、10Hzでの入力電圧ノイズが2.4 nV/√Hz、2MHzでのスプリアスフリー・ダイナミック・レンジ(SFDR)が−80dBcのデバイスです。

バッファとしてADA4851-1を使用することもできます。ADA4851-1は低価格、低消費電力、高速(−3dB帯域幅が130MHz)のデバイスですが、スルーレートは375V/µsとさらに低いい値です。

回路の評価とテスト

必要な装置

- EVAL-CN0304-SDZ評価ボード

- EVAL-SDP-CB1Z評価ボード

- AD9834評価用ソフトウェア

- Agilent E3631Aトリプル出力DC電源または相当品

- Rohde and Schwarz FSUP50信号源アナライザ

- Agilent E5061Bネットワーク・アナライザ(フィルタ応答の評価にのみ必要)

フィルタ応答の測定

フィルタの周波数応答は図8に示すセットアップを使ったネットワーク・アナライザで測定しました。

出力波形の測定

EVAL-CN0304-SDZボードを改造し、ネットワーク・アナライザからの信号をフィルタに入力しました。フィルタの出力はアナライザのもう1つのポートに接続しました。

EVAL-CN0304-SDZの5V電源はSDPカードからの5V USB電圧から供給します。ジャンパのLK1をBの位置、LK2をBの位置にし、LK3を取り外します。

AD9834の評価用ソフトウェア(ftp://ftp.analog.com/pub/evalcd/AD9834/)を使って、DDSの出力周波数と振幅を設定しました。詳細については、AD9834評価用ボードのユーザー・ガイドUG-266を参照してください。UG-266に記載されているハードウェアには7次出力フィルタはありませんが、グラフィカル・ユーザー・インターフェースとソフトウェアの操作はEVAL-CN0304-SDZのハードウェアと同一です。

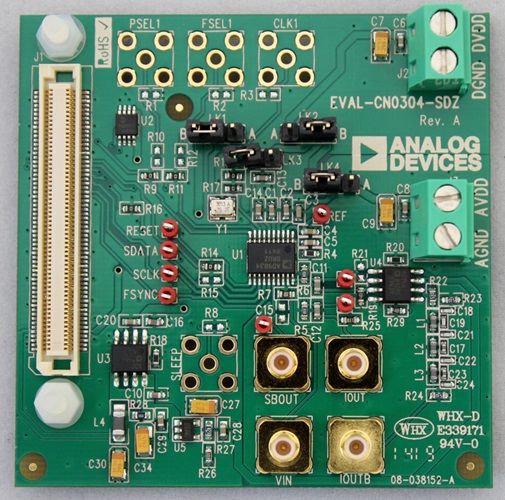

CN0304のプリント回路ボードの写真を図10に示します。