Circuits from the Lab®実用回路デザインは今日のアナログ・ミックスド・シグナル、RF回路の設計上の課題の解決に役立つ迅速で容易なシステム統合を行うために作製、テストされました。詳しい情報と支援については [www.analog.com/jp/CN0304](http://www.analog.com/jp/CN0304) をご覧ください。

**使用したリファレンス・デバイス**

|        |                        |

|--------|------------------------|

| AD9834 | 75 MHz コンプリート低消費電力 DDS |

| AD8014 | 400 MHz 低消費電力高性能アンプ    |

## 低消費電力 DDS 波形発生器

### 評価および設計サポート環境

#### 回路評価ボード

CN0304 回路評価ボード (EVAL-CN0304-SDZ)

SDP-B 評価ボード (EVAL-SDP-CB1Z)

#### 設計と統合ファイル

回路図、レイアウト・ファイル、部品表

### 回路の機能とその利点

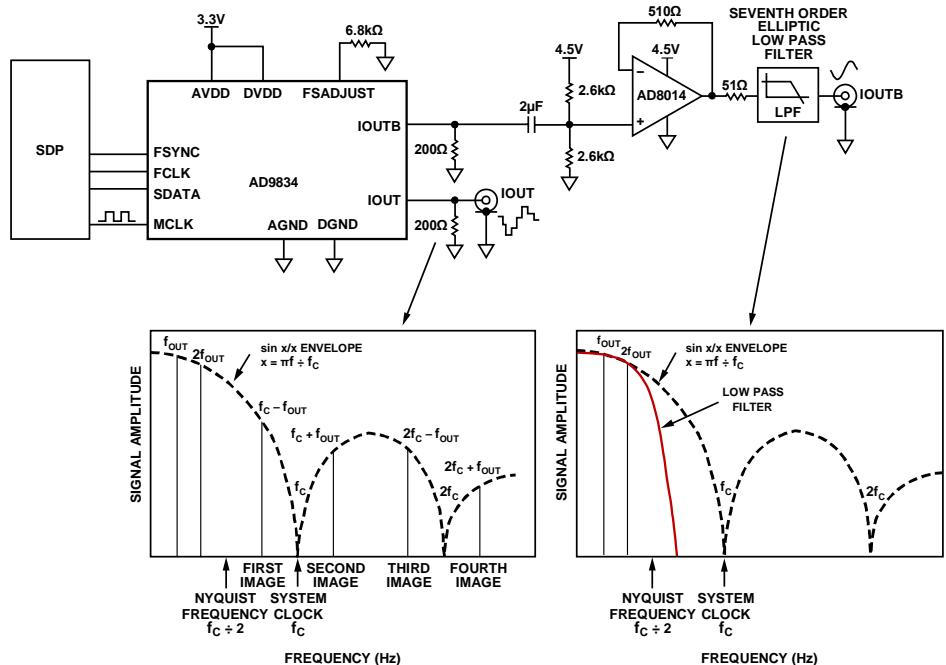

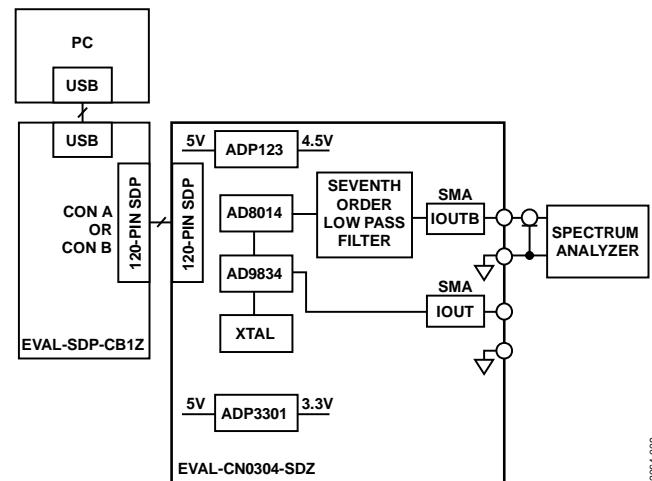

図 1 に示す回路は、75MHz の低消費電力 (合計 25mW) ダイレクト・デジタル・シンセシス (DDS) 波形発生器です。出力バッファとアンチイミーディング・フィルタによってスペクトル性能が改善されるので、最大 18MHz の

サイン波、三角波、方形波の出力を必要とする周波数発生やクロック駆動のアプリケーションに適しています。

低消費電力の DDS デバイスはサンプリング処理したデータを扱うデバイスなので、後段に適切なアンチイミーディング・フィルタを接続してスペクトル・イメージを除去する必要があります。しかし、推奨する 200Ω 負荷には最大約 4mA の出力電流が流れるため、DDS 出力にバッファとして最適な低消費電力で低歪みのオペアンプを接続することにより、高品質の 50Ω フィルタに対する低インピーダンス駆動源を実現します。

DDS、出力バッファ、7 次エリプティック・ローパス・フィルタの組合せにより、高品質のスペクトル性能を実現します。

図 1. 低消費電力波形発生器 (簡略回路図 : 全接続の一部およびデカップリングは省略されています。)

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものではありません。仕様は、予告なく変更される場合があります。本誌記載の商標および登録商標は、それぞれの所有者の財産です。※日本語資料は REVISION が古い場合があります。最新の内容については、英語版をご参照ください。

©2014 Analog Devices, Inc. All rights reserved.

## 回路説明

AD9834 は、75MHz の全機能を内蔵した低消費電力 (20mW) DDS です。このデバイスは、最大 37.5MHz の出力周波数で最大 4mA の真および相補電流を出力するよう設計されています。

AD8014 は、-3dB 帯域幅が 400MHz、スルーレート 4000V/μs、セトリング・タイムが 24ns の高速電流帰還アンプです。これは低歪みであるうえ、電圧ノイズと電流ノイズが非常に小さいデバイスです。AD8014 は低消費電力 (+4.5V 時に 5.2mW)、低価格で 30mA の電流駆動能力があるので、AD9834 の出力のバッファとして最適です。回路は AD9834 が +3.3V で、AD8014 が +4.5V で動作します。DDS は SPI インターフェースを使って動作します。この回路は DDS ブロック、バッファ・ブロック、ローパス・フィルタ・ブロックの 3 つのブロックで構成され、回路の総消費電力は約 25mW です。

## DDS の電圧出力

フルスケール調整 (FSADJUST) 電圧と外付け抵抗  $R_{SET}$  により、フルスケール DAC 電流の大きさが決まります。FSADJUST 電圧の公称値は 1.15V、 $R_{SET}$  抵抗の代表値は 6.8kΩ です。

AD9834 のフルスケール電流は次のとおりです。

$$I_{FULLSCALE} = 18 \times (FSADJUST/R_{SET})$$

この回路は、200 Ω の規定負荷と最大フルスケール電流を使用し、DAC のコンプライアンス電圧範囲を超えない電圧出力を実現します。

$$I_{FULLSCALE} = 18 \times (1.15/6800 \Omega) = 3 \text{ mA},$$

$$V_{OUT} = 3 \text{ mA} \times 200 \Omega = 0.6 \text{ V}$$

ボードには 2 つの電流出力 IOUT と IOUTB があります。IOUT はフィルタを通していない出力で、IOUTB はフィルタを通した出力です。

## バッファ・アンプ

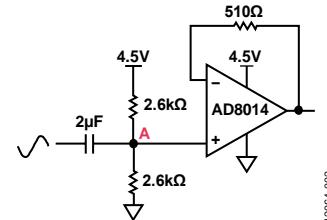

DDS の出力では電流とコンプライアンス電圧範囲が制限されているので、ローパス・フィルタがより大きな駆動能力を得るためにバッファが必要になります。さらに、バッファは DDS ブロックとフィルタ・ブロックを分離し、負荷が付いた DDS の出力インピーダンス 200Ω を終端されたフィルタを駆動するのに必要な値 50Ω に変換します。この回路ノートでは、AD9834 の出力バッファとして低消費電力の高性能電流帰還型オペアンプ AD8014 を使用します。AD8014 は、-3dB 帯域幅が 400MHz、スルーレート 4000V/μs、セトリング・タイム 24ns の高速電流帰還アンプで、30mA 以上の出力電流を駆動します。電流帰還型オペアンプ AD8014 の帰還抵抗によってオペアンプの帯域幅を設定します。

図 2 に 510 Ω の帰還抵抗を示します。このオペアンプは単極性の電源で動作するので、クリッピングを防ぐために出力の中心を電源電圧の中点にする必要があります。分圧器のポイント A は正弦波信号に対する 2.25V の DC オフセットを提供し、2.25V ± 0.3V の出力振幅を与えます。単電源アプリケーションでのオペアンプの適切なバイアス方法については、[アプリケーション・ノート AN-](#)

581 「*Biassing and Decoupling Op Amps in Single Supply Applications*」を参照してください。電流帰還アンプの詳細については、チュートリアル MT-034 「*Current Feedback (CFB) Op Amps*」を参照してください。

図 2. AD8014 の入力と帰還抵抗の接続

## 7 次エリプティック・ローパス・フィルタ

図 1 に示されているように、アンチイメージングによる再構成ではサンプリング・システムに固有のイメージ周波数を減衰させる必要があります。

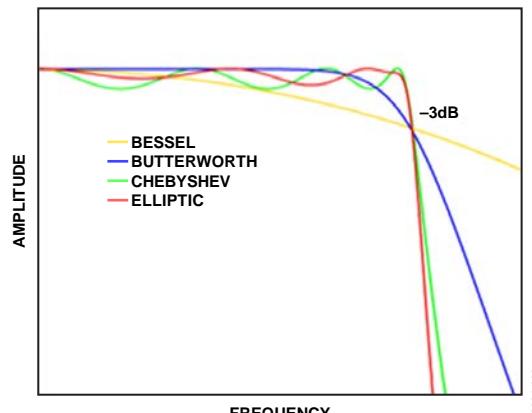

再構成フィルタとして、カウアー (エリプティック)、チェビシェフ、バターワース、ベッセルの 4 種類の基本的なフィルタを使用することができます。これら 4 種類の基本的なフィルタの応答曲線を図 3 に示します。

図 3. 4 種類の基本的なフィルタの応答曲線

同じ次数では、エリプティック・フィルタのロールオフ・レートが他の 3 つに比べて大きいので、再構成フィルタに最適です。この回路ノートでは、-3dB 帯域幅が 18MHz の 7 次エリプティック・フィルタを使用しました。

## 部品の選択

フィルタを実現するのに使用される抵抗、コンデンサ、インダクタは受動部品であり、高い周波数を扱うため、以下の条件を満たす必要があります。

- 寄生容量と寄生インダクタンスが小さいこと。

- 応答の実測値が設計値に近くなるように許容誤差が小さいこと。

- 温度範囲が広いこと。

- 寄生容量と寄生インダクタンスを最小限に抑えるために小型であること。

これらは、フィルタ応答の実測値をフィルタ応答のシミュレーション値に近づけるための条件の一部にすぎません。

さまざまなアプリケーションに対する受動部品の選択の詳細については、「[Basic Linear Design: Chapter 10, Passive Components](#)」を参照してください。

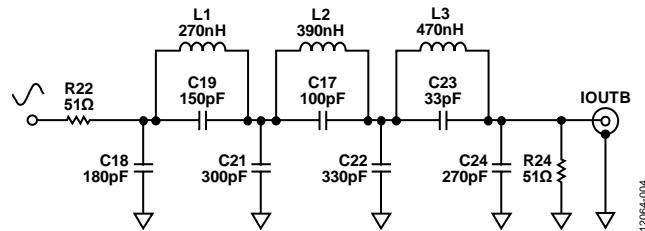

## フィルタの設計と性能

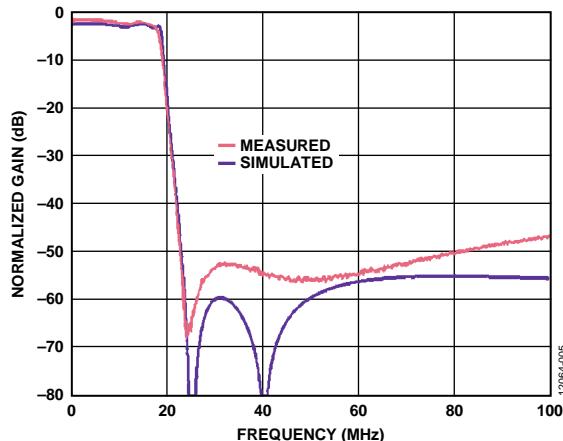

7次エリプティック・フィルタを図4に、フィルタの周波数応答のシミュレーション値と実測値を図5に示します。使用したソフトウェアはAdvanced Design System (ADS) のバージョン2012.08です。実際のフィルタ部品とメーカーについては、CN0304設計サポート・パッケージ (<http://www.analog.com/CN0304-DesignSupport>) の部品表を参照してください。

図4. 7次、シャント接続ローパス・フィルタ

図5. 7次エリプティック・フィルタの周波数応答の実測値 対 ミュレーション値

フィルタ応答はAgilent E5061Bネットワーク・アナライザを使って測定しました。 $-3\text{dB}$  帯域幅は18MHzです。信号源と負荷終端による通過帯域の減衰量は約6dBです。

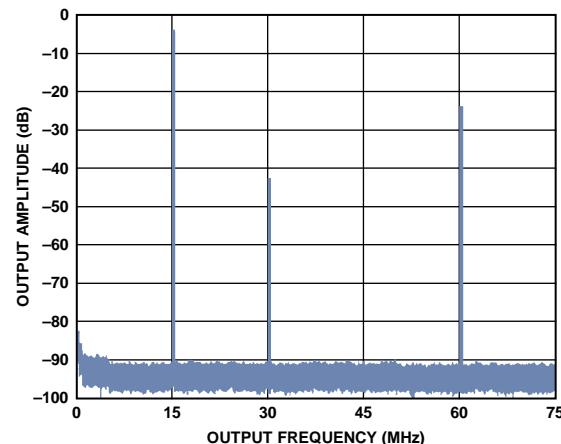

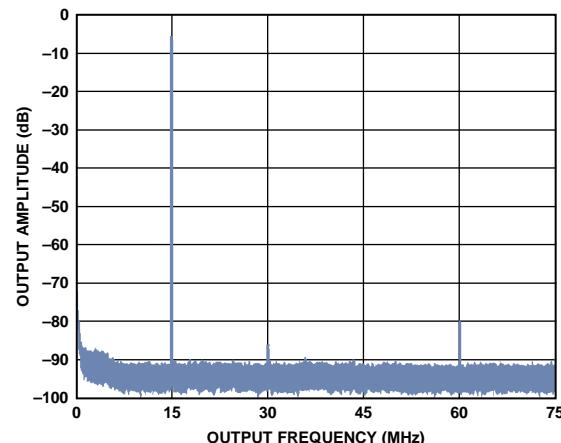

回路の性能をチェックするため、AD9834を15MHzの出力周波数に設定し、75MSPSのクロックでDDS出力のスペクトルを測定しました。フィルタを通していない出力とフィルタを通した出力をそれぞれ図6と図7に示します。

図6のフィルタを通していないスペクトルに生じる不要なイメージが、図7では大幅に低減されています。60MHzでの最も大きなイメージ・スプリアスは、フィルタを通していない出力に比べて約52dB抑制されています。これは、60MHzでのフィルタの減衰量の実測値に相当します。

図6. 15MHzに設定したAD9834のIOUTで測定したフィルタを通していない出力

図7. 15MHzに設定したAD9834のIOUTBで測定したフィルタを通した出力

AD9834の600mVp-pの出力はフィルタによって約6dB減衰し、 $\sin x/x$ のロールオフによってさらに1dB減衰します。このため、50Ω負荷への出力は約268mVp-p (94.7mVrms)になります。これは0.179mW (-7.5dBm)に相当します。

DDSに対する再構成フィルタ設計の詳細については、[アプリケーション・ノート AN-837 「DDS-Based Clock Jitter Performance vs. DAC Reconstruction Filter Performance」](#)を参照してください。

この回路は、大きな面積のグランド・プレーンを持つ多層PCボード上に構築する必要があります。最大限の性能を得るために正しいレイアウト、グラウンドティング、デカップリング技術が必要です。(チュートリアル MT-031 「データコンバータのグランディングとAGND/DGNDの不可解さの解決」と、チュートリアル MT-101 「デカップリング技術」を参照してください。)

回路図、レイアウト、部品表などが完備された設計サポート・パッケージについては、<http://www.analog.com/CN0304-DesignSupport>を参照ください。

## バリエーション回路

DDS の代替デバイスは [AD9838](#) です。AD9838 はより低消費電力 (11mW) で AD9834 と同じ機能を持ちますが、16MHz の低いクロック・レートで動作します。

この回路ノートで使用したバッファは電流帰還アンプ AD8014 です。この代替デバイスは [ADA4860-1](#) です。ADA4860-1 は低価格、高速 (-3dB 帯域幅が 800MHz)、低消費電力 (5V 時に 22.5mW) の電流帰還型オペアンプですが、790V/μs の低いスルーレートで動作します。

バッファには電圧帰還 (VFB) アンプを使用することもできます。VFB アンプの利点はノイズが小さく、帰還部品の選択の自由度が大きくなることです。AD8057 は、帯域幅とスルーレートが一般的な電流帰還アンプと同じ値の電圧帰還アンプです。AD8057 は、-3dB 帯域幅が 325MHz、28MHz までのゲイン平坦度が 0.1dB、スルーレートが 1000V/μs のデバイスです。

もう 1 つの代替デバイスは [ADA4897-1](#) です。ADA4897-1 はユニティ・ゲインで安定動作をし、広帯域ノイズが小さく、レール to レール出力の高速電圧帰還アンプであり、10Hz での入力電圧ノイズが 2.4 nV/√Hz、2MHz でのスプリアスフリー・ダイナミック・レンジ (SFDR) が -80dBc のデバイスです。

バッファとして [ADA4851-1](#) を使用することもできます。ADA4851-1 は低価格、低消費電力、高速 (-3dB 帯域幅が 130MHz) のデバイスですが、スルーレートは 375V/μs とさらに低い値です。

## 回路の評価とテスト

### 必要な装置

- [EVAL-CN0304-SDZ](#) 評価ボード

- [EVAL-SDP-CB1Z](#) 評価ボード

- [AD9834](#) 評価用ソフトウェア

- Agilent E3631A トリプル出力 DC 電源または相当品

- Rohde and Schwarz FSUP50 信号源アナライザ

- Agilent E5061B ネットワーク・アナライザ (フィルタ応答の評価にのみ必要)

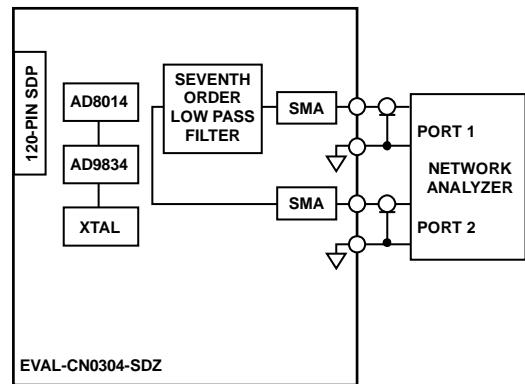

### フィルタ応答の測定

フィルタの周波数応答は図 8 に示すセットアップを使ったネットワーク・アナライザで測定しました。

12084-008

図 8. フィルタ応答測定用テスト・セットアップ

EVAL-CN0304-SDZ ボードを改造し、ネットワーク・アナライザからの信号をフィルタに入力しました。フィルタの出力はアナライザのもう 1 つのポートに接続しました。

### 出力波形の測定

DDS の出力波形は図 9 のセットアップを使って測定しました。

12084-009

図 9. DDS 出力に対するテスト・システムの機能図

EVAL-CN0304-SDZ の 5V 電源は SDP カードからの 5V USB 電圧から供給します。ジャンパの LK1 を B の位置、LK2 を B の位置にし、LK3 を取り外します。

### AD9834 の評価用ソフトウェア

([ftp://ftp.analog.com/pub/evalcd/AD9834/](http://ftp.analog.com/pub/evalcd/AD9834/)) を使って、DDS の出力周波数と振幅を設定しました。詳細については、[AD9834 評価用ボードのユーザー・ガイド UG-266](#) を参照してください。UG-266 に記載されているハードウェアには 7 次出力フィルタはありませんが、グラフィカル・ユーザー・インターフェースとソフトウェアの操作は EVAL-CN0304-SDZ のハードウェアと同一です。

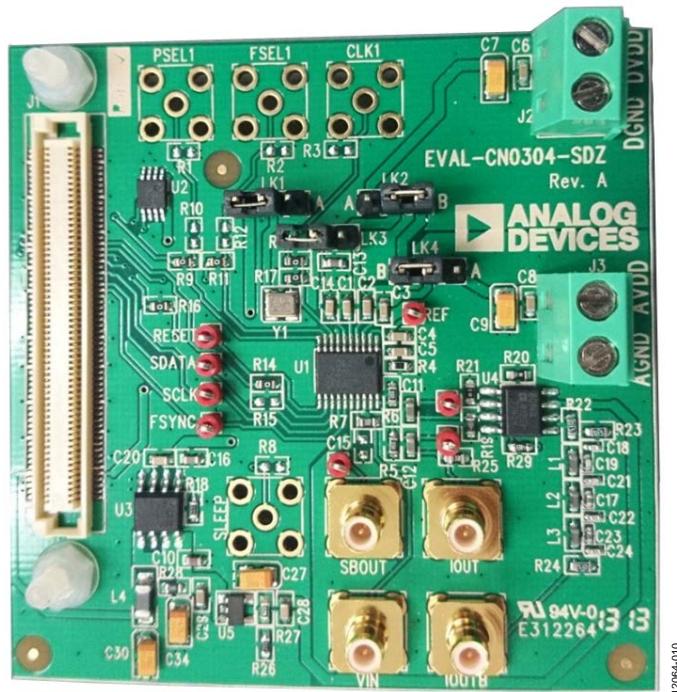

CN0304 のプリント回路ボードの写真を図 10 に示します。

図 10. EVAL-CN0304-SDZ ボードの写真

## さらに詳しい資料

CN0304 Design Support Package:

<http://www.analog.com/CN0304-DesignSupport>.

ADIsimDDS Design and Evaluation Tool.

UG-266 User Guide : Evaluating the AD9834 20 mW Power, 2.3 V to 5.5 V, 75 MHz Complete DDS. Analog Devices, Inc., 2011.

Kester, Walt. Chapter 3, Chapter 7, and Chapter 8, [The Data Conversion Handbook](#). Analog Devices, Inc., 2005.

MT-015 Tutorial : Basic DAC Architectures II: Binary DACs. Analog Devices, Inc.

MT-031 Tutorial : Grounding Data Converters and Solving the Mystery of AGND and DGND. Analog Devices, Inc.

MT-034 Tutorial : Current Feedback (CFB) Op Amps. Analog Devices, Inc.

[MT-085 Tutorial : Fundamentals of Direct Digital Synthesis \(DDS\)](#). Analog Devices, Inc.

[MT-101 Tutorial : Decoupling Techniques](#). Analog Devices, Inc.

[AN-837 Application Note : DDS-Based Clock Jitter Performance vs. DAC Reconstruction Filter Performance](#). Analog Devices, Inc.

[AN-1070 Application Note : Programming the AD9833/AD9834](#). Analog Devices, Inc.

## データシートと評価ボード

[AD9834 データシート](#)

[AD8014 データシート](#)

## 改訂履歴

4/14—Revision 0: 初版

「Circuits from the Lab／実用回路デザイン集」はアナログ・デバイセズ社製品専用に作られており、アナログ・デバイセズ社またはそのライセンスの供与者の知的所有物です。お客様は製品設計で「Circuits from the Lab／実用回路デザイン集」を使用することはできますが、その回路例を利用もしくは適用したことにより、特許権またはその他の知的所有権のもとの暗示的許可、またはその他の方法でのライセンスを許諾するものではありません。アナログ・デバイセズ社の提供する情報は正確でかつ信頼できるものであることを期しています。しかし、「Circuits from the Lab／実用回路デザイン集」は現状のまま、かつ商品性、非侵害性、特定目的との適合性の暗示的保証を含むがこれに限定されないいかなる種類の明示的、暗示的、法的な保証なしで供給されるものであり、アナログ・デバイセズ社はその利用に関して、あるいは利用によって生じる第三者の特許権もしくはその他の権利の侵害に関して一切の責任を負いません。アナログ・デバイセズ社はいつでも予告なく「Circuits from the Lab／実用回路デザイン集」を変更する権利を留保しますが、それを行う義務はありません。商標および登録商標は各社の所有に属します。