概要

設計リソース

評価用ボード

型番に"Z"が付いているものは、RoHS対応製品です。 本回路の評価には以下の評価用ボードが必要です。

- EVAL-CN0227-HSCZ High Performance, 16-Bit, 250 MSPS Wideband Receiver with Antialiasing Filter

- HSC-ADC-EVALCZ ($1134.20) High Speed Eval Control Board

デバイス・ドライバ

コンポーネントのデジタル・インターフェースとを介して通信するために使用されるCコードやFPGAコードなどのソフトウェアです。

機能と利点

- 16-Bit, 250MSPS 広帯域レシーバ

- アンチエイリアシング・フィルタ

- 72dB SNR @ 120MHz Input

- 82dB SFDR @ 120MHz Input

参考資料

-

UG-200: Evaluating the AD9467 16-Bit, 200 MSPS/250 MSPS ADC2011/07/08PDF1887 kB

-

MT-101: Decoupling Techniques2015/02/14PDF954 kB

-

MT-031: データ・コンバータのグラウンディングと、「AGND」および「DGND」に関する疑問の解消2009/03/20PDF144 kB

-

CN-0227: アンチエイリアシング・フィルタ付き、高性能、16 ビット、250 MSPS 広帯域レシーバ2012/06/13PDF262 kB

回路機能とその特長

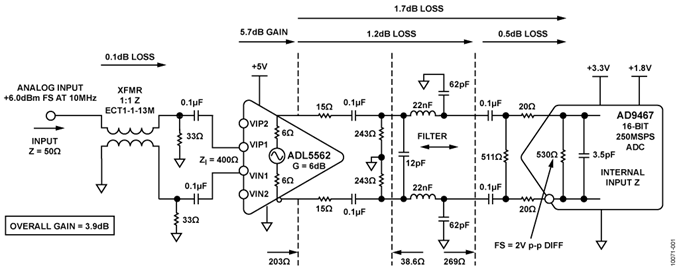

図1に示す回路は、超低ノイズ差動アンプ・ドライバADL5562と16ビット、250 MSPS A/DコンバータAD9467をベースにした広帯域レシーバのフロントエンドです。

3次バターワース・アンチエイリアシング・フィルタは、アンプとADCの性能およびインターフェースの要件に基づいて最適化されています。フィルタ・ネットワークと他の部品による損失はわずか1.8 dBです。

回路全体の帯域幅は152 MHz、通過帯域の平坦性は1 dBです。120 MHzのアナログ入力を使って測定したSNRは72.6 dBFS、SFDRは82.2 dBcです。

回路説明

この回路はシングルエンドの入力信号を受け入れ、それを帯域幅の広い(3 GHz) トランスM/A-COM ECT1-1-13M 1:1を使って差動に変換します。3.3 GHz差動アンプADL5562の差動入力インピーダンスは、6 dBのゲインで動作しているとき400 Ω、12 dBのゲインで動作しているとき200 Ωです。15.5 dBのゲインも選択可能です。

ADL5562はAD9467に最適なドライバです。ローパス・フィルタからADCに至るまで完全に差動のアーキテクチャなので、高周波同相除去性能が高く、2次歪み積を最小に抑えます。ADL5562は入力に応じて、6 dBまたは12 dBのゲインの設定が可能です。この回路では、フィルタ・ネットワークとトランスの挿入損失(約1.8 dB)を補償するためゲインを6 dBにしてあり、全体の信号ゲインは3.9 dBです。

6.0 dBmの入力信号はADCの入力に2 V p-pのフルスケール差動信号を生じます。

アンチエイリアシング・フィルタは、標準のフィルタ設計プログラムを使って設計した3次バターワース・フィルタです。バターワース・フィルタを選択した理由は、通過帯域内の応答がフラットであるためです。3次のフィルタはACノイズ帯域幅比が1.05になり、Nuhertz Technologies社のFilter FreeやQuite Universal Circuit Simulator (Qucs)の無償プログラムなど、いくつかの無償フィルタ・プログラムを使用して設計することができます。

最高の性能を得るため、ADL5562に200 Ωの差動負荷をかけます。15 Ωの直列抵抗はフィルタのキャパシタンスをアンプの出力から分離します。30 Ωの直列抵抗を追加することで、下流のインピーダンスと並列の243 Ω抵抗により、負荷インピーダンスは203 Ωになります。

ADCの入力と直列の20 Ω抵抗は、内部のスイッチング・トランジェントの影響がフィルタおよびアンプに及ばないようにします。

ADCと並列の511 Ω抵抗は、ADCの入力インピーダンスを下げて性能を安定させるのに役立ちます。

3次バターワース・フィルタは、38.6 Ωのソース・インピーダンス、269 Ωの負荷インピーダンス、および180 MHzの3 dB帯域幅で設計しました。プログラムで計算した値を図1に示します。選択したフィルタの受動部品の値はプログラムによって計算された値に最も近い標準値です。

ADC内部の3.5 pFの容量を2番目のシャント・コンデンサの値から差し引くと32.29 pFになります。図1に示すように、この回路では、このコンデンサはグラウンドに接続した2個の62 pFコンデンサを使って実現しました。これにより、同じフィルタ効果が得られ、いくらかのAC同相除去が行われます。

システム性能の測定結果を表1にまとめます。ここで、3 dB帯域幅は152 MHzです。ネットワーク全体の挿入損失は約2 dBです。応答帯域幅を図3に、SNRとSFDRの性能を図4に示します。

| Performance Specs @ 2 V p-p FS | Final Results |

| Cutoff Frequency (-3 dB) | 152 MHz |

| Pass-Band Flatness (6 MHz to 125 Mhz) | 1 dB |

| SNRF @ 120 MHz | 72.6 dBFS |

| SFDR @ 120 MHz | 82.2 dBc |

| H2/H3 @ 120 MHz | 86.6 dBc/82.2 dBc |

| Overall Gain @ 10 MHz | 3.9 dB |

| Input Drive @ 10 MHz | 6.0 dBm |

フィルタとインターフェースの設計手順

このセクションでは、フィルタ付きのアンプ/ADCインターフェースの一般的設計手法を説明します。最適な性能(帯域幅、SNR、SFDR)を実現するには、一般的な回路に対してアンプとADCによる設計上の一定の制約があります。

- 最適性能を得るには、アンプから見えるDC負荷をデータシートが推奨している適切な値にします。

- アンプと、フィルタによる負荷の間に適切な大きさの直列抵抗を使う必要があります。これは通過帯域内の不要なピーキングを防ぐためです。

- 外付け並列抵抗によってADCへの入力を減少させ、適切な直列抵抗を使ってADCをフィルタから分離します。この直列抵抗はピーキングを減らす効果もあります。

図5に示す一般化された回路はほとんどの高速差動アンプ/ADCインターフェースに適用できるので、ここでの説明の基礎として使います。この設計手法は、比較的高い入力インピーダンスの高速ADCと比較的低いインピーダンスの駆動源(アンプ)に活用することで、フィルタの挿入損失を小さく抑えるのに役立ちます。

基本的な設計手順は以下のとおりです。

- RTADCとRADCの並列抵抗が200 Ω~400 ΩになるようにADCの外付け終端抵抗RTADCを選択します。

- 経験やADCのデータシートの推奨値(標準5 Ω~36 Ω)に基づきRKBを選択します。

- 次式を使ってフィルタの負荷インピーダンスを計算します。

ZAAFL = RTADC || (RADC + 2RKB) - アンプの外付け直列抵抗RAを選択します。アンプの差動出力インピーダンスが100 Ω~200 Ωであれば、RAを10 Ω未満にします。アンプの出力インピーダンスが12 Ω以下であれば、RAを5 Ω~36 Ωにします。

- アンプから見た総負荷ZALが選択した特定の差動アンプに対して最適になるように、次式を使ってRTAMPを選択します。

ZAL = 2RA + (ZAAFL || 2RTAMP). - フィルタのソース抵抗を計算します。

ZAAFS = 2RTAMP || (ZO + 2RA). - フィルタ設計プログラムまたは表を使い、ソース・インピーダンスと負荷インピーダンス(ZAAFSとZAAFL)、フィルタのタイプ、帯域幅および次数を使ってフィルタを設計します。サンプリング・レートの1/2より約40%高い帯域幅を使って、DC~fs/2の周波数範囲が確実に平坦になるようにします。

- ADCの内部容量CADCをプログラムによって計算したシャント・コンデンサの最終値から差し引きます。プログラムから差動シャント・コンデンサの値CSHUNT2が得られます。最終的に得られた同相シャント容量値は次のとおりです。

CAAF2 = 2(CSHUNT2 − CADC).

これらの予備的計算を実行した後、以下の事項に関して回路を速やかに見直します。

- CAAF2がCADCより数倍大きくなるように、CAAF2の値を少なくとも10 pFにします。これにより、CADCのばらつきによってフィルタが受ける影響が小さく抑えられます。

- フィルタが大部分のフィルタの表および設計プログラムのリミット内に収まるように、ZAAFSに対するZAAFLの比が約7を超えないようにします。

- CAAF1の値を少なくとも5 pFにして、寄生容量と部品のばらつきの影響を小さく抑えます。

- インダクタLAAFは少なくとも数nHの適度な値にします。

1. CAAF2がCADCより数倍大きくなるように、CAAF2の値を少なくとも10 pFにします。これにより、CADCのばらつきによってフィルタが受ける影響が小さく抑えられます。

2. フィルタが大部分のフィルタの表および設計プログラムのリミット内に収まるように、ZAAFSに対するZAAFLの比が約7を超えないようにします。

3. CAAF1の値を少なくとも5 pFにして、寄生容量と部品のばらつきの影響を小さく抑えます。

4. インダクタLAAFは少なくとも数nHの適度な値にします。

フィルタ設計プログラムは、特に高次のフィルタの場合、複数の提案が提供されることがあります。選択が可能な最適な部品の値を用いる提案を常に選択する必要があります。また、最後の部分がシャント・コンデンサで終る構成を選択して、シャント・コンデンサをADCの入力容量と組み合わせることができるようにします。

回路の最適化手法とトレードオフ

このインターフェース回路のパラメータは相互に依存度が高いので、全ての主要な仕様(帯域幅、帯域の平坦度、SNR、SFDR、ゲイン)に対して回路を最適化することはほとんど不可能です。ただし、応答帯域幅内でしばしば生じるピーキングは、RAとRKBを変えることで小さく抑えることができます。

図6で、出力の直列抵抗RAの値を大きくするにつれ、通過帯域のピーキングが小さくなることに注意してください。ただし、この抵抗値が増加するにつれ信号が減衰するので、ADCのフルスケール入力範囲を満たすには、アンプがより大きな信号を駆動する必要があります。

RAの値もSNR性能に影響します。

RAを大きくすると帯域幅内のピーキングが小さくなりますが、ADCをフルスケールに駆動するには大きな信号レベルが必要なので、SNRがわずかに増加する傾向があります。

ADC入力のRKB直列抵抗は、ADC内部のサンプリング・コンデンサから注入される残留電荷によって生じる歪みが最小になるように選択します。また、この抵抗を大きくすると、帯域幅内のピーキングが小さくなる傾向があります。

ただし、RKBを大きくすると信号が大きく減衰するので、ADCの入力範囲を満たすには、アンプはより大きな信号を駆動する必要があります。

通過帯域の平坦性を最適化するもう1つの方法は、フィルタのシャント・コンデンサCAAF2をわずかに変えることです。

通常は、ADCの入力インピーダンスが200 Ω~400 ΩになるようにADC入力の終端抵抗RTADCを選択します。これを下げると、ADCの入力容量の影響が小さくなり、フィルタ回路が安定しますが、回路の挿入損失が増加します。また、値を大きくすると、ピーキングが小さくなります。

これらのトレードオフのバランスをとるのが難しいことがあります。この設計では各パラメータの重みづけを等しくしたので、全ての回路特性に関して、インターフェース性能の代表的な値を選択しました。設計によっては、システムの要件に従って異なる値を選択して、SFDR、SNR、入力駆動レベルを最適化することができます。

この設計のSFDR性能は2つの要因によって決まります。つまり図1に示すアンプとADCのインターフェースの部品の値、および内部レジスタによるAD9467内部のフロントエンド・バッファのバイアス電流の設定です。表1と図4に示す最終的に得られたSFDR性能の数値はAD9467のデータシートで説明されているSFDRの最適化に従って得られました。

この特定の設計で可能な別のトレードオフはADCのフルスケールの設定です。この設計で得られたデータの場合、ADCのフルスケール差動入力電圧を2 V p-pに設定しました。

これによってSFDRが最適化されます。フルスケール入力範囲を2.5 V p-pに変えると、SNRが約1.5 dB改善されますが、SFDR性能がわずかに低下します。データシートで説明されているように、入力範囲はAD9467の内部レジスタにロードした値によって設定されます。

この設計の信号はアンプ、その終端抵抗、およびADC入力の間の同相電圧を遮断するために0.1 μFのコンデンサによってAC結合されていることに注意してください。

同相電圧の詳細についてはAD9467のデータシートを参照してください。

受動部品とPCボードの寄生要素の検討

この回路をはじめ、いずれの高速回路でも、性能はPCBレイアウトに大きく依存します。PCBレイアウトに含まれる要素として、電源のバイパス、制御されたインピーダンス・ライン(必要時)、部品配置、信号配線、電源プレーンとグラウンド・プレーンなどがあります。

高速ADCとアンプのPCBレイアウトの詳細についてはチュートリアルの MT-031 と MT-101 を参照してください。

フィルタの受動部品には、寄生要素が小さい表面実装コンデンサ、インダクタ、抵抗を使用します。ここで選択したインダクタは、Coilcraftの0603CSシリーズです。フィルタには安定性と精度を考慮して5%、C0G、0402タイプの表面実装コンデンサを使用しています。

システムに関する詳細情報については(www.analog.com/CN0227-DesignSupport) を参照してください。

回路の評価とテスト

この回路は修正した回路ボード AD9467-250EBZ とFPGAベースのデータ・キャプチャ・ボード HSC-ADC-EVALCZ を使用します。これら2枚のボードは接続用高速コネクタを搭載しているので、短時間でセットアップして回路の性能を評価することができます。修正されたAD9467-250EBZボードにはこの回路ノートで説明した評価対象の回路が含まれており、データ・キャプチャ・ボードHSC-ADC-EVALCZはVisual Analog評価ソフトウェアやSPIコントローラ・ソフトウェアと組み合わせて使用し、ADCを適切に制御してデータをキャプチャします。AD9467-250EBZボードの回路図、部品表、レイアウトに関しては、User Guide UG-200を参照してください。 (www.analog.com/CN0227-DesignSupport) に付属しているreadme.txtファイルは、標準のAD9467-250EBZボードの修正箇所について説明しています。 Application Note AN-835 には、この回路ノートで説明したテストを実行するためのハードウェアとソフトウェアのセットアップ方法が詳述されています。