TNJ-021:減衰型構成アンプでのノイズ・レベルや位相余裕はどう考えるか

2016年8月1日公開

はじめに

異なる、でも似たような、ふたつのご質問をいただきました。「反転アンプで減衰型を構成した場合に、出力で得られるノイズ・レベルをどう考えるか?」、「差動アンプで減衰型を構成した場合に、得られる位相余裕をどう考えるか?」ということでした。

増幅構成とする場合は、「回路の信号利得に応じて周波数特性が低下していく」と想像できるとは思います。しかし「減衰構成」とした場合に、G = 1の回路より「出力ノイズ量は低くなる」とか、「周波数特性として、より高い周波数まで動作する」と考えられるでしょうか。基本的な回路動作として考えても、「いや、そんなはずは無い」と直感的に感じるものと思います。

また、このとき回路動作の安定性を決定づける「位相余裕」はどうなるかについても、これをどのように考えればよいかは、はたと行き詰ってしまうのではないでしょうか。

この技術ノートでは、ノイズ・レベルと位相余裕という二つの視点で、そのあたりを考えてみたいと思います。途中ではこれらの点と関連した話題として、非反転増幅と反転増幅の周波数特性についても考えてみます。

まずはノイズ・レベルのようすを実験でみてみる

まずはノイズ・レベルを比較評価してみるため、2つの実験回路を作ってみました(「実験」といってもシミュレーションですが)。図1は非反転アンプで、G = 1 + 1/10 = 1.1倍、図2は反転アンプで、G = -1/10 = -0.1倍です。このとき得られるノイズ量はどうなるでしょうか?これをアナログ・デバイセズのSPICEシミュレータADIsimPEでみていきましょう。なお抵抗R1, R2それぞれの大きさは、2回路ともどもで、同じになっています(これがミソ。抵抗からの熱ノイズが等しいということ)。

使用したOPアンプは、AD8671(オペアンプ、シングル、高精度、超ローノイズ、低入力バイアス電流)です。

【概要】

AD8671は超ローノイズ、きわめて低いオフセット電圧とドリフト、低入力バイアス電流、10MHzの帯域幅、低消費電力を特長とするシングル、デュアル、クワッドの高精度アンプです。出力は、100pFを超える容量性負荷でも安定に動作します。電源電流は、30Vでアンプ当たり3mA未満です。

信号利得は違うがノイズ・レベルは同じだ

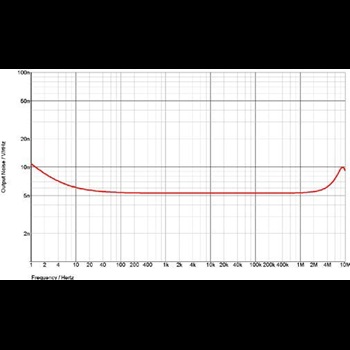

図1(非反転 G = 1.1)のシミュレーションの結果を図3に、図2(G = -0.1)の結果を図4に示します。図3の非反転 G = 1.1と、図4の反転 G = -0.1それぞれで、出力ノイズは同じになっています。なぜこのような結果になるのでしょうか?!詳しくは追って…。

と、そんな話をしていたら、知人からコメントがありました。「こういう時のためにノイズ・ゲインっていう考え方があるんですよね」「ポイントは重ね合わせの定理で考える事かな?答えを言っちゃってまずかったかな( ^^; )」。

図4. 反転アンプG = -1/10 = -0.1倍のノイズ・レベル

ノイズ・ゲインという考え方がある

図3と図4の結果が同じなのは、この知人の言うとおり「ノイズ・ゲイン」というものが関係しています。ノイズ・ゲインとは、入力換算ノイズが出力に現れる量、それこそノイズが増幅される率のことです。

図5は増幅回路のトポロジーごとに信号利得とノイズ・ゲインを示したものです。ここで「利得」と「ゲイン」と和洋折衷な表現ですが(利得 = ゲイン)、可読性を考えて、使い方を「信号利得」と「ノイズ・ゲイン」として分けています。

この図から分かるように、入力信号に対して得られる信号利得と、OPアンプの入力換算ノイズに対して得られるゲインは異なるものになります。

ノイズ・ゲインの考え方は回路を非反転増幅とみればよい

ノイズ・ゲインの考え方は、「すべての入力端子をグラウンドに落して、非反転増幅の構成として考えなおす」とすれば良いものです(図5に図示してあります。以降でひとつひとつ説明していきます)。

なぜこのように考えればよいかは、入力換算ノイズは(一般的に)非反転入力端子に加わる電圧源として(図5の赤丸を信号源と考えるように)モデル化することができるからです。

つまりこの電圧源をソースとして、帰還抵抗の構成でどのように増幅率が形成され、この電圧源が何倍の利得をもって出力に現れるか、その率がノイズ・ゲインとなります。

ノイズ・ゲインの考え方はノイズばかりではない

ノイズ・ゲインが使えるのは、出力端に現れるノイズ量を計算するのみではありません。オフセット電圧(入力換算オフセット電圧が出力に現れる大きさ)や、この技術ノートの以降で示していく回路の周波数特性(信号利得により変化する-3dB周波数帯域幅)の計算、これらにも広く活用することができます。

ノイズ・ゲインという考え方を詳しくみていく

それではノイズ・ゲインの考え方を、図5を使って詳しくみていきましょう。

さきに示したように、「ノイズ・ゲインは回路を非反転増幅と見ればよい」…考え方はただそれだけの話です。いろいろな書籍やアプリケーション・ノートでは、これに関して明快な説明がされていないものもあり、「ノイズ・ゲインっていったい何モノ?」と思う方も多いかもしれません。しかし「非反転増幅と見ればよいだけのこと」として分かってしまえば、実は簡単なことなのです。

非反転アンプは信号利得とノイズ・ゲインは同じ

図5の左は非反転アンプです。この信号ゲインGは教科書どおり

G = 1 + R2/R1 (1)

です。この回路のノイズ・ゲインを考えるには、信号入力端子(OPアンプの非反転入力端子)をグラウンドに落として、その非反転入力端子に信号源が(図中の赤丸のように)加わったものとして考えます。このときのノイズ・ゲインGNは、当然のごとく式(1)と一緒で、

GN = 1 + R2/R1 (2)

になります。これはさきの「ノイズ・ゲインは回路を非反転増幅と見ればよい」という考え方がそのまま、というわけですね。

反転アンプは信号利得+1がノイズ・ゲイン

図5の中央は反転アンプです。この信号ゲインGも教科書どおり

G = - R2/R1 (3)

です。この回路のノイズ・ゲインを考えるには、信号入力端子をグラウンドに落として、グラウンドにつながっている非反転入力端子側に信号源が(図中の赤丸のように)加わったものとして考えます。このときのノイズ・ゲインGNは、なんと、式(1)や式(2)と一緒で、

GN = 1 + R2/R1 (4)

になります。これも「ノイズ・ゲインは回路を非反転増幅と見ればよい」という考え方がそのままですね。

反転アンプで抵抗がよけいに付加されているとノイズ・ゲインは大きくなる

図5の右は、反転アンプですが、信号利得には影響を与えないR3という抵抗が付加されています。OPアンプの非反転入力端子はグラウンドにつながっていて、反転入力端子は仮想ショートなので、グラウンド。それを考えれば「どう考えてもR3は動作に何の影響も与えないのではないか?」と思うかもしれません。

たしかにこの回路の信号利得Gは

G = 1 + R2/R1 (5)

です。ではノイズ・ゲインGNを考えてみましょう。

ノイズ・ゲインは「回路を非反転増幅と見ればよい」という考え方です。つまり、信号入力端子をグラウンドに落として、グラウンドにつながっている非反転入力端子側に信号源が(図中の赤丸のように)加わったものとして考えます。こうするとなんと、R3が帰還抵抗の一部を構成していることが分かります。つまりノイズ・ゲインGNは

GN = 1 + R2/(R1//R3) (6)

となり、もともとR1だったところがR1, R3の並列抵抗となり、得られるノイズ・ゲインGNの大きさも、とても大きくなることが分かります。ここで「//」は抵抗の並列接続を意味しています。

もともと、図5の左・中央と右の回路の、OPアンプ自体の入力換算ノイズは同じなわけですから、この右の回路は(中央と信号利得は同じであるにもかかわらず)出力でのノイズが(オフセット電圧なども)大きく上昇してしまうという問題があるわけです。

これは「予期せずノイズ・ゲインが上昇してしまう」ことでもあります。

非反転・反転の2つの回路のノイズ・ゲインは全く同じ

図1、図2に示した、非反転・反転の2つの回路でのR1, R2の帰還構成は、「ノイズ・ゲインは回路を非反転増幅と見ればよい」という考え方からすると、同一の回路になっています。そのため両方のノイズ・ゲインは同じです。

また回路全体でのOPアンプ入力換算ノイズが両方とも同じ(抵抗値も同一であるため)なので、出力で得られるノイズは同じ量になっています。

結局これが図3、図4での結果として得られているだけなわけです。

入力換算SN比を考えるには

これまでの関係から、入力換算SN比を考えてみます。出力ノイズはこれまでの話のように入力換算ノイズに対してノイズ・ゲイン倍したものが出力に現れます。いっぽうで信号自体は信号利得倍したものが出力に現れます。これらをアンプ出力で(異なる利得として)考えれば、出力換算SN比を正しく求めることができるわけです。これがこのまま入力換算SN比となります。

いっぽうで入力換算ノイズと信号源レベルを用いてSN比を計算することはできません。それぞれ出力に現れる倍率(信号利得とノイズ・ゲイン)が異なっているからです。

減衰型構成反転アンプのノイズ・レベルを考える

それではいよいよ本題の減衰型構成反転アンプのノイズ・レベルを考えてみましょう。減衰型構成反転アンプは図5の中央の図でR1 > R2とすることで、入力レベルを減衰させたかたちで出力から取り出すことができます。このときの信号ゲインは式(3)のとおり

|G| = |R2/R1| < 1 (7)

です。減衰なので1より小さいわけですね。一方でノイズ・ゲインは式(4)のとおりなので、GN は1~ 2の間となります。

つまり減衰型構成反転アンプのノイズ・ゲインは、「ボルテージ・フォロアの基本回路で得られるノイズ・ゲインよりいくぶん大きくなる」という答えになることが分かります。

ノイズ・ゲインから回路の周波数特性が得られる

ここまで「ノイズ・ゲインは入力換算ノイズが出力端で得られる倍率である」と説明してきました。また同じく、入力換算オフセット電圧が出力に現れる倍率としても利用することができます。

同様に、実は、回路の動作周波数特性もノイズ・ゲインで考えることができます。

OPアンプにはGB積(Gain Bandwith Product)という数値が多くのデータシートに掲載されています。たとえばOP2177では1.3MHzと規定されています。ゲインG = 10倍のアンプを組めば、そのときの動作帯域BW[Hz]は

G × BW = GBP (8)

という式から、GBP = 1.3E6, G = 10として代入してみると、BW = 130kHzと計算できます。しかし、ここでの「動作帯域BW」というのは、何を基準にすればよいのでしょうか?これはこの技術ノートで「動作利得」として示してきた信号の増幅率ではなく、実は「ノイズ・ゲイン」なのです。

つまり「回路の周波数特性もノイズ・ゲインから得られる」ことになります。

シミュレーションしてみるとノイズ・ゲインが同じなら周波数特性も同じはず…?

それでは実際にADIsimPEで図1と図2の回路の周波数特性をシミュレーションしてみましょう。なおそれぞれ信号利得が異なり、反転アンプがG = -20dBになるので、非反転アンプも-20dBになるようにスケーリングして表示してみました。

シミュレーション結果を図6(非反転アンプ)と図7(反転アンプ)に示します。結果はたしかに近いようす(つまりノイズ・ゲインが同じであれば、周波数特性も同じ)が確認できます。しかし、ぴったり同じにはなっていませんね…。

あらためて図8にふたつのグラフを重ねあわせてみました。たしかにぴったり同じではありません…。減衰が-30dBを超えたあたり(基本の-20dBから30dBダウンのところ)で合わなくなってくるので、「ちょっとした誤差だよ…」といえる範囲かもしれませんが、これはなぜでしょう?

この違いはオープンループゲインが原因

周波数が高くなってきたあたりで、OPアンプとしてオープンループゲインA(f)が0dBに近くなったり、割り込んだりすると、OPアンプ自体の出力インピーダンスが上昇してきます。

OPアンプが本来もつ出力インピーダンスをROUTとすると、帰還により低下した実際の出力インピーダンスRFBは、以下で表せます。

RFB = ROUT/(1 + A(f)β) (9)

周波数fが高くなってくると、A(f)が低下します。そのため、最終的にはROUT = RFBとなり、OPアンプによってROUTは異なりますが、一般的に帰還抵抗に十分影響を与えてしまう大きさであるため、図6と図7がこのように差異が出てしまう原因となってしまうわけです。

そこで図9、図10のようにOPアンプ出力に理想バッファを接続し、ROUT = 0としてシミュレーションしてみました。図9では信号利得が-20dBになるようにスケーリングするバッファも接続されています。

図11に図9と図10のシミュレーション結果を重ねあわせたものを示します。図8と異なり、みごとに一致していることが分かりますね。このように「ノイズ・ゲインが同じであれば、周波数特性も同じ」になっていることが、ここまでの説明でお分かりいただけたものかと思います。

図11. 図9と図10の結果を重ねあわせてみた(青が非反転、赤が反転。赤のプロットが隠れている)

減衰型構成差動アンプの位相余裕を理解する

アナログ・デバイセズではファンネル・アンプ(Funnel Amp)とよばれる減衰型構成の差動アンプを用意しています。これは駆動すべきADCの動作電圧が信号源のスイングよりも小さい場合、信号源振幅を減衰させたうえで(またファンネル・アンプの電源電圧をADCの電源電圧に合わせることで)ADCの入力をオーバードライブしないようにできるアンプになっています。ファンネル・アンプの一例としてAD8475という製品を図12に示します。

図12. ファンネル・アンプの例:AD8475

このアンプは0.4x, 0.8xとして動作することが保証されているわけですが、とある日、「ADA4930-1、ADA4930-2やADA4937-1、ADA4937-2という差動アンプをADCドライバとして使ってみたい」というお話をうかがいました。そのときに、この技術ノートの最初に示したように「これらの差動アンプでAD8475のように減衰型を構成したい。なおG = 0.5としたい。そこで減衰型とした場合には、位相余裕をどう考えるか?」というご質問をいただいたわけなのです。

差動アンプを2個の反転アンプと考える

基本的な差動アンプの解析方法は、「アンプを上下半分で切って、それぞれが反転アンプになっていると、それが2個あるものとして動作しているのだ」と考えることです。

つまり回路動作を解析したいときは、図2と同じようにシングルエンドの反転構成として、さらに信号利得を減衰型にしたものとして考えれば良いことが分かります。

減衰型構成差動アンプの位相余裕はどう考える

それではひきつづき減衰型での位相余裕をどう考えるかを示してみたいと思います。

ここまで「回路の動作はノイズ・ゲインで決まる」と説明してきました。このことと上記の「2個の反転アンプ」ということを利用すれば、位相余裕は簡単に(正しく)求めることができます。

まずはノイズ・ゲインGNを考えるわけですが、G = 0.5の反転アンプであれば、式(4)を用いれば良いこととなり、GN = 1.5になることが分かります。

つづいてADA4930-1、ADA4930-2のデータシートをみてみます。Figure 31(図13として以下に示します)にオープンループゲインと位相の関係が示されています。GN = 1.5は3.5dBに相当します。そうするとオープンループゲインが3.5dBになったところが、ループが切れる周波数となり、ここの位相を読むことで位相余裕を得ることができます。

図13のGAINが3.5dBとなるあたりを拡大して図14に示してみます。図中の赤の横線が3.5dBのところとなり、それから青の矢印が2本見えますが、これが-135°程度のところを指していることが分かります。-180°は位相余裕がゼロになるところですから、このADA4930-1、ADA4930-2を用いたG = 0.5の減衰アンプにおける位相余裕は、大体45°となることが分かります。

つづいて同様な話しをADA4937-1、ADA4937-2でみてみましょう。こちらを図15に示します。これはデータシートのFigure 48から抜粋したものです。こちらも同じようにGN = 3.5dBの点から青い矢印を追っていくと、-135°程度となり、45°程度の位相余裕があることが分かります。

まとめ

OPアンプの回路動作は「ノイズ・ゲインが支配する」と言い切ってもいいかもしれません。ノイズ・ゲインは信号利得と違うことを理解し、これで出力換算ノイズ量、周波数特性、位相余裕を知ることができます。

著者について

デジタル回路(FPGAやASIC)からアナログ、高周波回路まで多...