ADuM3150

PRODUCTION3.75 kV, 6-Channel, SPIsolator Digital Isolator for SPI with Delay Clock

- Part Models

- 4

- 1ku List Price

- Starting From $4.39

Overview

- Supports up to 40 MHz SPI clock speed in delay clock mode

- Supports up to 17 MHz SPI clock speed in 4-wire mode

- 4 high speed, low propagation delay, SPI signal isolation channels

- 2 data channels at 250 kbps

- Delayed compensation clock line

- 20-lead SSOP with 5.1 mm creepage

- High temperature operation: 125°C

- High common-mode transient immunity: >25 kV/μs

- Safety and regulatory approvals

- UL 1577

- VISO = 3750 V rms for 1 minute

- IEC/EN/CSA 62368-1

- DIN EN IEC 60747-17 (VDE 0884-17)

- VIORM = 565 V peak

- UL 1577

The ADuM3150 is a 6-channel SPIsolator™ digital isolator optimized for isolated serial peripheral interfaces (SPIs). Based on the Analog Devices, Inc., iCoupler® chip scale transformer technology, the low propagation delay in the CLK, MO/SI, MI/SO, and SS SPI bus signals supports SPI clock rates of up to 17 MHz. These channels operate with 14 ns propagation delay and 1 ns jitter to optimize timing for SPI.

The ADuM3150 isolator also provides two additional independent low data rate isolation channels, one channel in each direction. Data in the slow channels is sampled and serialized for a 250 kbps data rate with 2.5 μs of jitter.

The ADuM3150 supports a delay clock output on the main side of the device. This output can be used with an additional clocked port on the main to support 40 MHz clock performance. See the Delay Clock section for more information.

Applications

- Industrial programmable logic controllers (PLC)

- Sensor isolation

Documentation

Data Sheet 1

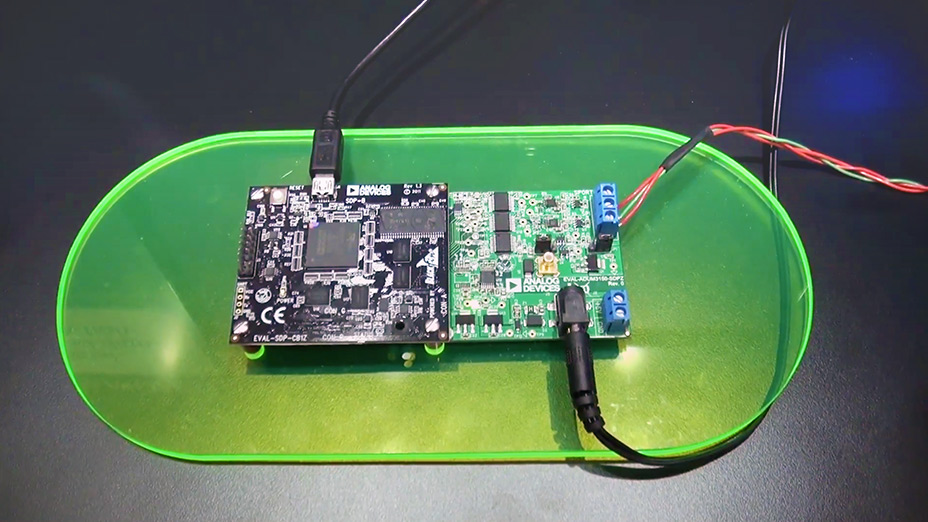

User Guide 1

Technical Articles 2

Safety and Regulatory Compliance 1

Video 3

Safety and Regulatory Compliance 1

Circuit Note 1

Webcast 2

ADI has always placed the highest emphasis on delivering products that meet the maximum levels of quality and reliability. We achieve this by incorporating quality and reliability checks in every scope of product and process design, and in the manufacturing process as well. "Zero defects" for shipped products is always our goal. View our quality and reliability program and certifications for more information.

| Part Model | Pin/Package Drawing | Documentation | CAD Symbols, Footprints, and 3D Models |

|---|---|---|---|

| ADUM3150ARSZ | 20-Lead SSOP | ||

| ADUM3150ARSZ-RL7 | 20-Lead SSOP | ||

| ADUM3150BRSZ | 20-Lead SSOP | ||

| ADUM3150BRSZ-RL7 | 20-Lead SSOP |

| Part Models | Product Lifecycle | PCN |

|---|---|---|

|

Feb 27, 2015 - 15_0031 ADuM315x Data Sheet Changes |

||

| ADUM3150ARSZ | PRODUCTION | |

| ADUM3150ARSZ-RL7 | PRODUCTION | |

| ADUM3150BRSZ | PRODUCTION | |

| ADUM3150BRSZ-RL7 | PRODUCTION | |

This is the most up-to-date revision of the Data Sheet.