AD4630-24

RECOMMENDED FOR NEW DESIGNS24-Bit, 2 MSPS Dual Channel SAR ADC

- Part Models

- 2

- 1ku List Price

- Starting From $38.09

Overview

- High performance

- Throughput: 2 MSPS (AD4630-24) or 500 kSPS (AD4632-24) per channel maximum

- INL: ±0.9 ppm maximum from −40°C to +125°C

- SNR: 105.7 dB typical

- THD: −127 dB typical

- NSD: −166 dBFS/Hz typical

- Low power

- 15 mW per channel at 2 MSPS

- 5 mW per channel at 500 kSPS

- 1.5 mW per channel at 10 kSPS

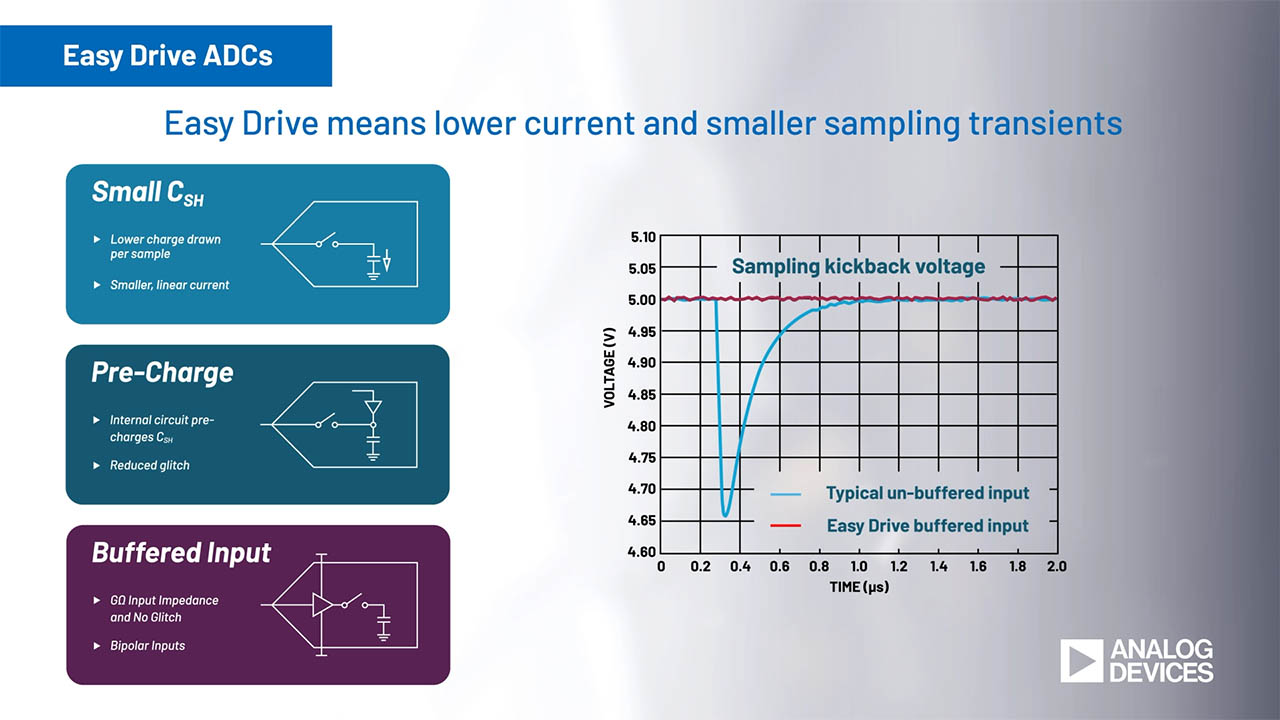

- Easy Drive features reduce system complexity

- Low 0.6 μA input current for dc inputs at 2 MSPS

- Wide input common-mode range: −(1/128) × VREF to +(129/128) × VREF

- Flexible external reference voltage range: 4.096 V to 5 V

- Accurate integrated reference buffer with 2 μF bypass capacitor

- Programmable block averaging filter with up to 216 decimation

- Extended sample resolution to 30 bits

- Overrange and synchronization bits

- Flexi-SPI digital interface

- 1, 2, or 4 SDO lanes per channel allows slower SCK

- Echo clock mode simplifies use of digital isolator

- Compatible with 1.2 V to 1.8 V logic

- 7 mm × 7 mm 64-Ball CSP_BGA package with internal supply and reference capacitors to help reduce system footprint

The AD4630-24/AD4632-24 are two-channel, simultaneous sampling, Easy Drive™, 2 MSPS or 500 kSPS successive approximation register (SAR) analog-to-digital converters (ADCs). With a guaranteed maximum ±0.9 ppm INL and no missing codes at 24 bits, the AD4630-24/AD4632-24 achieve unparalleled precision from −40°C to +125°C. Figure 1 in the data sheet shows the functional architecture of the AD4630-24/AD4632-24.

A low drift, internal precision reference buffer eases voltage reference sharing with other system circuitry. The AD4630-24/ AD4632-24 offer a typical dynamic range of 106 dB when using a 5 V reference. The low noise floor enables signal chains requiring less gain and lower power. A block averaging filter with programmable decimation ratio can increase dynamic range up to 153 dB. The wide differential input and common-mode ranges allow inputs to use the full voltage reference (±VREF) range without saturating, simplifying signal conditioning requirements and system calibration. The improved settling of the Easy Drive analog inputs broadens the selection of analog front-end components compatible with the AD4630-24/AD4632-24. Both single-ended and differential signals are supported.

The versatile Flexi-SPI serial peripheral interface (SPI) eases host processor and ADC integration. A wide data clocking window, multiple SDO lanes, and optional dual data rate (DDR) data clocking can reduce the serial clock to 10 MHz while operating at a sample rate of 2 MSPS or 500 kSPS. Echo clock mode and ADC host clock mode relax the timing requirements and simplify the use of digital isolators.

The 64-ball chip scale package ball grid array (CSP_BGA) of the AD4630-24/AD4632-24 integrates all critical power supply and reference bypass capacitors, reducing the footprint and system component count, and lessening sensitivity to board layout.

APPLICATIONS

- Automatic test equipment

- Digital control loops

- Medical instrumentation

- Seismology

- Semiconductor manufacturing

- Scientific instrumentation

Documentation

Data Sheet 1

User Guide 2

Technical Articles 2

Video 4

Device Drivers 2

Webcast 2

ADI has always placed the highest emphasis on delivering products that meet the maximum levels of quality and reliability. We achieve this by incorporating quality and reliability checks in every scope of product and process design, and in the manufacturing process as well. "Zero defects" for shipped products is always our goal. View our quality and reliability program and certifications for more information.

| Part Model | Pin/Package Drawing | Documentation | CAD Symbols, Footprints, and 3D Models |

|---|---|---|---|

| AD4630-24BBCZ | 64-Lead BGA (7 mm x 7 mm x 1.72 mm) | ||

| AD4630-24BBCZ-RL | 64-Lead BGA (7 mm x 7 mm x 1.72 mm) |

This is the most up-to-date revision of the Data Sheet.

Software Resources

Device Drivers 2

FPGA/HDL 1

Code Examples 1

Evaluation Software 2

Precision Toolbox for MATLAB

The Precision Toolbox is an evaluation software, made available in MATLAB, that allows configuring and capturing data with ADI’s precision data converters. To get started evaluating with the Precision Toolbox:

Step 1: Setup the evaluation hardware as described in the hardware setup guide.

Step 2: Install the Precision Toolbox and its dependencies. Refer to the Precision Toolbox wiki.

AD4630-24 Evaluation Software

Can't find the software or driver you need?

Hardware Ecosystem

-

High DC Precision Signal Chain -

High DC Precision Signal Chain, Lower Power

| Parts | Product Life Cycle | Description |

|---|---|---|

| Analog to Digital Converters (ADCs) 1 | ||

| AD4020 | RECOMMENDED FOR NEW DESIGNS | 20-Bit, 1.8 MSPS/1 MSPS/500 kSPS, Easy Drive, Differential SAR ADCs |

| Instrumentation Amplifiers 1 | ||

| LTC6373 | RECOMMENDED FOR NEW DESIGNS | 36V Fully-Differential Programmable-Gain Instrumentation Amplifier with 25pA Input Bias Current |

Tools & Simulations

LTspice 2

- LTC6373/LTC6655/ADG5421F Demo Circuit - Low Latency Programmable Gain Measurement for AD4630-24

- AD4630-24 - Precision A/D Converters

Models for the following parts are available in LTspice:

- AD4630-16

- AD4630-24

Precision ADC Driver Tool

The Precision ADC Driver Tool is a web application that simulates the performance of precision ADC and driver combinations. Potential issues with driver selection, kickback settling, and distortion are flagged, and design tradeoffs can be quickly evaluated. Simulations and calculations include system noise, distortion, and settling of the ADC input

Open ToolIBIS Model 1

Signal Chain Designer

Signal Chain Designer is a web-based tool designed to create and simulate complex precision signal chains. See your circuit’s performance before you commit to your PCB: transfer function, noise, power consumption, input range, and DC error. Quickly experiment with different parts and architectures. Signal chains can be exported to LTspice for further analysis.

Open ToolADI Circuit Explorer™

ADI Circuit Explorer™ uses AI to interpret natural language prompts and search a database of validated analog circuit designs, helping you quickly find the best match for your needs.

Open ToolLTspice® is a powerful, fast and free simulation software, schematic capture and waveform viewer with enhancements and models for improving the simulation of analog circuits.

Evaluation Kits

Latest Discussions

No discussions on AD4630-24 yet. Have something to say?

Start a Discussion on EngineerZone®